- 您现在的位置:买卖IC网 > Datasheet目录43 > MAX5952CUAX+ (Maxim Integrated)IC PSE CNTRLR FOR POE 36-SSOP Datasheet资料下载

参数资料

| 型号: | MAX5952CUAX+ |

| 厂商: | Maxim Integrated |

| 文件页数: | 43/50页 |

| 文件大小: | 1006K |

| 描述: | IC PSE CNTRLR FOR POE 36-SSOP |

| 产品培训模块: | Lead (SnPb) Finish for COTS Obsolescence Mitigation Program |

| 标准包装: | 30 |

| 类型: | 以太网供电控制器(PoE) |

| 应用: | 远程外设(工业控制,相机,数据访问) |

| 内部开关: | 无 |

| 工作温度: | 0°C ~ 85°C |

| 安装类型: | 表面贴装 |

| 封装/外壳: | 36-BSOP(0.295",7.50mm 宽) |

| 供应商设备封装: | 36-SSOP |

| 包装: | 管件 |

第1页第2页第3页第4页第5页第6页第7页第8页第9页第10页第11页第12页第13页第14页第15页第16页第17页第18页第19页第20页第21页第22页第23页第24页第25页第26页第27页第28页第29页第30页第31页第32页第33页第34页第35页第36页第37页第38页第39页第40页第41页第42页当前第43页第44页第45页第46页第47页第48页第49页第50页

High-Power, Quad, PSE Controller

for Power-Over-Ethernet

______________________________________________________________________________________ 43

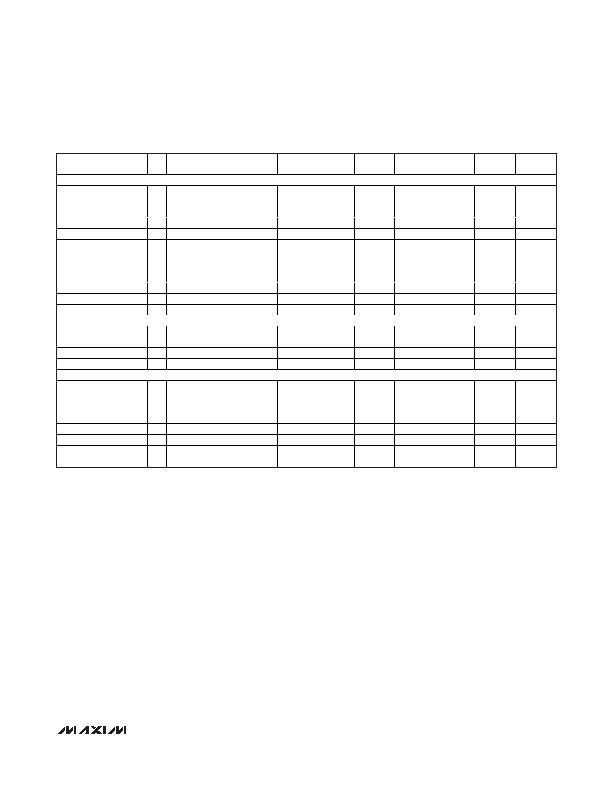

ADDR

REGISTER NAME

R/W PORT

BIT 7

BIT 6

BIT 5

BIT 4

BIT 3

BIT 2

BIT 1

BIT 0

RESET

STATE

MAXIM RESERVED

20H

Reserved

G

Reserved

Reserved

Reserved

Reserved

Reserved

Reserved

Reserved

Reserved

21H

Reserved

G

Reserved

Reserved

Reserved

Reserved

Reserved

Reserved

Reserved

Reserved

22H

Reserved

G

Reserved

Reserved

Reserved

Reserved

Reserved

Reserved

Reserved

Reserved

23H

Program 1

R/W

4321

Reserved

Reserved

CLC_EN

DET_BY

OSCF_RS

AC_TH[2]

AC_TH[1]

AC_TH[0]

0000,0000

24h

High Power Mode

R/W

G

Reserved

Reserved

Reserved

Reserved

Reserved

0000,0000

25h

Reserved

G

Reserved

Reserved

Reserved

Reserved

Reserved

Reserved

Reserved

Reserved

0000,0000

26h

Reserved

G

Reserved

Reserved

Reserved

Reserved

Reserved

Reserved

Reserved

Reserved

0000,0000

27H

Reserved

G

Reserved

Reserved

Reserved

Reserved

Reserved

Reserved

Reserved

Reserved

28H

Reserved

G

Reserved

Reserved

Reserved

Reserved

Reserved

Reserved

Reserved

Reserved

29H

Misc Config 2

R/W

1234

Reserved

Reserved

Reserved

Reserved

Reserved

Reserved

IVEE[1]

IVEE[0]

0000,0000

2AH

ICUT Register 1

R/W

21

Reserved

ICUT2[2]

ICUT2[1]

ICUT2[0]

Reserved

ICUT1[2]

ICUT1[1]

ICUT1[0]

0000,0000

2BH

ICUT Register 2

R/W

43

Reserved

ICUT4[2]

ICUT4[1]

ICUT4[0]

Reserved

ICUT3[2]

ICUT3[1]

ICUT[30]

0000,0000

CLASSIFICATION REGISTERS

2CH

Port 1 Class

RO

1

Reserved

Reserved

0000,0000

2DH

Port 2 Class

RO

2

Reserved

Reserved

0000,0000

2EH

Port 3 Class

RO

3

Reserved

Reserved

0000,0000

2FH

Port 4 Class

RO

4

Reserved

Reserved

0000,0000

CURRENT REGISTER

30H

Current Port 1 (MSB)

RO

1

IPD1[8]

IPD1[7]

IPD1[6]

IPD1[5]

IPD1[4]

IPD1[3]

IPD1[2]

IPD1[1]

0000,0000

31H

Current Port 1 (LSB)

RO

1

Reserved

Reserved

Reserved

Reserved

Reserved

Reserved

Reserved

IPD1[0]

0000,0000

32H

Current Port 2 (MSB)

RO

2

IPD2[8]

IPD2[7]

IPD2[6]

IPD2[5]

IPD2[4]

IPD2[3]

IPD2[2]

IPD2[1]

0000,0000

33H

Current Port 2 (LSB)

RO

2

Reserved

Reserved

Reserved

Reserved

Reserved

Reserved

Reserved

IPD2[0]

0000,0000

34H

Current Port 3 (MSB)

RO

3

IPD3[8]

IPD3[7]

IPD3[6]

IPD3[5]

IPD3[4]

IPD3[3]

IPD3[2]

IPD3[1]

0000,0000

35H

Current Port 3 (LSB)

RO

3

Reserved

Reserved

Reserved

Reserved

Reserved

Reserved

Reserved

IPD3[0]

0000,0000

36H

Current Port 4 (MSB)

RO

4

IPD4[8]

IPD4[7]

IPD4[6]

IPD4[5]

IPD4[4]

IPD4[3]

IPD4[2]

IPD4[1]

0000,0000

37H

Current Port 4 (LSB)

RO

4

Reserved

Reserved

Reserved

Reserved

Reserved

Reserved

Reserved

IPD4[0]

0000,0000

Table 37. Register Summary (continued)

*UV and UVLO bits of V

EE

and V

DD

asserted depends on the order V

EE

and V

DD

supplies are brought up.

A = AUTO pin state before reset.

M = MIDSPAN state before reset.

A3...0 = ADDRESS input states before reset.

相关PDF资料 |

PDF描述 |

|---|---|

| MAX5953DUTM+ | IC INTERFACE 802.3AF 48TQFN |

| MAX5954LETX+T | IC PCI EXP/HOT-PLUG CTRLR 36TQFN |

| MAX5955BEEE+ | IC DUAL HOT-SWAP CTRLR 16-QSOP |

| MAX5957AETN+T | IC TRPL PCI EXP/HOT-PLUG 56-TQFN |

| MAX5960AECS+T | IC CTRLR HOT-PLUG QD 80-TQFP |

相关代理商/技术参数 |

参数描述 |

|---|---|

| MAX5952CUAX+ | 功能描述:热插拔功率分布 Quad PSE Controller for POE RoHS:否 制造商:Texas Instruments 产品:Controllers & Switches 电流限制: 电源电压-最大:7 V 电源电压-最小:- 0.3 V 工作温度范围: 功率耗散: 安装风格:SMD/SMT 封装 / 箱体:MSOP-8 封装:Tube |

| MAX5952CUAX+T | 功能描述:热插拔功率分布 Quad PSE Controller for POE RoHS:否 制造商:Texas Instruments 产品:Controllers & Switches 电流限制: 电源电压-最大:7 V 电源电压-最小:- 0.3 V 工作温度范围: 功率耗散: 安装风格:SMD/SMT 封装 / 箱体:MSOP-8 封装:Tube |

| MAX5952DEAX+ | 制造商:Maxim Integrated Products 功能描述:- Rail/Tube |

| MAX5952DEAX+T | 制造商:Maxim Integrated Products 功能描述:HIGH-POWER QUAD PSE CONTROLLER FOR - Tape and Reel |

| MAX5952DUAX+ | 制造商:Maxim Integrated Products 功能描述:- Rail/Tube |

发布紧急采购,3分钟左右您将得到回复。