- 您现在的位置:买卖IC网 > PDF目录16779 > MAX9888EVKIT+ (Maxim Integrated Products)KIT EVALUATION FOR MAX9888 PDF资料下载

参数资料

| 型号: | MAX9888EVKIT+ |

| 厂商: | Maxim Integrated Products |

| 文件页数: | 6/115页 |

| 文件大小: | 0K |

| 描述: | KIT EVALUATION FOR MAX9888 |

| 产品培训模块: | Lead (SnPb) Finish for COTS Obsolescence Mitigation Program |

| 标准包装: | 1 |

| 系列: | DirectDrive®, FLEXSOUND™ |

| 相关产品: | MAX9888EWY+T-ND - IC CODEC AUDIO FLEXSOUND 63WLP |

第1页第2页第3页第4页第5页当前第6页第7页第8页第9页第10页第11页第12页第13页第14页第15页第16页第17页第18页第19页第20页第21页第22页第23页第24页第25页第26页第27页第28页第29页第30页第31页第32页第33页第34页第35页第36页第37页第38页第39页第40页第41页第42页第43页第44页第45页第46页第47页第48页第49页第50页第51页第52页第53页第54页第55页第56页第57页第58页第59页第60页第61页第62页第63页第64页第65页第66页第67页第68页第69页第70页第71页第72页第73页第74页第75页第76页第77页第78页第79页第80页第81页第82页第83页第84页第85页第86页第87页第88页第89页第90页第91页第92页第93页第94页第95页第96页第97页第98页第99页第100页第101页第102页第103页第104页第105页第106页第107页第108页第109页第110页第111页第112页第113页第114页第115页

Stereo Audio CODEC

with FlexSound Technology

MAX9888

103

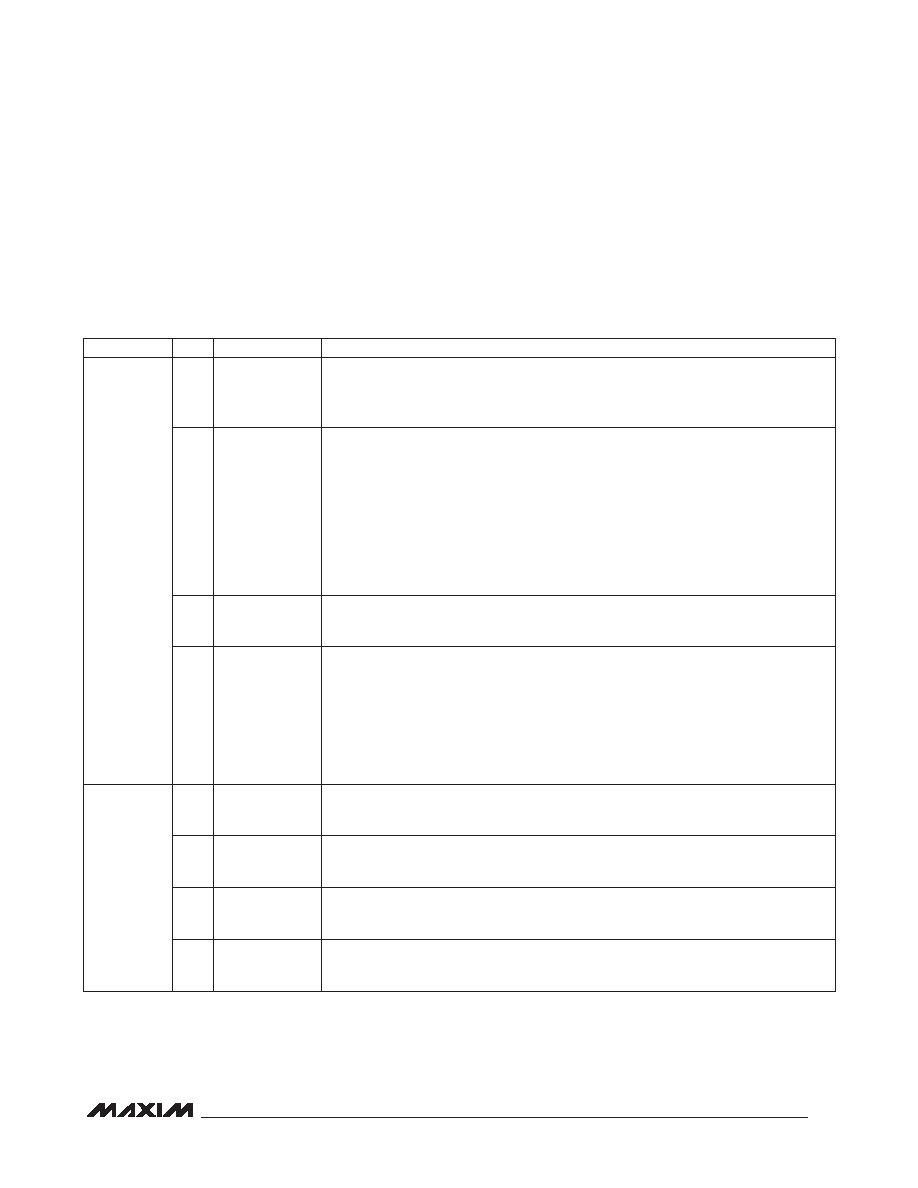

Table 37. Status and Interrupt Registers

Device Status

The IC uses register 0x00 and IRQ to report the status of

various device functions. The status register bits are set

when their respective events occur, and cleared upon

reading the register. Device status can be determined

either by poling register 0x00 or configuring the IRQ to

pull low when specific events occur. IRQ is an open-

drain output that requires a pullup resistor for proper

operation. Register 0x0F determines which bits in the

status register trigger IRQ to pull low.

REGISTER

BIT

NAME

DESCRIPTION

0x00

(Read Only)

7

CLD

Full Scale

0 = All digital signals are less than full scale.

1 = The DAC or ADC signal path has reached or exceeded full scale. This typically

indicates clipping.

6

SLD

Volume Slew Complete

SLD reports that any of the programmable-gain arrays or volume controllers has

completed slewing from a previous setting to a new programmed setting. If multiple

gain arrays or volume controllers are changed at the same time, the SLD flag is set

after the last volume slew completes. SLD also reports when the digital audio interface

soft-start or soft-stop process has completed. MCLK is required for proper SLD

operation.

0 = No volume slewing sequences have completed since the status register was last

read.

1 = Volume slewing complete.

5

ULK

Digital Audio Interface Unlocked

0 = Both digital audio interfaces are operating normally.

1 = Either digital audio interface is configured incorrectly or receiving invalid data.

1

JDET

Jack Configuration Change

JDET reports changes to any bit in the Jack Status register (0x02). Changes to the Jack

Status bits are debounced before setting JDET. The debounce period is programmable

using the JDEB bits. JDET is always set the first time JDETEN or SHDN is set the first

time power is applied to the IC. Read the status register following such an event to clear

JDET and allow for proper jack detection.

0 = No change in jack configuration.

1 = Jack configuration has changed.

0x0F

7

ICLD

Full-Scale Interrupt Enable

0 = Disabled

1 = Enabled

6

ISLD

Volume Slew Complete Interrupt Enable

0 = Disabled

1 = Enabled

5

IULK

Digital Audio Interface Unlocked Interrupt Enable

0 = Disabled

1 = Enabled

1

IJDET

Jack Configuration Change Interrupt Enable

0 = Disabled

1 = Enabled

相关PDF资料 |

PDF描述 |

|---|---|

| H3AAH-3418G | IDC CABLE - HSC34H/AE34G/HSC34H |

| EBM22DRAI | CONN EDGECARD 44POS R/A .156 SLD |

| RNF-100-1/8-GN-STK | HEAT SHRINK TUBING |

| RSC06DREF-S13 | CONN EDGECARD 12POS .100 EXTEND |

| GEC26DRXN-S734 | CONN EDGECARD 52POS DIP .100 SLD |

相关代理商/技术参数 |

参数描述 |

|---|---|

| MAX9888EVKIT+ | 功能描述:音频 IC 开发工具 MAX9888 Eval Kit RoHS:否 制造商:Texas Instruments 产品:Evaluation Kits 类型:Audio Amplifiers 工具用于评估:TAS5614L 工作电源电压:12 V to 38 V |

| MAX9888EWY+T | 功能描述:接口—CODEC Stereo Audio CODEC RoHS:否 制造商:Texas Instruments 类型: 分辨率: 转换速率:48 kSPs 接口类型:I2C ADC 数量:2 DAC 数量:4 工作电源电压:1.8 V, 2.1 V, 2.3 V to 5.5 V 最大工作温度:+ 85 C 安装风格:SMD/SMT 封装 / 箱体:DSBGA-81 封装:Reel |

| MAX9889EWO+T | 功能描述:接口—CODEC RoHS:否 制造商:Texas Instruments 类型: 分辨率: 转换速率:48 kSPs 接口类型:I2C ADC 数量:2 DAC 数量:4 工作电源电压:1.8 V, 2.1 V, 2.3 V to 5.5 V 最大工作温度:+ 85 C 安装风格:SMD/SMT 封装 / 箱体:DSBGA-81 封装:Reel |

| MAX988ESA | 功能描述:校验器 IC Single uPower Comparator RoHS:否 制造商:STMicroelectronics 产品: 比较器类型: 通道数量: 输出类型:Push-Pull 电源电压-最大:5.5 V 电源电压-最小:1.1 V 补偿电压(最大值):6 mV 电源电流(最大值):1350 nA 响应时间: 最大工作温度:+ 125 C 安装风格:SMD/SMT 封装 / 箱体:SC-70-5 封装:Reel |

| MAX988ESA+ | 功能描述:校验器 IC Single uPower Comparator RoHS:否 制造商:STMicroelectronics 产品: 比较器类型: 通道数量: 输出类型:Push-Pull 电源电压-最大:5.5 V 电源电压-最小:1.1 V 补偿电压(最大值):6 mV 电源电流(最大值):1350 nA 响应时间: 最大工作温度:+ 125 C 安装风格:SMD/SMT 封装 / 箱体:SC-70-5 封装:Reel |

发布紧急采购,3分钟左右您将得到回复。