- 您现在的位置:买卖IC网 > PDF目录16879 > MC35XS3500PNA (Freescale Semiconductor)IC SWITCH HIGHSIDE 24PQFN PDF资料下载

参数资料

| 型号: | MC35XS3500PNA |

| 厂商: | Freescale Semiconductor |

| 文件页数: | 29/45页 |

| 文件大小: | 0K |

| 描述: | IC SWITCH HIGHSIDE 24PQFN |

| 标准包装: | 168 |

| 类型: | 高端开关 |

| 输出数: | 5 |

| Rds(开): | * |

| 内部开关: | 是 |

| 电流限制: | 9A |

| 输入电压: | 7 V ~ 20 V |

| 工作温度: | -40°C ~ 125°C |

| 安装类型: | 表面贴装 |

| 封装/外壳: | 24-PowerQFN |

| 供应商设备封装: | 24-PQFN(12x12) |

| 包装: | 托盘 |

第1页第2页第3页第4页第5页第6页第7页第8页第9页第10页第11页第12页第13页第14页第15页第16页第17页第18页第19页第20页第21页第22页第23页第24页第25页第26页第27页第28页当前第29页第30页第31页第32页第33页第34页第35页第36页第37页第38页第39页第40页第41页第42页第43页第44页第45页

�� �

�

FUNCTIONAL� DEVICE� OPERATION�

�LOGIC� COMMANDS� AND� REGISTERS�

�ADDRESS� 00011� —� CONFIGURATION� CSNS�

�The� Configuration� Current� Sense� register� is� used�

�todisable� the� high� over-current� shutdown� phase� (OCHI1� and�

�OCHI2� dynamic� levels)� in� order� to� activate� immediately� the�

�current� sense� analog� feedback.�

�When� bit� D9� is� set� to� logic� [1],� the� current� sense�

�synchronization� signal� is� reported� on� FETOUT� output� pin.�

�When� the� corresponding� NO_OCHI� bit� is� set� to� logic� [1],�

�the� output� is� only� protected� with� OCLO� level.� And� the� current�

�sense� is� immediately� available� if� it� is� selected� through� SPI,� as�

�described� in� Figures 13� .� The� NO_OCHI� bit� per� output� is�

�automatically� reset� at� each� corresponding� ON� off� bit�

�transition� from� logic� [1]� to� [0]� and� in� case� of� over-temperature�

�or� over-current� fault.� All� NO_OCHI� bits� are� also� reset� in� case�

�of� under-voltage� fault� detection.�

�ADDRESS� 01001� —� Control� OUT1�

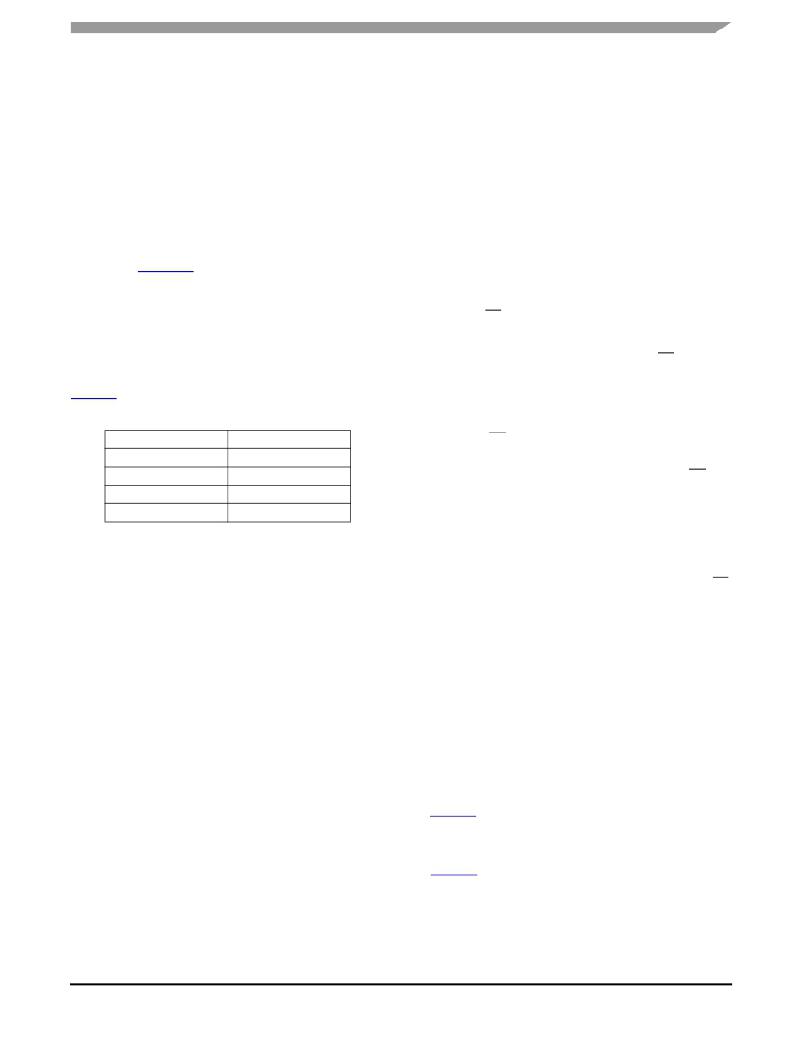

�Bits� D9� and� D8� control� the� switching� phases� as� shown� in�

��Table� 11.� Switching� Phases�

�ADDRESS� 01101� —� Control� OUT5�

�Same� description� as� OUT1.�

�ADDRESS� 01110� —� Control� External� Switch�

�Same� description� as� OUT1.�

�ADDRESS� 01111� —� Test� Mode�

�This� register� is� reserved� for� test� and� is� not� available� with�

�the� SPI� during� normal� operation.�

�Serial� Output� Communication� (Device� Status�

�Return� Data)�

�When� the� CS� pin� is� pulled� low,� the� output� register� is�

�loaded.� Meanwhile,� the� data� clocks� out� the� MSB� first� as� the�

�new� message� data� is� clocked� into� the� SI� pin.� The� first� 16� bits�

�of� data� clocking� out� of� the� SO,� and� following� a� CS� transition,�

�is� dependant� upon� the� previously� written� SPI� word� (SOA1�

�and� SOA0� defined� in� the� last� SPI� initialization� word).�

�Any� bits� clocked� out� of� the� SO� pin� after� the� first� 16� will� be�

�representative� of� the� initial� message� bits� clocked� into� the� SI�

�D9� :� D8�

�00�

�01�

�10�

�11�

�PWM� Phase�

�0°�

�90°�

�180°�

�270°�

�pin,� since� the� CS� pin� first� transitioned� to� a� logic� [0].� This�

�feature� is� useful� for� daisy� chaining� devices.�

�A� valid� message� length� is� determined� following� a� CS�

�transition� of� logic� [0]� to� logic� [1].� If� the� message� length� is�

�valid,� the� data� is� latched� into� the� appropriate� registers.� A� valid�

�message� length� is� a� multiple� of� 16� bits.� At� this� time,� the� SO�

�Bit� D7� at� logic� [1]� turns� ON� OUT1.� OUT1� is� turned� OFF�

�with� bit� D7� at� logic� [0].� This� register� allows� the� master� to�

�control� the� duty� cycle� and� the� switching� phases� of� OUT1.� The�

�duty� cycle� resolution� is� given� by� bits� D6� :� D0.�

�D7� =� 0,� D6� :� D0� =� XX� output� OFF.�

�D7� =� 1,� D6� :� D0� =� 00� output� ON� during� 1/128.�

�D7� =� 1,� D6� :� D0� =� 1� A� output� ON� during� 27/128� on� PWM�

�period.�

�D7� =� 1,� D6� :� D0� =� 7� F� output� continuous� ON� (no� PWM).�

�ADDRESS� 01010� —� Control� OUT2�

�Same� description� as� OUT1.�

�ADDRESS� 011111� —� Control� OUT3�

�Same� description� as� OUT1.�

�ADDRESS� 01100� —� Control� OUT4�

�Same� description� as� OUT1.�

�pin� is� tri-stated� and� the� fault� status� register� is� now� able� to�

�accept� new� fault� status� information.�

�The� output� status� register� correctly� reflects� the� status� of�

�the� Initialization-selected� register� data� at� the� time� that� the� CS�

�is� pulled� to� a� logic� [0]� during� SPI� communication� and� /� or� for�

�the� period� of� time� since� the� last� valid� SPI� communication,�

�with� the� following� exceptions:�

�?� The� previous� SPI� communication� was� determined� to� be�

�invalid.� In� this� case,� the� status� will� be� reported� as�

�though� the� invalid� SPI� communication� never� occurred.�

�?� Battery� transients� below� 6.0� V,� resulting� in� an� under-�

�voltage� shutdown� of� the� outputs,� may� result� in� incorrect�

�data� loaded� into� the� SPI� register,� except� the� UVF� fault�

�reporting� (OD13).�

�Serial� Output� Bit� Assignment�

�The� contents� of� bits� OD15� :� OD0� depend� on� bits� D1:� D0�

�from� the� most� recent� initialization� command� SOA[1:0]� (refer�

�to� Table� 12� ),� as� explained� in� the� paragraphs� that� follow.�

�The� register� bits� are� reset� by� a� read� operation� and� also� if�

�the� fault� is� removed.�

�Table 12� summarizes� the� SO� register� content.� Bit� OD10�

�reflects� Normal� mode� (NM).�

�35XS3500�

�Analog� Integrated� Circuit� Device� Data� ?�

�Freescale� Semiconductor�

�29�

�相关PDF资料 |

PDF描述 |

|---|---|

| GCC25DCMD-S288 | CONN EDGECARD 50POS .100 EXTEND |

| 342A124-4/42-0 | BOOT MOLDED |

| TCMD-17-D-02.00-01 | CABLE ASSEM 2MM 34POS M-M 2" |

| MC10XS3535PNAR2 | IC SWITCH HIGHSIDE 24PQFN |

| EBC31DCSN-S288 | CONN EDGECARD 62POS .100 EXTEND |

相关代理商/技术参数 |

参数描述 |

|---|---|

| MC35XS3500PNAR2 | 功能描述:功率驱动器IC 5 OUTPUT ESWITCH RoHS:否 制造商:Micrel 产品:MOSFET Gate Drivers 类型:Low Cost High or Low Side MOSFET Driver 上升时间: 下降时间: 电源电压-最大:30 V 电源电压-最小:2.75 V 电源电流: 最大功率耗散: 最大工作温度:+ 85 C 安装风格:SMD/SMT 封装 / 箱体:SOIC-8 封装:Tube |

| MC36089 | 制造商:SPC Multicomp 功能描述:ESD OPEN BIN BOX; ESD Storage Type:Bin; External Depth - Imperial:24.75"; External Depth - Metric:628.65mm; External Height - Imperial:4.5"; External Height - Metric:114.3mm; External Width - Imperial:4.25"; External Depth:24-3/4" ;RoHS Compliant: NA |

| MC36090 | 制造商:SPC Multicomp 功能描述:ESD OPEN BIN BOX; ESD Storage Type:Bin; External Depth - Imperial:24.75"; External Depth - Metric:628.65mm; External Height - Imperial:4.5"; External Height - Metric:114.3mm; External Width - Imperial:2.25"; External Depth:24-3/4" ;RoHS Compliant: NA |

| MC36091 | 制造商:SPC Multicomp 功能描述:ESD OPEN BIN BOX; ESD Storage Type:Bin; External Depth - Imperial:18"; External Depth - Metric:457.2mm; External Height - Imperial:4.5"; External Height - Metric:114.3mm; External Width - Imperial:4"; External Width - Metric:101.6mm ;RoHS Compliant: NA |

| MC36092 | 制造商:SPC Multicomp 功能描述:ESD OPEN BIN BOX; ESD Storage Type:Bin; External Depth - Imperial:18"; External Depth - Metric:457.2mm; External Height - Imperial:4.5"; External Height - Metric:114.3mm; External Width - Imperial:2"; External Width - Metric:50.8mm ;RoHS Compliant: NA |

发布紧急采购,3分钟左右您将得到回复。