- 您现在的位置:买卖IC网 > PDF目录80461 > MC8610TPX1066JZ (FREESCALE SEMICONDUCTOR INC) MICROPROCESSOR, PBGA783 PDF资料下载

参数资料

| 型号: | MC8610TPX1066JZ |

| 厂商: | FREESCALE SEMICONDUCTOR INC |

| 元件分类: | 微控制器/微处理器 |

| 英文描述: | MICROPROCESSOR, PBGA783 |

| 封装: | 29 X 29 MM, PLASTIC, FCBGA-783 |

| 文件页数: | 49/96页 |

| 文件大小: | 1237K |

| 代理商: | MC8610TPX1066JZ |

第1页第2页第3页第4页第5页第6页第7页第8页第9页第10页第11页第12页第13页第14页第15页第16页第17页第18页第19页第20页第21页第22页第23页第24页第25页第26页第27页第28页第29页第30页第31页第32页第33页第34页第35页第36页第37页第38页第39页第40页第41页第42页第43页第44页第45页第46页第47页第48页当前第49页第50页第51页第52页第53页第54页第55页第56页第57页第58页第59页第60页第61页第62页第63页第64页第65页第66页第67页第68页第69页第70页第71页第72页第73页第74页第75页第76页第77页第78页第79页第80页第81页第82页第83页第84页第85页第86页第87页第88页第89页第90页第91页第92页第93页第94页第95页第96页

Electrical Characteristics

MPC8610 Integrated Host Processor Hardware Specifications, Rev. 2

Freescale Semiconductor

53

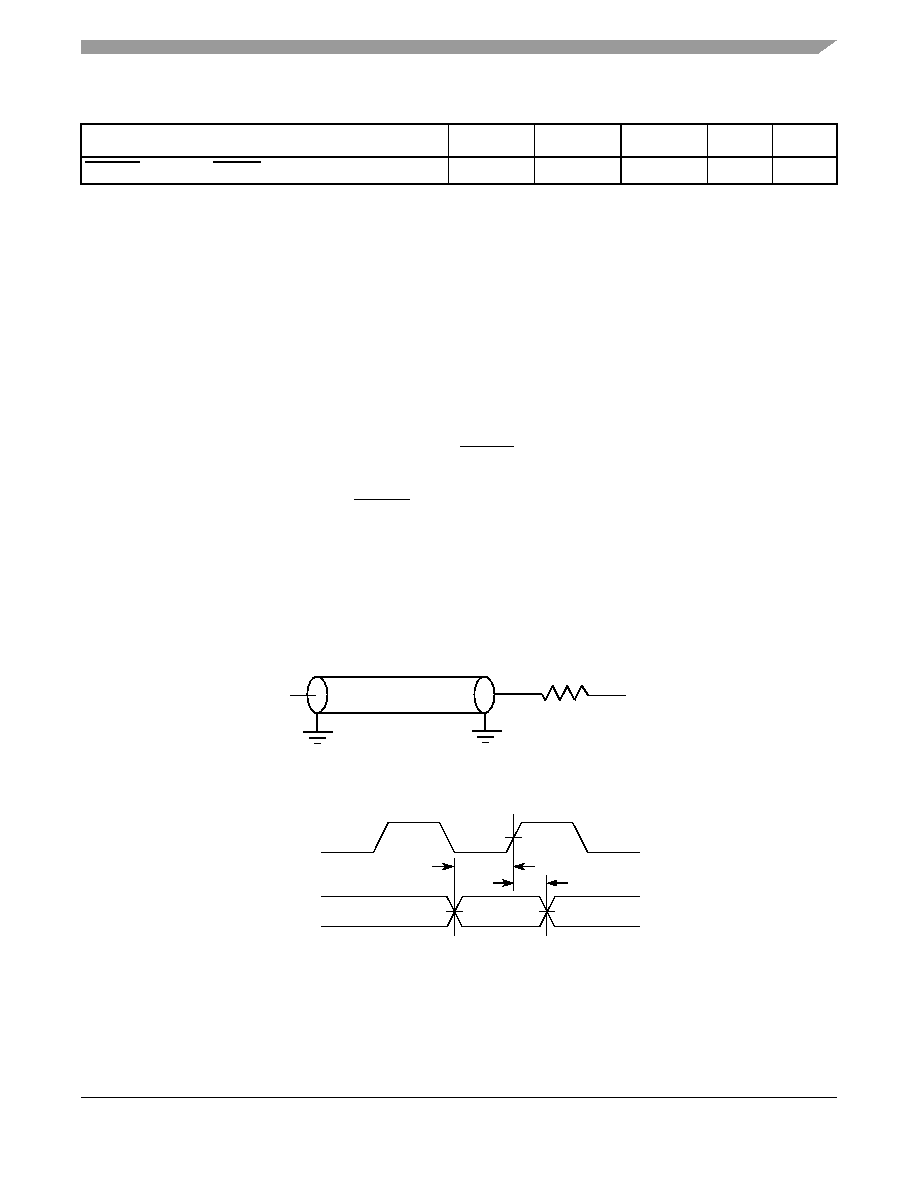

Figure 15 provides the AC test load for PCI.

Figure 26. PCI AC Test Load

Figure 27 shows the PCI input AC timing conditions.

Figure 27. PCI Input AC Timing Measurement Conditions

HRESET high to first FRAME assertion

tPCRHFV

10

—

clocks

8, 11

Notes:

1. The symbols used for timing specifications follow the pattern of t(first two letters of functional block)(signal)(state)(reference)(state) for

inputs and t(first two letters of functional block)(reference)(state)(signal)(state) for outputs. For example, tPCIVKH symbolizes PCI timing

(PC) with respect to the time the input signals (I) reach the valid state (V) relative to the SYSCLK clock, tSYS, reference (K)

going to the high (H) state or setup time. Also, tPCRHFV symbolizes PCI timing (PC) with respect to the time hard reset (R)

went high (H) relative to the frame signal (F) going to the valid (V) state.

2. See the timing measurement conditions in the

PCI 2.2 Local Bus Specifications.

3. All PCI signals are measured from OVDD/2 of the rising edge of PCI_SYNC_IN to 0.4 × OVDD of the signal in question for

3.3-V PCI signaling levels.

4. For purposes of active/float timing measurements, the Hi-Z or off state is defined to be when the total current delivered

through the component pin is less than or equal to the leakage current specification.

5. Input timings are measured at the pin.

6. The timing parameter tSYS indicates the minimum and maximum CLK cycle times for the various specified frequencies. The

system clock period must be kept within the minimum and maximum defined ranges. For values see Section 3.1, “System

7. The setup and hold time is with respect to the rising edge of HRESET.

8. The timing parameter tPCRHFV is a minimum of 10 clocks rather than the minimum of 5 clocks in the PCI 2.2 Local Bus

Specifications.

9. The reset assertion timing requirement for HRESET is 100

μs.

10.Guaranteed by characterization.

11.Guaranteed by design.

12. The timing parameter tPCKHOV is a minimum of 1.5 ns and a maximum of 7.4 ns rather than the minimum of 2 ns and a

maximum of 6 ns in the

PCI 2.2 Local Bus Specifications.

13. The timing parameter tPCIVKH is a minimum of 3.7 ns rather than the minimum of 3 ns in the PCI 2.2 Local Bus Specifications.

14. The timing parameter tPCIXKH is a minimum of 0.8 ns rather than the minimum of 0 ns in the PCI 2.2 Local Bus Specifications.

Table 46. PCI AC Timing Specifications at 66 MHz (continued)

Parameter

Symbol1

Min

Max

Unit

Notes

Output

Z0 = 50 Ω

OVDD/2

RL = 50 Ω

tPCIVKH

CLK

Input

tPCIXKH

相关PDF资料 |

PDF描述 |

|---|---|

| MB95F134NBWPFV | 8-BIT, FLASH, 16.25 MHz, MICROCONTROLLER, PDSO30 |

| MC9S12GC128PMPB25 | 16-BIT, FLASH, 25 MHz, MICROCONTROLLER, PQFP52 |

| M30201F6T-FP | 16-BIT, FLASH, 10 MHz, MICROCONTROLLER, PQFP56 |

| M48T37Y-70MH6F | 0 TIMER(S), REAL TIME CLOCK, PDSO44 |

| MC68HC08GP16ACFB | 8-BIT, MROM, 8.2 MHz, MICROCONTROLLER, PQFP44 |

相关代理商/技术参数 |

参数描述 |

|---|---|

| MC8610TPX1067G | 制造商:FREESCALE 制造商全称:Freescale Semiconductor, Inc 功能描述:Integrated Host Processor Hardware Specifications |

| MC8610TPX1067J | 制造商:FREESCALE 制造商全称:Freescale Semiconductor, Inc 功能描述:Integrated Host Processor Hardware Specifications |

| MC8610TPX800G | 制造商:FREESCALE 制造商全称:Freescale Semiconductor, Inc 功能描述:Integrated Host Processor Hardware Specifications |

| MC8610TPX800GB | 功能描述:微处理器 - MPU REV 1.1 8610 1.0V -40C RoHS:否 制造商:Atmel 处理器系列:SAMA5D31 核心:ARM Cortex A5 数据总线宽度:32 bit 最大时钟频率:536 MHz 程序存储器大小:32 KB 数据 RAM 大小:128 KB 接口类型:CAN, Ethernet, LIN, SPI,TWI, UART, USB 工作电源电压:1.8 V to 3.3 V 最大工作温度:+ 85 C 安装风格:SMD/SMT 封装 / 箱体:FBGA-324 |

| MC8610TPX800GZ | 制造商:FREESCALE 制造商全称:Freescale Semiconductor, Inc 功能描述:MPC8610 Integrated Host Processor Hardware Specifications |

发布紧急采购,3分钟左右您将得到回复。