- 您现在的位置:买卖IC网 > PDF目录16673 > MCP2150DM (Microchip Technology)BOARD DEMO FOR MCP2150 PDF资料下载

参数资料

| 型号: | MCP2150DM |

| 厂商: | Microchip Technology |

| 文件页数: | 43/52页 |

| 文件大小: | 0K |

| 描述: | BOARD DEMO FOR MCP2150 |

| 标准包装: | 1 |

| 主要目的: | 接口,IrDA |

| 嵌入式: | 是,MCU,8 位 |

| 已用 IC / 零件: | MCP2150 |

| 主要属性: | 带 PIC18F MCU 的 IrDA 控制器 |

| 次要属性: | USB 接口 |

| 已供物品: | 板 |

| 产品目录页面: | 685 (CN2011-ZH PDF) |

第1页第2页第3页第4页第5页第6页第7页第8页第9页第10页第11页第12页第13页第14页第15页第16页第17页第18页第19页第20页第21页第22页第23页第24页第25页第26页第27页第28页第29页第30页第31页第32页第33页第34页第35页第36页第37页第38页第39页第40页第41页第42页当前第43页第44页第45页第46页第47页第48页第49页第50页第51页第52页

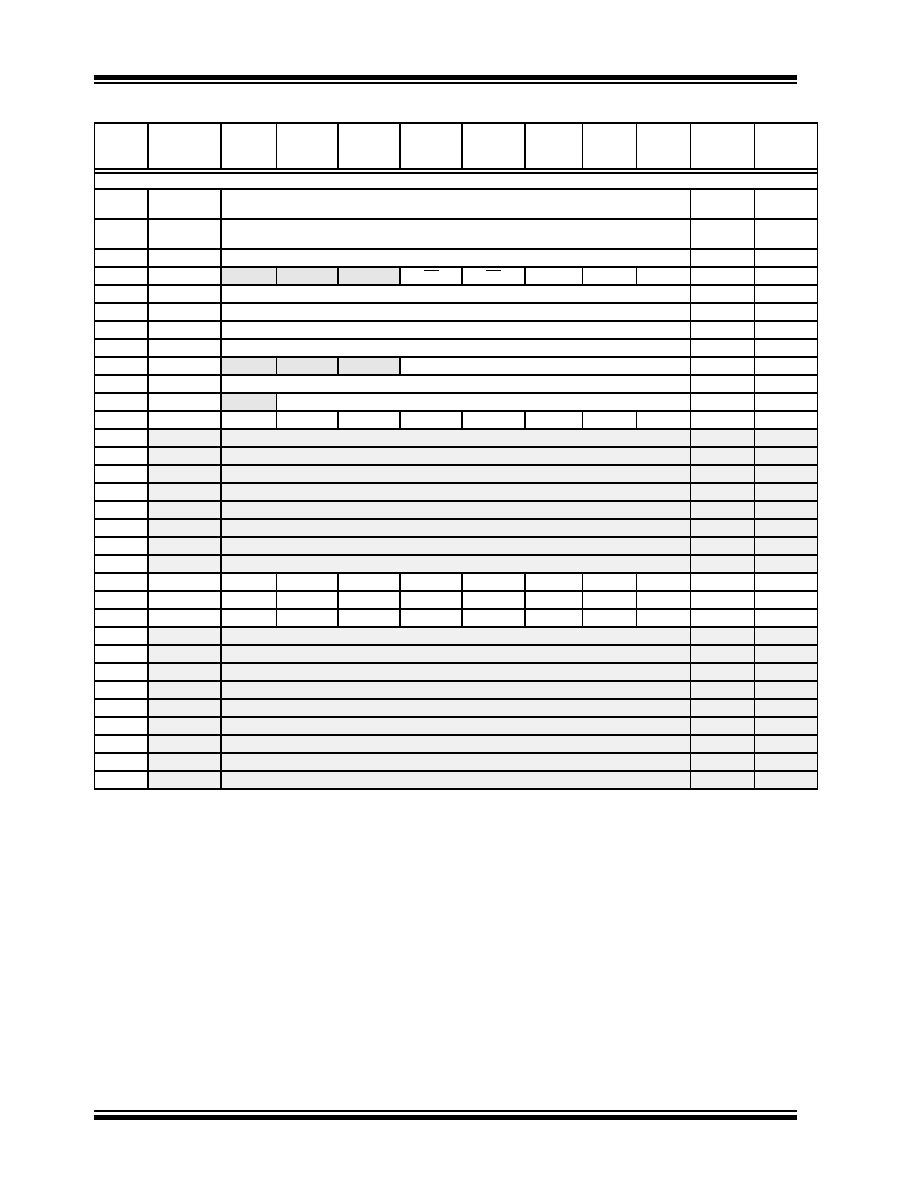

PIC16F193X/LF193X

DS41364D-page 48

Preliminary

2009 Microchip Technology Inc.

Bank 7

380h(2)

INDF0

Addressing this location uses contents of FSR0H/FSR0L to address data memory

(not a physical register)

xxxx xxxx xxxx xxxx

381h(2)

INDF1

Addressing this location uses contents of FSR1H/FSR1L to address data memory

(not a physical register)

xxxx xxxx xxxx xxxx

382h(2)

PCL

Program Counter (PC) Least Significant Byte

0000 0000 0000 0000

383h(2)

STATUS

—

—TO

PD

ZDC

C

---1 1000 ---q quuu

384h(2)

FSR0L

Indirect Data Memory Address 0 Low Pointer

0000 0000 uuuu uuuu

385h(2)

FSR0H

Indirect Data Memory Address 0 High Pointer

0000 0000 0000 0000

386h(2)

FSR1L

Indirect Data Memory Address 1 Low Pointer

0000 0000 uuuu uuuu

387h(2)

FSR1H

Indirect Data Memory Address 1 High Pointer

0000 0000 0000 0000

388h(2)

BSR

—

BSR<4:0>

---0 0000 ---0 0000

389h(2)

WREG

Working Register

0000 0000 uuuu uuuu

38Ah(1, 2) PCLATH

—

Write Buffer for the upper 7 bits of the Program Counter

-000 0000 -000 0000

38Bh(2)

INTCON

GIE

PEIE

TMR0IE

INTE

IOCIE

TMR0IF

INTF

IOCIF

0000 000x 0000 000u

38Ch

—

Unimplemented

—

38Dh

—

Unimplemented

—

38Eh

—

Unimplemented

—

38Fh

—

Unimplemented

—

390h

—

Unimplemented

—

391h

—

Unimplemented

—

392h

—

Unimplemented

—

393h

—

Unimplemented

—

394h

IOCBP

IOCBP7

IOCBP6

IOCBP5

IOCBP4

IOCBP3

IOCBP2

IOCBP1

IOCBP0 0000 0000 0000 0000

395h

IOCBN

IOCBN7

IOCBN6

IOCBN5

IOCBN4

IOCBN3

IOCBN2

IOCBN1

IOCBN0 0000 0000 0000 0000

396h

IOCBF

IOCBF7

IOCBF6

IOCBF5

IOCBF4

IOCBF3

IOCBF2

IOCBF1

IOCBF0

0000 0000 0000 0000

397h

—

Unimplemented

—

398h

—

Unimplemented

—

399h

—

Unimplemented

—

39Ah

—

Unimplemented

—

39Bh

—

Unimplemented

—

39Ch

—

Unimplemented

—

39Dh

—

Unimplemented

—

39Eh

—

Unimplemented

—

39Fh

—

Unimplemented

—

TABLE 3-14:

SPECIAL FUNCTION REGISTER SUMMARY (CONTINUED)

Address

Name

Bit 7

Bit 6

Bit 5

Bit 4

Bit 3

Bit 2

Bit 1

Bit 0

Value on:

POR, BOR

Value on all

other

Resets

Legend:

x

= unknown, u = unchanged, q = value depends on condition, - = unimplemented, read as ‘0’, r = reserved.

Shaded locations are unimplemented, read as ‘0’.

Note

1:

The upper byte of the program counter is not directly accessible. PCLATH is a holding register for the PC<14:8>, whose contents are trans-

ferred to the upper byte of the program counter.

2:

These registers can be addressed from any bank.

3:

These registers/bits are not implemented on PIC16F1933/1936/1938/PIC16LF1933/1936/1938 devices, read as ‘0’.

4:

The Capacitive Sensing Reference Mode (CPSRM) bit is not available for the PIC16F/LF1934/1936/1937 devices.

相关PDF资料 |

PDF描述 |

|---|---|

| GBM10DRSN-S664 | CONN EDGECARD 20POS DIP .156 SLD |

| CB5278-000 | HEAT SHRINK TUBING |

| ELC-10D390E | COIL CHOKE 39UH RADIAL |

| CB5270-000 | HEAT SHRINK TUBING |

| VI-BWV-EX | CONVERTER MOD DC/DC 5.8V 75W |

相关代理商/技术参数 |

参数描述 |

|---|---|

| MCP2150-I/P | 功能描述:输入/输出控制器接口集成电路 IrDA protocol handlr RoHS:否 制造商:Silicon Labs 产品: 输入/输出端数量: 工作电源电压: 最大工作温度:+ 85 C 最小工作温度:- 40 C 安装风格:SMD/SMT 封装 / 箱体:QFN-64 封装:Tray |

| MCP2150-I/P | 制造商:Microchip Technology Inc 功能描述:IC IRDA CONTROLLER 2150 DIP18 |

| MCP2150-I/SO | 功能描述:输入/输出控制器接口集成电路 IrDA protocol handlr RoHS:否 制造商:Silicon Labs 产品: 输入/输出端数量: 工作电源电压: 最大工作温度:+ 85 C 最小工作温度:- 40 C 安装风格:SMD/SMT 封装 / 箱体:QFN-64 封装:Tray |

| MCP2150-I/SO | 制造商:Microchip Technology Inc 功能描述:IRDA CONTROLLER SMD 2150 SOIC18 |

| MCP2150-I/SORVB | 制造商:Microchip 功能描述:MCP2150 Series 115.2 kBaud 64 Byte Standard Protocol Stack Controller - SOIC-18 |

发布紧急采购,3分钟左右您将得到回复。