- 您现在的位置:买卖IC网 > PDF目录29137 > MPC973FA (INTEGRATED DEVICE TECHNOLOGY INC) 973 SERIES, PLL BASED CLOCK DRIVER, 12 TRUE OUTPUT(S), 0 INVERTED OUTPUT(S), PQFP52 PDF资料下载

参数资料

| 型号: | MPC973FA |

| 厂商: | INTEGRATED DEVICE TECHNOLOGY INC |

| 元件分类: | 时钟及定时 |

| 英文描述: | 973 SERIES, PLL BASED CLOCK DRIVER, 12 TRUE OUTPUT(S), 0 INVERTED OUTPUT(S), PQFP52 |

| 封装: | LQFP-52 |

| 文件页数: | 11/13页 |

| 文件大小: | 629K |

| 代理商: | MPC973FA |

MPC973

7

MOTOROLA

Using the MPC973 as a Zero Delay Buffer

The external feedback of the MPC973 clock driver allows for

its use as a zero delay buffer. By using one of the outputs as a

feedback to the PLL the propagation delay through the device

is eliminated. The PLL works to align the output edge with the

input reference edge thus producing a near zero delay. The

reference frequency affects the static phase offset of the PLL

and thus the relative delay between the inputs and outputs.

Because the static phase offset is a function of the reference

clock the Tpd of the MPC973 is a function of the configuration

used.

When used as a zero delay buffer the MPC973 will likely be

in a nested clock tree application. For these applications the

MPC973 offers a LVPECL clock input as a PLL reference. This

allows the user to use LVPECL as the primary clock distribution

device to take advantage of its far superior skew performance.

The MPC973 then can lock onto the LVPECL reference and

translate with near zero delay to low skew LVCMOS outputs.

Clock trees implemented in this fashion will show significantly

tighter skews than trees developed from CMOS fanout buffers.

To calculate the overall uncertainty between the input

reference clock and the output clocks the following approach

should be used. Figure 4 through 7 contains performance

information to assist in calculating the overall uncertainty. Data

presented in Figures 4 through 7 is representative data but is

not guaranteed under all conditions. Since the overall skew

performance is a function of the input reference frequency all

of the graphs provide relavent data with respect to the input

reference frequency.

The overall uncertainty can be broken down into three parts;

the static phase offset variation (Tpd), the I/O phase jitter and

the output skew. If we assume that we have a 75 MHz reference

clock, from the graphs we can pull the following information for

static phase offset (SPO) and I/O jitter: the SPO variation will

be 300 ps (–100 ps to +200 ps assuming a TCLK is used) and

the I/O jitter will be

±105 ps (assuming a VCO/6 configuration

and a

±3 sigma for min and max). The nominal delay from

Figure 5 is 50 ps so that the propagation delay between the

reference clock and the feedback clock is 50 ps

±255 ps.

Figure 4 can now be used to establish the uncertainty

between the reference clock and all of the outputs for the

MPC973. Figure 4 provides the skew of the MC973 outputs with

respect to the feedback output. From Figure 4, if all of the

outputs are used the propagation delay of the device will range

from –555 ps (50 ps – 255 ps – 350 ps) to +705 ps (50 ps +

255 ps + 400 ps) for a total uncertainty of 1.26 ns. This 1.26ns

uncertainty would hold true if multiple 973’s are used in parallel

in the application given that the skew between the reference

clock for the devices were zero. Notice from the data in Figure

4 that if a subset of the outputs were used significant reductions

in uncertainty could be obtained.

SYNC Output Description

In situations where output frequency relationships are not

integer multiples of each other there is a need for a signal for

system synchronization purposes. The SYNC output of the

MPC973 is designed to specifically address this need. The

MPC973 monitors the relationship between the Qa and the Qc

banks of outputs. It provides a low going pulse, one period in

duration, one period prior to the coincident rising edges of the

Qa and Qc outputs. The duration and the placement of the

pulse is dependent on the higher of the Qa and Qc output

frequencies. The timing diagrams in the data sheet show the

various waveforms for the SYNC output. Note that the SYNC

output is defined for all possible combinations of the Qa and Qc

outputs even though under some relationships the lower

frequency clock could be used as a synchronizing signal.

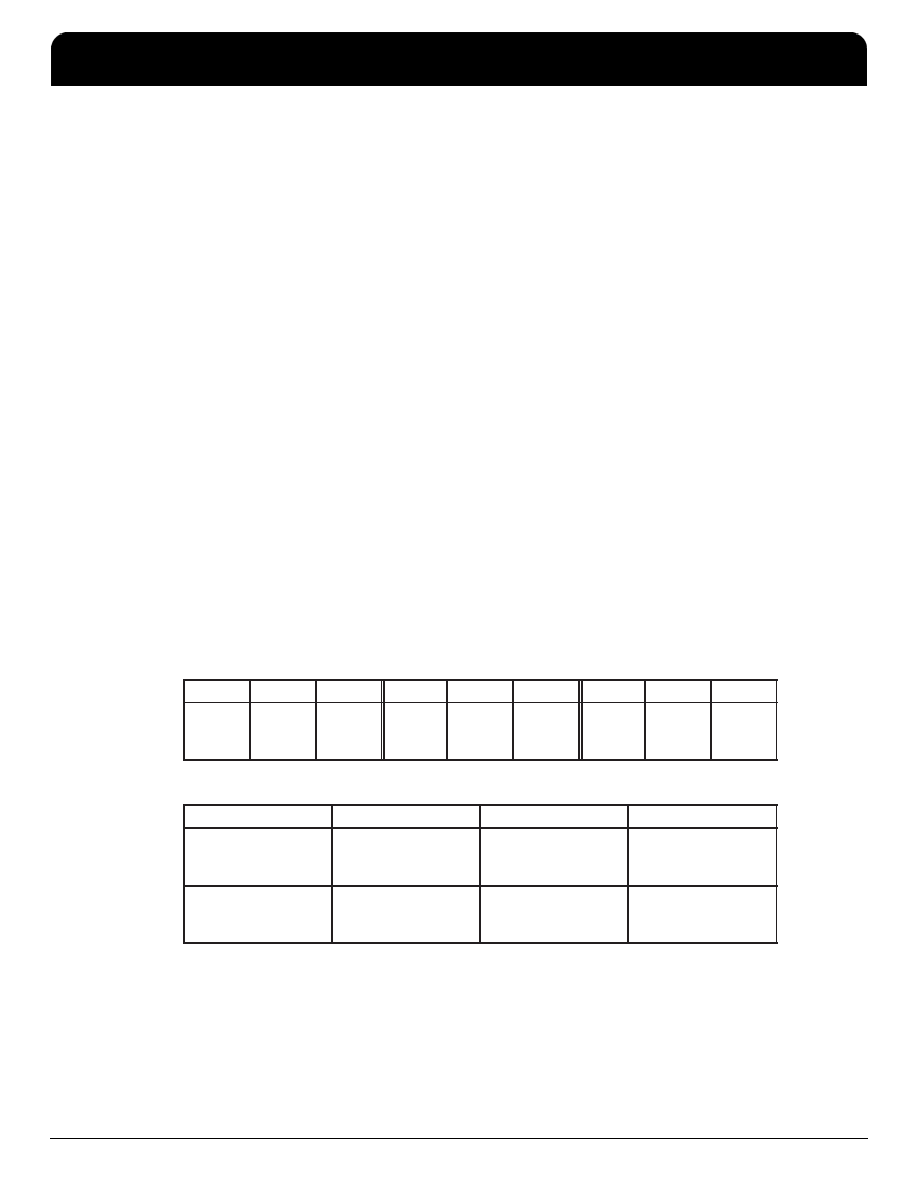

1. Programmable Output Frequency Relationships (VCO_Sel=‘1’)

fsela1

fsela0

Qa

fselb1

fselb0

Qb

fselc1

fselc0

Qc

0

1

0

1

0

1

VCO/4

VCO/6

VCO/8

VCO/12

0

1

0

1

0

1

VCO/4

VCO/6

VCO/8

VCO/10

0

1

0

1

0

1

VCO/2

VCO/4

VCO/6

VCO/8

2. Programmable Output Frequency Relationships (VCO_Sel=‘1’)

fselFB2

fselFB1

fselFB0

QFB

0

1

0

1

0

1

VCO/4

VCO/6

VCO/8

VCO/10

1

0

1

0

1

0

1

VCO/8

VCO/12

VCO/16

VCO/20

F

re

e

sc

a

le

S

e

m

ic

o

n

d

u

c

to

r,

I

Freescale Semiconductor, Inc.

For More Information On This Product,

Go to: www.freescale.com

n

c

..

.

MPC973

Low Voltage PLL Clock Driver

NETCOM

IDT Low Voltage PLL Clock Driver

Freescale Timing Solutions Organization has been acquired by Integrated Device Technology, Inc

MPC973

7

相关PDF资料 |

PDF描述 |

|---|---|

| MPC974FAR2 | 974 SERIES, PLL BASED CLOCK DRIVER, 14 TRUE OUTPUT(S), 0 INVERTED OUTPUT(S), PQFP52 |

| MPC974FA | 974 SERIES, PLL BASED CLOCK DRIVER, 14 TRUE OUTPUT(S), 0 INVERTED OUTPUT(S), PQFP52 |

| MPC974FA | 974 SERIES, PLL BASED CLOCK DRIVER, 14 TRUE OUTPUT(S), 0 INVERTED OUTPUT(S), PQFP52 |

| MPC9773AE | 9773 SERIES, PLL BASED CLOCK DRIVER, 12 TRUE OUTPUT(S), 0 INVERTED OUTPUT(S), PQFP52 |

| MPC97H74AER2 | 97H SERIES, PLL BASED CLOCK DRIVER, 14 TRUE OUTPUT(S), 0 INVERTED OUTPUT(S), PQFP52 |

相关代理商/技术参数 |

参数描述 |

|---|---|

| MPC974 | 制造商:MOTOROLA 制造商全称:Motorola, Inc 功能描述:LOW VOLTAGE PLL CLOCK DRIVER |

| MPC974A44 F44A WAF | 制造商:Motorola Inc 功能描述: |

| MPC9772 | 制造商:MOTOROLA 制造商全称:Motorola, Inc 功能描述:3.3V 1:12 LVCMOS PLL Clock Generator |

| MPC9772AE | 功能描述:锁相环 - PLL 2.5 3.3V 250MHz Clock Generator RoHS:否 制造商:Silicon Labs 类型:PLL Clock Multiplier 电路数量:1 最大输入频率:710 MHz 最小输入频率:0.002 MHz 输出频率范围:0.002 MHz to 808 MHz 电源电压-最大:3.63 V 电源电压-最小:1.71 V 最大工作温度:+ 85 C 最小工作温度:- 40 C 封装 / 箱体:QFN-36 封装:Tray |

| MPC9772AER2 | 功能描述:时钟发生器及支持产品 FSL 1-12 LVCMOS PLL Clock Generator, xta RoHS:否 制造商:Silicon Labs 类型:Clock Generators 最大输入频率:14.318 MHz 最大输出频率:166 MHz 输出端数量:16 占空比 - 最大:55 % 工作电源电压:3.3 V 工作电源电流:1 mA 最大工作温度:+ 85 C 安装风格:SMD/SMT 封装 / 箱体:QFN-56 |

发布紧急采购,3分钟左右您将得到回复。