- 您现在的位置:买卖IC网 > PDF目录29137 > MPC973FA (INTEGRATED DEVICE TECHNOLOGY INC) 973 SERIES, PLL BASED CLOCK DRIVER, 12 TRUE OUTPUT(S), 0 INVERTED OUTPUT(S), PQFP52 PDF资料下载

参数资料

| 型号: | MPC973FA |

| 厂商: | INTEGRATED DEVICE TECHNOLOGY INC |

| 元件分类: | 时钟及定时 |

| 英文描述: | 973 SERIES, PLL BASED CLOCK DRIVER, 12 TRUE OUTPUT(S), 0 INVERTED OUTPUT(S), PQFP52 |

| 封装: | LQFP-52 |

| 文件页数: | 6/13页 |

| 文件大小: | 629K |

| 代理商: | MPC973FA |

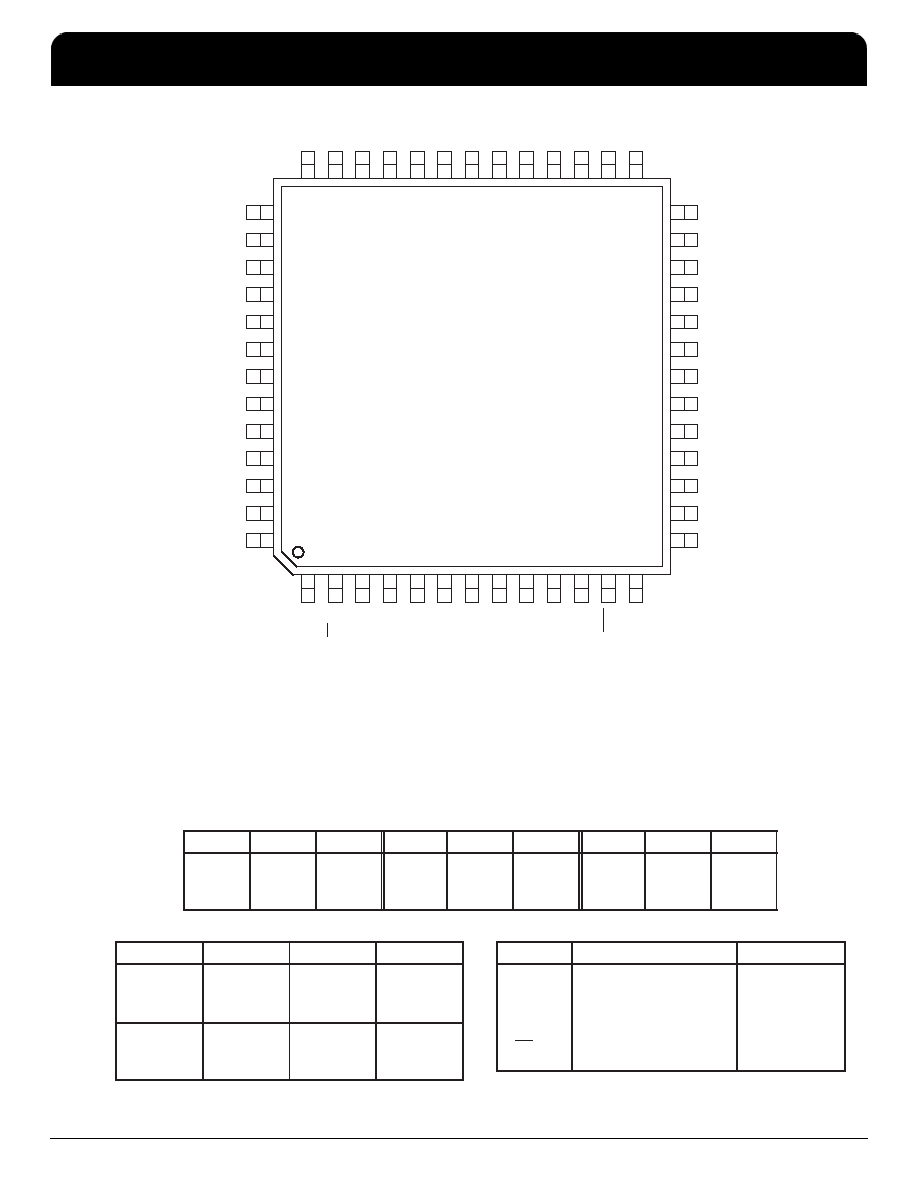

MPC973

2

MOTOROLA

fselb1

fselb0

fsela1

fsela0

Qa3

VCCO

Qa2

GNDO

Qa1

VCCO

Qa0

GNDO

VCO_Sel

fselFB1

QSync

GNDO

Qc0

VCCO

Qc1

fselc0

fselc1

Qc2

VCCO

Qc3

GNDO

Inv_Clk

GNDO

Qb0

VCCO

Qb1

GNDO

Qb2

VCCO

Qb3

Ext_FB

GNDO

QFB

VCCI

fselFB0

GNDI

MR/OE

Frz_Clk

Frz_Data

fselFB2

PLL_EN

Ref_Sel

TClk_Sel

TClk0

TClk1

VCCA

40

41

42

43

44

45

46

47

48

49

50

51

52

25

24

23

22

21

20

19

18

17

16

15

14

1234

56789

10

11

12

13

39

38

37

36

35

34

33

32

31

30

29

28

27

26

MPC973

PCLK

Figure 1. 52–Lead Pinout (Top View)

All inputs have internal pull-up resistors (appr. 50 K) except for the xtal1 and xtal2 pins.

FUNCTION TABLE 1

fsela1

fsela0

Qa

fselb1

fselb0

Qb

fselc1

fselc0

Qc

0

1

0

1

0

1

÷4

÷6

÷8

÷12

0

1

0

1

0

1

÷4

÷6

÷8

÷10

0

1

0

1

0

1

÷2

÷4

÷6

÷8

FUNCTION TABLE 2

*fselFB2

fselFB1

fselFB0

QFB

0

1

0

1

0

1

÷4

÷6

÷8

÷10

1

0

1

0

1

0

1

÷8

÷12

÷16

÷20

* If the fselFB2 is 1, it may be necessary to apply a reset after power up

to ensure synchronization between QFB and the other inputs.

FUNCTION TABLE 3

Control Pin

Logic ‘0’

Logic ‘1’

VCO_Sel

VCO/2

VCO

Ref_Sel

TCLK

Xtal (PECL)

TCLK_Sel

TCLK0

TCLK1

PLL_En

Bypass PLL

Enable PLL

MR/OE

Master Reset/Output Hi–Z

Enable Outputs

Inv_Clk

Non–Inverted Qc2, Qc3

Inverted Qc2, Qc3

F

re

e

sc

a

le

S

e

m

ic

o

n

d

u

c

to

r,

I

Freescale Semiconductor, Inc.

For More Information On This Product,

Go to: www.freescale.com

n

c

..

.

MPC973

Low Voltage PLL Clock Driver

NETCOM

IDT Low Voltage PLL Clock Driver

Freescale Timing Solutions Organization has been acquired by Integrated Device Technology, Inc

MPC973

2

相关PDF资料 |

PDF描述 |

|---|---|

| MPC974FAR2 | 974 SERIES, PLL BASED CLOCK DRIVER, 14 TRUE OUTPUT(S), 0 INVERTED OUTPUT(S), PQFP52 |

| MPC974FA | 974 SERIES, PLL BASED CLOCK DRIVER, 14 TRUE OUTPUT(S), 0 INVERTED OUTPUT(S), PQFP52 |

| MPC974FA | 974 SERIES, PLL BASED CLOCK DRIVER, 14 TRUE OUTPUT(S), 0 INVERTED OUTPUT(S), PQFP52 |

| MPC9773AE | 9773 SERIES, PLL BASED CLOCK DRIVER, 12 TRUE OUTPUT(S), 0 INVERTED OUTPUT(S), PQFP52 |

| MPC97H74AER2 | 97H SERIES, PLL BASED CLOCK DRIVER, 14 TRUE OUTPUT(S), 0 INVERTED OUTPUT(S), PQFP52 |

相关代理商/技术参数 |

参数描述 |

|---|---|

| MPC974 | 制造商:MOTOROLA 制造商全称:Motorola, Inc 功能描述:LOW VOLTAGE PLL CLOCK DRIVER |

| MPC974A44 F44A WAF | 制造商:Motorola Inc 功能描述: |

| MPC9772 | 制造商:MOTOROLA 制造商全称:Motorola, Inc 功能描述:3.3V 1:12 LVCMOS PLL Clock Generator |

| MPC9772AE | 功能描述:锁相环 - PLL 2.5 3.3V 250MHz Clock Generator RoHS:否 制造商:Silicon Labs 类型:PLL Clock Multiplier 电路数量:1 最大输入频率:710 MHz 最小输入频率:0.002 MHz 输出频率范围:0.002 MHz to 808 MHz 电源电压-最大:3.63 V 电源电压-最小:1.71 V 最大工作温度:+ 85 C 最小工作温度:- 40 C 封装 / 箱体:QFN-36 封装:Tray |

| MPC9772AER2 | 功能描述:时钟发生器及支持产品 FSL 1-12 LVCMOS PLL Clock Generator, xta RoHS:否 制造商:Silicon Labs 类型:Clock Generators 最大输入频率:14.318 MHz 最大输出频率:166 MHz 输出端数量:16 占空比 - 最大:55 % 工作电源电压:3.3 V 工作电源电流:1 mA 最大工作温度:+ 85 C 安装风格:SMD/SMT 封装 / 箱体:QFN-56 |

发布紧急采购,3分钟左右您将得到回复。