- 您现在的位置:买卖IC网 > PDF目录29137 > MPC9773AE (INTEGRATED DEVICE TECHNOLOGY INC) 9773 SERIES, PLL BASED CLOCK DRIVER, 12 TRUE OUTPUT(S), 0 INVERTED OUTPUT(S), PQFP52 PDF资料下载

参数资料

| 型号: | MPC9773AE |

| 厂商: | INTEGRATED DEVICE TECHNOLOGY INC |

| 元件分类: | 时钟及定时 |

| 英文描述: | 9773 SERIES, PLL BASED CLOCK DRIVER, 12 TRUE OUTPUT(S), 0 INVERTED OUTPUT(S), PQFP52 |

| 封装: | 10 X 10 MM, 1.40 MM HEIGHT, 0.65 MM PITCH, LEAD FREE, LQFP-52 |

| 文件页数: | 7/19页 |

| 文件大小: | 1007K |

| 代理商: | MPC9773AE |

Advanced Clock Drivers Device Data

Freescale Semiconductor

15

MPC9773

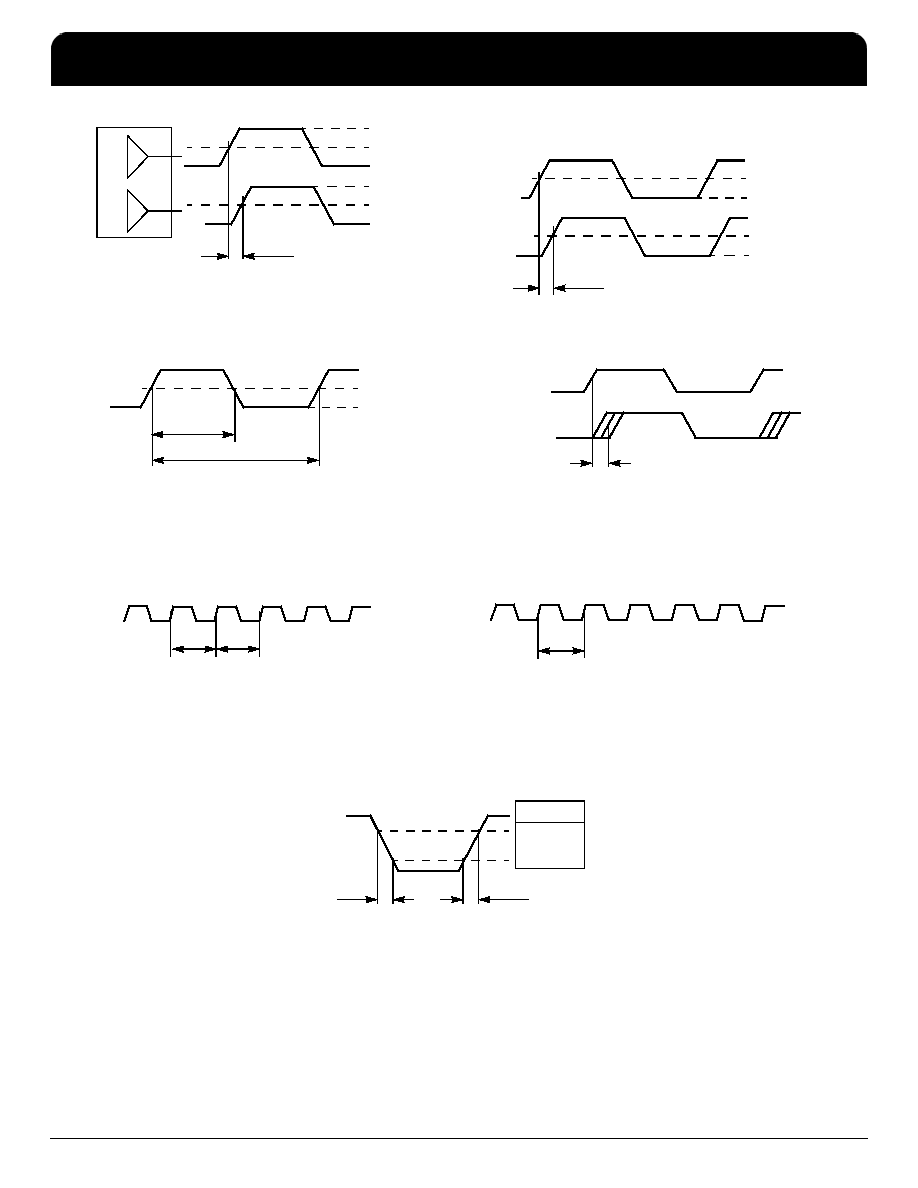

Figure 17. Output-to-Output Skew tSK(O)

Figure 18. Propagation Delay (t(), Static Phase

Offset) Test Reference

Figure 19. Output Duty Cycle (DC)

The pin-to-pin skew is defined as the worst case difference in propagation

delay between any similar delay path within a single device

The time from the PLL controlled edge to the non controlled edge,

divided by the time between PLL controlled edges, expressed as

a percentage

VCC

VCC ÷ 2

GND

VCC

VCC ÷ 2

GND

tSK(O)

VCC

VCC ÷ 2

GND

tP

T0

DC = tP/T0 x 100%

VCC

VCC ÷ 2

GND

VCC

VCC ÷ 2

GND

t()

CCLKx

FB_IN

TJIT() = |T0-T1mean|

CCLKx

FB_IN

The deviation in t0 for a controlled edge with respect to a t0 mean in a random

sample of cycles

Figure 20. I/O Jitter

TN

TJIT(CC) = |TN–TN+1|

TN+1

TJIT(PER) = |TN–1/f0|

T0

Figure 21. Cycle-to-Cycle Jitter

Figure 22. Period Jitter

The variation in cycle time of a signal between adjacent cycles, over a random

sample of adjacent cycle pairs

The deviation in cycle time of a signal with respect to the ideal period over a

random sample of cycles

tF

tR

VCC = 3.3 V

2.4

0.55

Figure 23. Output Transition Time Test Reference

MPC9773

3.3 V 1:12 LVCMOS PLL Clock Generator

NETCOM

IDT 3.3 V 1:12 LVCMOS PLL Clock Generator

Freescale Timing Solutions Organization has been acquired by Integrated Device Technology, Inc

MPC9773

15

相关PDF资料 |

PDF描述 |

|---|---|

| MPC97H74AER2 | 97H SERIES, PLL BASED CLOCK DRIVER, 14 TRUE OUTPUT(S), 0 INVERTED OUTPUT(S), PQFP52 |

| MPC97H74FAR2 | 97H SERIES, PLL BASED CLOCK DRIVER, 14 TRUE OUTPUT(S), 0 INVERTED OUTPUT(S), PQFP52 |

| MPC97H74FA | 97H SERIES, PLL BASED CLOCK DRIVER, 14 TRUE OUTPUT(S), 0 INVERTED OUTPUT(S), PQFP52 |

| MPC9893FAR2 | 9893 SERIES, PLL BASED CLOCK DRIVER, 12 TRUE OUTPUT(S), 0 INVERTED OUTPUT(S), PQFP48 |

| MPC991FAR2 | PLL BASED CLOCK DRIVER, 13 TRUE OUTPUT(S), 0 INVERTED OUTPUT(S), PQFP52 |

相关代理商/技术参数 |

参数描述 |

|---|---|

| MPC9773AER2 | 功能描述:时钟发生器及支持产品 FSL 1-12 LVCMOS/LVPE CL to LVCMOS PLL Clo RoHS:否 制造商:Silicon Labs 类型:Clock Generators 最大输入频率:14.318 MHz 最大输出频率:166 MHz 输出端数量:16 占空比 - 最大:55 % 工作电源电压:3.3 V 工作电源电流:1 mA 最大工作温度:+ 85 C 安装风格:SMD/SMT 封装 / 箱体:QFN-56 |

| MPC9773FA | 功能描述:锁相环 - PLL 3.3V 240MHz Clock Generator RoHS:否 制造商:Silicon Labs 类型:PLL Clock Multiplier 电路数量:1 最大输入频率:710 MHz 最小输入频率:0.002 MHz 输出频率范围:0.002 MHz to 808 MHz 电源电压-最大:3.63 V 电源电压-最小:1.71 V 最大工作温度:+ 85 C 最小工作温度:- 40 C 封装 / 箱体:QFN-36 封装:Tray |

| MPC9773FAR2 | 制造商:Integrated Device Technology Inc 功能描述:PLL Clock Driver Single 52-Pin LQFP T/R 制造商:Integrated Device Technology Inc 功能描述:MPC9773FAR2 - Tape and Reel |

| MPC9774 | 制造商:MOTOROLA 制造商全称:Motorola, Inc 功能描述:3.3V / 2,5V 1:14 LVCMOS PLL CLOCK GENERATOR |

| MPC9774AE | 功能描述:时钟发生器及支持产品 3.3V 125MHz Clock Generator RoHS:否 制造商:Silicon Labs 类型:Clock Generators 最大输入频率:14.318 MHz 最大输出频率:166 MHz 输出端数量:16 占空比 - 最大:55 % 工作电源电压:3.3 V 工作电源电流:1 mA 最大工作温度:+ 85 C 安装风格:SMD/SMT 封装 / 箱体:QFN-56 |

发布紧急采购,3分钟左右您将得到回复。