- 您现在的位置:买卖IC网 > PDF目录385639 > MT4C4256 (Micron Technology, Inc.) 256K x 4 DRAM Standard Or Low Power, Extended Refresh(标准或低功率,扩展刷新,256K x 4动态RAM) PDF资料下载

参数资料

| 型号: | MT4C4256 |

| 厂商: | Micron Technology, Inc. |

| 英文描述: | 256K x 4 DRAM Standard Or Low Power, Extended Refresh(标准或低功率,扩展刷新,256K x 4动态RAM) |

| 中文描述: | 256K × 4的DRAM标准或低功耗,延长刷新(标准或低功率,扩展刷新,256K × 4动态内存) |

| 文件页数: | 1/15页 |

| 文件大小: | 240K |

| 代理商: | MT4C4256 |

MT4C4256(L)

REV. 4/94

Micron Semiconductor, Inc., reserves the right to change products or specifications without notice.

1994, Micron Semiconductor, Inc.

1

MT4C4256(L)

256K x 4 DRAM

OBSOLETE

FEATURES

512-cycle refresh in 8ms (MT4C4256) or 64ms

(MT4C4256 L)

Industry-standard x4 pinout, timing, functions and

packages

High-performance CMOS silicon-gate process

Single +5V

±

10% power supply

Low power, 0.8mW standby; 175mW active, typical

All inputs, outputs and clocks are TTL-compatible

FAST PAGE MODE access cycle

Refresh modes:

/

R

A

/

S ONLY,

/

C

A

/

S-BEFORE-

/

R

A

/

S (CBR),

HIDDEN and Extended (MT4C4256 L only)

Low CMOS Standby Current, 200

μ

A maximum

(MT4C4256 L)

OPTIONS

Timing

60ns access

70ns acces

80ns access

Packages

Plastic DIP (300 mil)

Plastic SOJ (300 mil)

Plastic ZIP (350 mil)

Version

512-cycle refresh in 8 ms

512-cycle refresh in 64 ms

Part Number Example: MT4C4256DJ-7 L

MARKING

-6

-7

-8

None

DJ

Z

None

L

DRAM

256K x 4 DRAM

STANDARD OR LOW POWER,

EXTENDED REFRESH

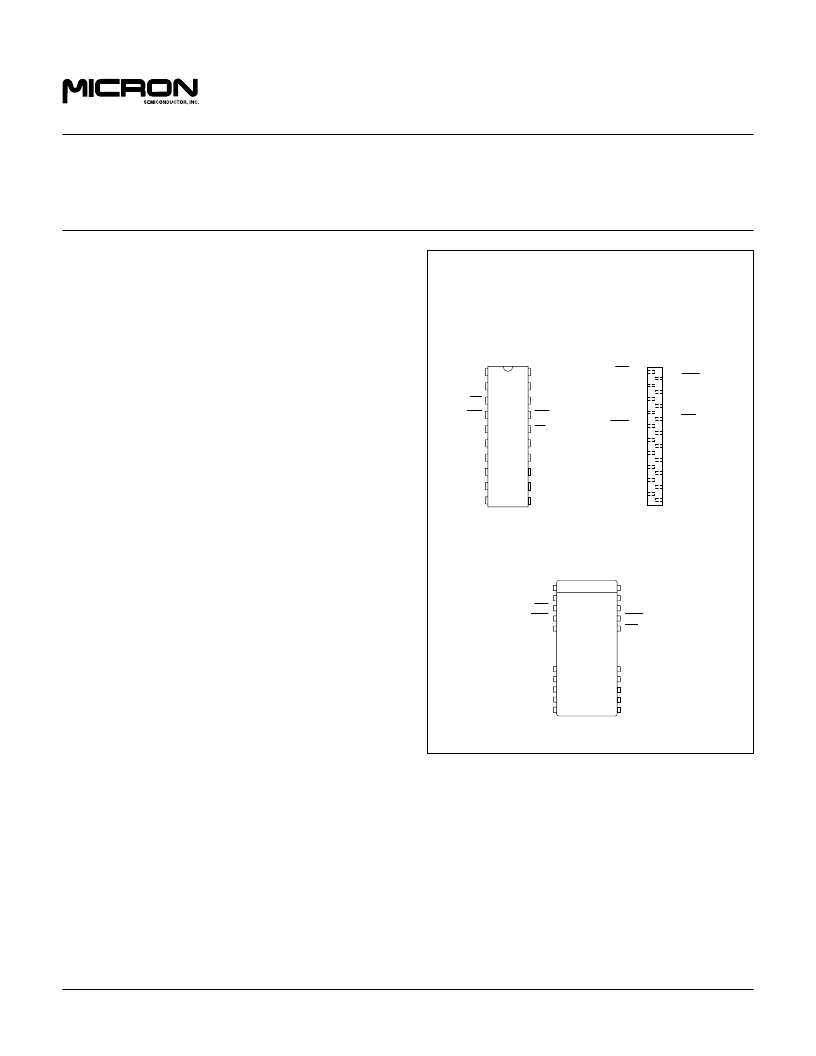

PIN ASSIGNMENT (Top View)

GENERAL DESCRIPTION

The MT4C4256(L) is a randomly accessed solid-state

memory containing 1,048,576 bits organized in a x4 configu-

ration. During READ or WRITE cycles, each bit is uniquely

addressed through the 18 address bits, which are entered 9

bits (A0-A8) at a time.

/

R

A

/

S is used to latch the first 9 bits and

/

C

A

/

S the latter 9 bits. READ and WRITE cycles are selected

with the

W

/

E input. A logic HIGH on

W

/

E dictates READ

mode while a logic LOW on

W

/

E dictates WRITE mode.

During a WRITE cycle, data-in (D) is latched by the falling

edge of

W

/

E or

/

C

A

/

S, whichever occurs last. If

W

/

E goes LOW

prior to

/

C

A

/

S going LOW, the output pin(s) remain open

(High-Z) until the next

/

C

A

/

S cycle. If

W

/

E goes LOW after

data reaches the output pin, data-out (Q) is activated and

retains the selected cell data as long as

/

C

A

/

S remains LOW

(regardless of

W

/

E or

/

R

A

/

S). This late

W

/

E pulse results in a

READ WRITE cycle. The four data inputs and four data

outputs are routed through four pins using common I/ O

and pin direction is controlled by

W

/

E and

O

/

E.

FAST PAGE MODE operations allow faster data opera-

tions (READ, WRITE or READ-MODIFY-WRITE) within a

row-address-defined (A0-A8) page boundary. The FAST

PAGE MODE cycle is always initiated with a row-address

strobed-in by

/

R

A

/

S followed by a column-address strobed-

20/26-Pin SOJ

(DC-1)

DQ1

DQ2

WE

RAS

NC

A0

A1

A2

A3

Vcc

Vss

DQ4

DQ3

CAS

OE

A8

A7

A6

A5

A4

1

2

3

4

5

9

10

11

12

13

26

25

24

23

22

18

17

16

15

14

20-Pin DIP

(DA-2)

20-Pin ZIP

(DB-1)

DQ1

DQ2

WE

RAS

NC

A0

A1

A2

A3

Vcc

1

2

3

4

5

6

7

8

9

10

20

19

18

17

16

15

14

13

12

11

Vss

DQ4

DQ3

CAS

OE

A8

A7

A6

A5

A4

OE

DQ3

Vss

DQ2

RAS

A0

A2

Vcc

A5

A7

CAS

DQ4

DQ1

WE

NC

A1

A3

A4

A6

A8

1

3

5

7

9

11

13

15

17

19

2

4

6

8

10

12

14

16

18

20

相关PDF资料 |

PDF描述 |

|---|---|

| MT4C4256L | 256K x 4 DRAM Standard Or Low Power, Extended Refresh(标准或低功率,扩展刷新,256K x 4动态RAM) |

| MT4LC16M4T8TG-5 | DRAM |

| MT4LC16M4T8TG-5S | DRAM |

| MT4LC16M4T8TG-6 | DRAM |

| MT4LC16M4T8TG-6S | DRAM |

相关代理商/技术参数 |

参数描述 |

|---|---|

| MT4C4256-10 | 制造商:未知厂家 制造商全称:未知厂家 功能描述:256K X 4RAM(FAST PAGE MODE) |

| MT4C4256-12 | 制造商:未知厂家 制造商全称:未知厂家 功能描述:256K X 4RAM(FAST PAGE MODE) |

| MT4C425628 | 制造商:MICRON 功能描述:* |

| MT4C4256-6 | 制造商:MAJOR 功能描述: |

| MT4C4256-8 | 制造商:未知厂家 制造商全称:未知厂家 功能描述:256K X 4RAM(FAST PAGE MODE) |

发布紧急采购,3分钟左右您将得到回复。