- 您现在的位置:买卖IC网 > PDF目录385639 > MT4LC1M16E5 (Micron Technology, Inc.) EDO DRAM PDF资料下载

参数资料

| 型号: | MT4LC1M16E5 |

| 厂商: | Micron Technology, Inc. |

| 英文描述: | EDO DRAM |

| 中文描述: | EDO公司的DRAM |

| 文件页数: | 4/24页 |

| 文件大小: | 385K |

| 代理商: | MT4LC1M16E5 |

4

1 Meg x 16 EDO DRAM

D52_B.p65 – Rev. B; Pub. 3/01

Micron Technology, Inc., reserves the right to change products or specifications without notice.

2001, Micron Technology, Inc

16Mb: 1 MEG x16

EDO DRAM

STORED

DATA

1

1

0

1

1

1

1

1

RAS#

CASL#

WE#

X = NOT EFFECTIVE (DON'T CARE)

ADDRESS 1

ADDRESS 0

0

1

0

1

0

0

0

0

WORD WRITE

LOWER BYTE WRITE

CASH#

INPUT

DATA

0

0

1

0

0

0

0

0

1

0

1

0

1

1

1

1

X

X

X

X

X

X

X

X

INPUT

DATA

1

1

0

1

1

1

1

1

INPUT

DATA

STORED

DATA

1

1

0

1

1

1

1

1

INPUT

DATA

STORED

DATA

0

0

1

0

0

0

0

0

1

0

1

0

1

1

1

1

STORED

DATA

0

0

1

0

0

0

0

0

1

0

1

0

1

1

1

1

X

X

X

X

X

X

X

X

1

0

1

0

1

1

1

1

UPPER BYTE

(DQ8-DQ15)

OF WORD

LOWER BYTE

(DQ0-DQ7)

OF WORD

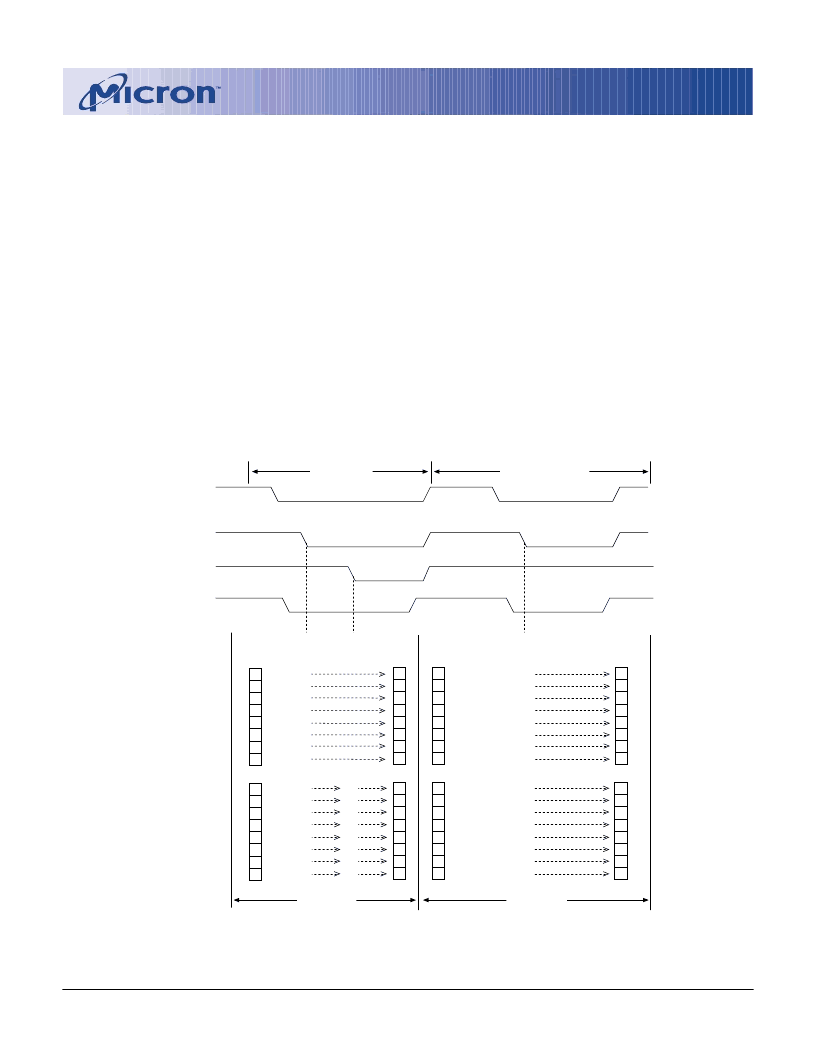

Figure 3

WORD and BY TE WRITE Example

However, an EARLY WRITE on one byte and a LATE

WRITE on the other byte, after a CAS# precharge has

been satisfied, are permissible.

DRAM REFRESH

Preserve correct memory cell data by maintaining

power and executing any RAS# cycle (READ, WRITE) or

RAS# REFRESH cycle (RAS#-ONLY, CBR or HIDDEN)

so that all 1,024 combinations of RAS# addresses are

executed within

t

REF (MAX), regardless of sequence.

The CBR, EXTENDED and SELF REFRESH cycles will

invoke the internal refresh counter for automatic RAS#

addressing.

An optional self refresh mode is available on the “S”

version. The self refresh feature is initiated by per-

forming a CBR REFRESH cycle and holding RAS# LOW

for the specified

t

RASS. The “S” option allows the user

the choice of a fully static, low-power data retention

mode or a dynamic refresh mode at the extended re-

fresh period of 128ms, or 125μs per row, when using a

distributed CBR REFRESH. This refresh rate can be

applied during normal operation, as well as during a

standby or battery backup mode.

The self refresh mode is terminated by driving

RAS# HIGH for a minimum time of

t

RPS. This delay

allows for the completion of any internal refresh cycles

that may be in process at the time of the RAS# LOW-to-

HIGH transition. If the DRAM controller uses a distrib-

uted refresh sequence, a burst refresh is not required

upon exiting self refresh. However, if the DRAM con-

troller utilizes a RAS#-ONLY or burst refresh sequence,

all 1,024 rows must be refreshed within the average

internal refresh rate, prior to the resumption of normal

operation.

STANDBY

Returning RAS# and CAS# HIGH terminates a

memory cycle and decreases chip current to a reduced

standby level. The chip is preconditioned for the next

cycle during the RAS# HIGH time.

相关PDF资料 |

PDF描述 |

|---|---|

| MT4C4256 | 256K x 4 DRAM Standard Or Low Power, Extended Refresh(标准或低功率,扩展刷新,256K x 4动态RAM) |

| MT4C4256L | 256K x 4 DRAM Standard Or Low Power, Extended Refresh(标准或低功率,扩展刷新,256K x 4动态RAM) |

| MT4LC16M4T8TG-5 | DRAM |

| MT4LC16M4T8TG-5S | DRAM |

| MT4LC16M4T8TG-6 | DRAM |

相关代理商/技术参数 |

参数描述 |

|---|---|

| MT4LC1M16E5DJ-5 | 制造商:MICRON 制造商全称:Micron Technology 功能描述:EDO DRAM |

| MT4LC1M16E5DJ-5S | 制造商:MICRON 制造商全称:Micron Technology 功能描述:EDO DRAM |

| MT4LC1M16E5DJ-6 | 制造商:MICRON 制造商全称:Micron Technology 功能描述:EDO DRAM |

| MT4LC1M16E5DJ-6S | 制造商:MICRON 制造商全称:Micron Technology 功能描述:EDO DRAM |

| MT4LC1M16E5TG-5 | 制造商:MICRON 制造商全称:Micron Technology 功能描述:EDO DRAM |

发布紧急采购,3分钟左右您将得到回复。