- 您现在的位置:买卖IC网 > PDF目录189414 > OR2T10A-4S352 (Electronic Theatre Controls, Inc.) Field-Programmable Gate Arrays PDF资料下载

参数资料

| 型号: | OR2T10A-4S352 |

| 厂商: | Electronic Theatre Controls, Inc. |

| 元件分类: | FPGA |

| 英文描述: | Field-Programmable Gate Arrays |

| 中文描述: | 现场可编程门阵列 |

| 文件页数: | 138/192页 |

| 文件大小: | 3148K |

| 代理商: | OR2T10A-4S352 |

第1页第2页第3页第4页第5页第6页第7页第8页第9页第10页第11页第12页第13页第14页第15页第16页第17页第18页第19页第20页第21页第22页第23页第24页第25页第26页第27页第28页第29页第30页第31页第32页第33页第34页第35页第36页第37页第38页第39页第40页第41页第42页第43页第44页第45页第46页第47页第48页第49页第50页第51页第52页第53页第54页第55页第56页第57页第58页第59页第60页第61页第62页第63页第64页第65页第66页第67页第68页第69页第70页第71页第72页第73页第74页第75页第76页第77页第78页第79页第80页第81页第82页第83页第84页第85页第86页第87页第88页第89页第90页第91页第92页第93页第94页第95页第96页第97页第98页第99页第100页第101页第102页第103页第104页第105页第106页第107页第108页第109页第110页第111页第112页第113页第114页第115页第116页第117页第118页第119页第120页第121页第122页第123页第124页第125页第126页第127页第128页第129页第130页第131页第132页第133页第134页第135页第136页第137页当前第138页第139页第140页第141页第142页第143页第144页第145页第146页第147页第148页第149页第150页第151页第152页第153页第154页第155页第156页第157页第158页第159页第160页第161页第162页第163页第164页第165页第166页第167页第168页第169页第170页第171页第172页第173页第174页第175页第176页第177页第178页第179页第180页第181页第182页第183页第184页第185页第186页第187页第188页第189页第190页第191页第192页

Lucent Technologies Inc.

5

Data Sheet

June 1999

ORCA Series 2 FPGAs

ORCA Foundry Development System

Overview

The

ORCA Foundry Development System interfaces to

front-end design entry tools and provides the tools to

produce a configured FPGA. In the design flow, the

user defines the functionality of the FPGA at two

points: at design entry and at the bit stream generation

stage.

Following design entry, the development system’s map,

place, and route tools translate the netlist into a routed

FPGA. Its bit stream generator is then used to generate

the configuration data which is loaded into the FPGA’s

internal configuration RAM. When using the bit stream

generator, the user selects options that affect the func-

tionality of the FPGA. Combined with the front-end

tools,

ORCA Foundry produces configuration data that

implements the various logic and routing options dis-

cussed in this data sheet.

Architecture

The

ORCA Series FPGA is comprised of two basic

elements: PLCs and PICs. Figure 1 shows an array of

programmable logic cells (PLCs) surrounded by pro-

grammable input/output cells (PICs). The Series 2 has

PLCs arranged in an array of 20 rows and 20 columns.

PICs are located on all four sides of the FPGA between

the PLCs and the IC edge.

The location of a PLC is indicated by its row and col-

umn so that a PLC in the second row and third column

is R2C3. PICs are indicated similarly, with PT (top) and

PB (bottom) designating rows and PL (left) and PR

(right) designating columns, followed by a number. The

routing resources and configuration RAM are not

shown, but the interquad routing blocks (hIQ, vIQ)

present in the Series 2 series are shown.

Each PIC contains the necessary I/O buffers to inter-

face to bond pads. The PICs also contain the routing

resources needed to connect signals from the bond

pads to/from PLCs. The PICs do not contain any user-

accessible logic elements, such as flip-flops.

Combinatorial logic is done in look-up tables (LUTs)

located in the PFU. The PFU can be used in different

modes to meet different logic requirements. The LUT’s

configurable medium-/large-grain architecture can be

used to implement from one to four combinatorial logic

functions. The flexibility of the LUT to handle wide input

functions, as well as multiple smaller input functions,

maximizes the gate count/PFU.

The LUTs can be programmed to operate in one of

three modes: combinatorial, ripple, or memory. In com-

binatorial mode, the LUTs can realize any four-, five-,

or six-input logic functions. In ripple mode, the high-

speed carry logic is used for arithmetic functions, the

new multiplier function, or the enhanced data path

functions. In memory mode, the LUTs can be used as a

16 x 4 read/write or read-only memory (asynchronous

mode or the new synchronous mode) or a new 16 x 2

dual-port memory.

Programmable Logic Cells

The programmable logic cell (PLC) consists of a pro-

grammable function unit (PFU) and routing resources.

All PLCs in the array are identical. The PFU, which con-

tains four LUTs and four latches/FFs for logic imple-

mentation, is discussed in the next section.

Programmable Function Unit

The PFUs are used for logic. Each PFU has 19 exter-

nal inputs and six outputs and can operate in several

modes. The functionality of the inputs and outputs

depends on the operating mode.

The PFU uses three input data buses (A[4:0], B[4:0],

WD[3:0]), four control inputs (C0, CK, CE, LSR), and a

carry input (CIN); the last is used for fast arithmetic

functions. There is a 5-bit output bus (O[4:0]) and a

carry-out (COUT).

5-2750(F).r3

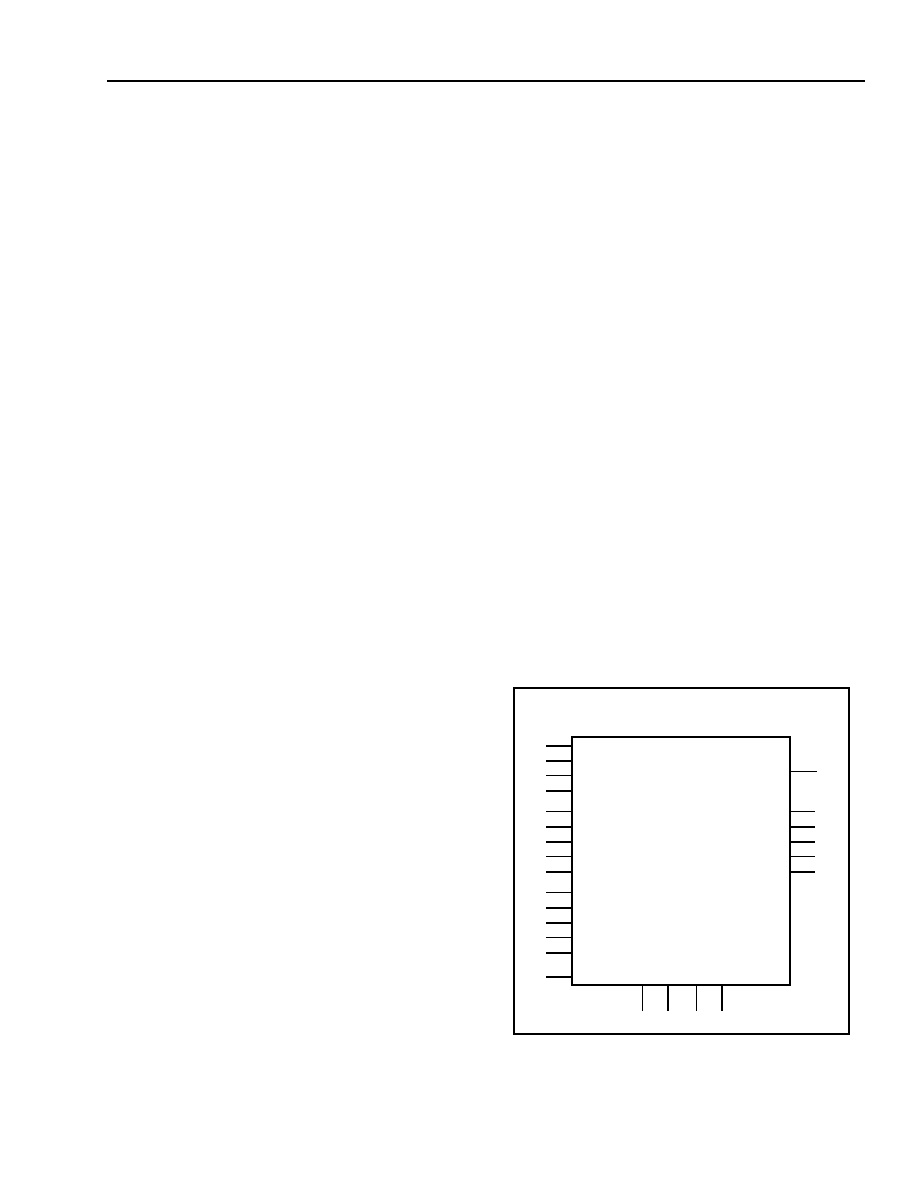

Figure 2. PFU Ports

PROGRAMMABLE LOGIC CELL (PLC)

WD3

WD2

WD1

WD0

A4

A3

A2

A1

A0

B4

B3

B2

B1

B0

O4

O3

O2

O1

O0

PROGRAMMABLE

FUNCTION UNIT

CE LSR

C0 CK

(ROUTING RESOURCES, CONFIGURATION RAM)

CIN

(PFU)

COUT

相关PDF资料 |

PDF描述 |

|---|---|

| OR2T10A-4S256I | Field-Programmable Gate Arrays |

| OR2T10A-4S256 | Field-Programmable Gate Arrays |

| OR2T10A-4S240I | Field-Programmable Gate Arrays |

| OR2T10A-4S240 | Field-Programmable Gate Arrays |

| OR2T10A-4S208I | Field-Programmable Gate Arrays |

相关代理商/技术参数 |

参数描述 |

|---|---|

| OR2T10A5BA256-DB | 功能描述:FPGA - 现场可编程门阵列 1024 LUT 244 I/O RoHS:否 制造商:Altera Corporation 系列:Cyclone V E 栅极数量: 逻辑块数量:943 内嵌式块RAM - EBR:1956 kbit 输入/输出端数量:128 最大工作频率:800 MHz 工作电源电压:1.1 V 最大工作温度:+ 70 C 安装风格:SMD/SMT 封装 / 箱体:FBGA-256 |

| OR2T10A5J160-DB | 功能描述:FPGA - 现场可编程门阵列 1024 LUT 244 I/O RoHS:否 制造商:Altera Corporation 系列:Cyclone V E 栅极数量: 逻辑块数量:943 内嵌式块RAM - EBR:1956 kbit 输入/输出端数量:128 最大工作频率:800 MHz 工作电源电压:1.1 V 最大工作温度:+ 70 C 安装风格:SMD/SMT 封装 / 箱体:FBGA-256 |

| OR2T10A5S208-DB | 功能描述:FPGA - 现场可编程门阵列 1024 LUT 244 I/O RoHS:否 制造商:Altera Corporation 系列:Cyclone V E 栅极数量: 逻辑块数量:943 内嵌式块RAM - EBR:1956 kbit 输入/输出端数量:128 最大工作频率:800 MHz 工作电源电压:1.1 V 最大工作温度:+ 70 C 安装风格:SMD/SMT 封装 / 箱体:FBGA-256 |

| OR2T10A5S240-DB | 功能描述:FPGA - 现场可编程门阵列 Use ECP/EC or XP RoHS:否 制造商:Altera Corporation 系列:Cyclone V E 栅极数量: 逻辑块数量:943 内嵌式块RAM - EBR:1956 kbit 输入/输出端数量:128 最大工作频率:800 MHz 工作电源电压:1.1 V 最大工作温度:+ 70 C 安装风格:SMD/SMT 封装 / 箱体:FBGA-256 |

| OR2T12A4BA256-DB | 制造商:Rochester Electronics LLC 功能描述:- Bulk 制造商:Lattice Semiconductor Corporation 功能描述: |

发布紧急采购,3分钟左右您将得到回复。