- 您现在的位置:买卖IC网 > Datasheet目录347 > P0304 (Terasic Technologies Inc)DE2-70 CALL FOR ACADEMIC PRICING Datasheet资料下载

参数资料

| 型号: | P0304 |

| 厂商: | Terasic Technologies Inc |

| 文件页数: | 48/93页 |

| 文件大小: | 0K |

| 描述: | DE2-70 CALL FOR ACADEMIC PRICING |

| 标准包装: | 1 |

| 类型: | FPGA |

| 适用于相关产品: | Cyclone II 2C70 |

| 所含物品: | DE2-70 板,电源,线缆,塑料盖和软件 |

| 配用: | P0033-ND - BOARD ADAPTER HSMC TO GPIO P0006-ND - BOARD ADAPTER THDB-SUM P0001-ND - MODULE DIGITAL CAMERA 5MP (D5M) P0307-ND - KIT DEV 4.3" LCD TOUCH PANEL |

| 相关产品: | 544-2147-ND - IC CYCLONE II FPGA 70K 896-FBGA 544-2146-ND - IC CYCLONE II FPGA 70K 896-FBGA 544-2145-ND - IC CYCLONE II FPGA 70K 896-FBGA 544-2144-ND - IC CYCLONE II FPGA 70K 896-FBGA 544-2143-ND - IC CYCLONE II FPGA 70K 672-FBGA 544-2142-ND - IC CYCLONE II FPGA 70K 672-FBGA 544-2141-ND - IC CYCLONE II FPGA 70K 672-FBGA 544-2140-ND - IC CYCLONE II FPGA 70K 672-FBGA 544-1696-ND - IC CYCLONE II FPGA 70K 896-FBGA 544-1695-ND - IC CYCLONE II FPGA 70K 896-FBGA 更多... |

| 其它名称: | DE2-70 |

第1页第2页第3页第4页第5页第6页第7页第8页第9页第10页第11页第12页第13页第14页第15页第16页第17页第18页第19页第20页第21页第22页第23页第24页第25页第26页第27页第28页第29页第30页第31页第32页第33页第34页第35页第36页第37页第38页第39页第40页第41页第42页第43页第44页第45页第46页第47页当前第48页第49页第50页第51页第52页第53页第54页第55页第56页第57页第58页第59页第60页第61页第62页第63页第64页第65页第66页第67页第68页第69页第70页第71页第72页第73页第74页第75页第76页第77页第78页第79页第80页第81页第82页第83页第84页第85页第86页第87页第88页第89页第90页第91页第92页第93页

�� ��

��

��

��DE2-70� User� Manual�

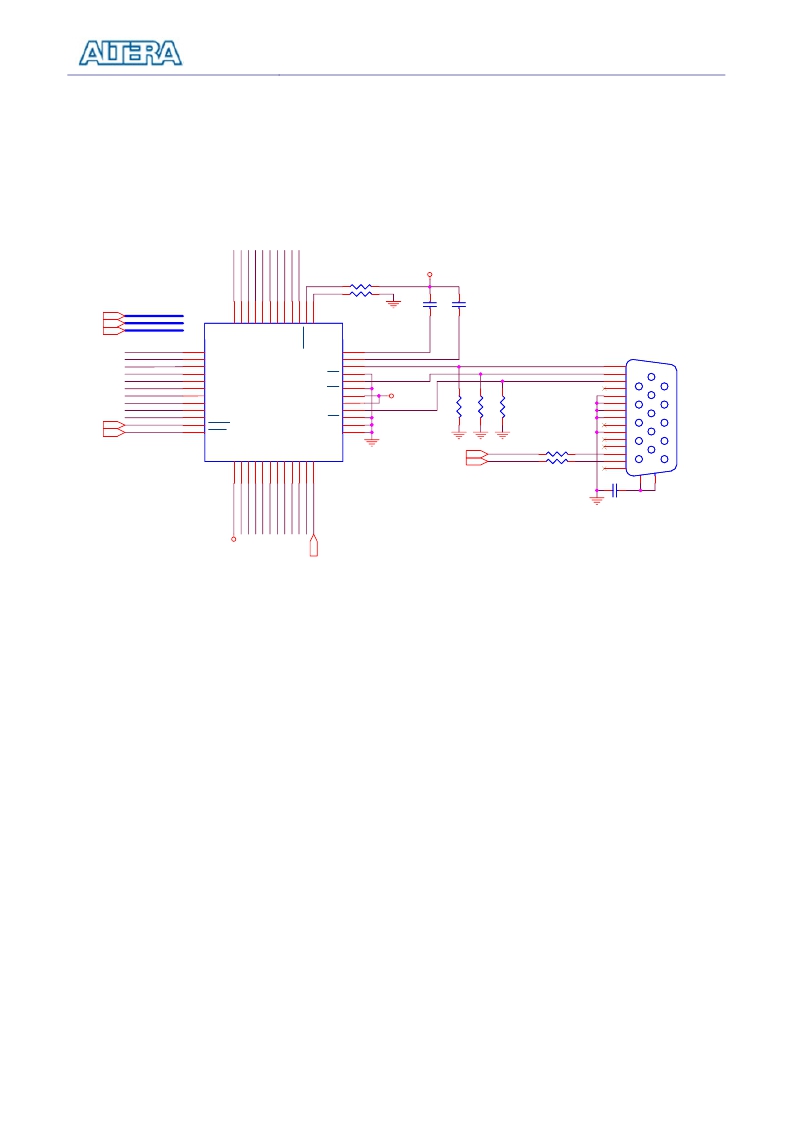

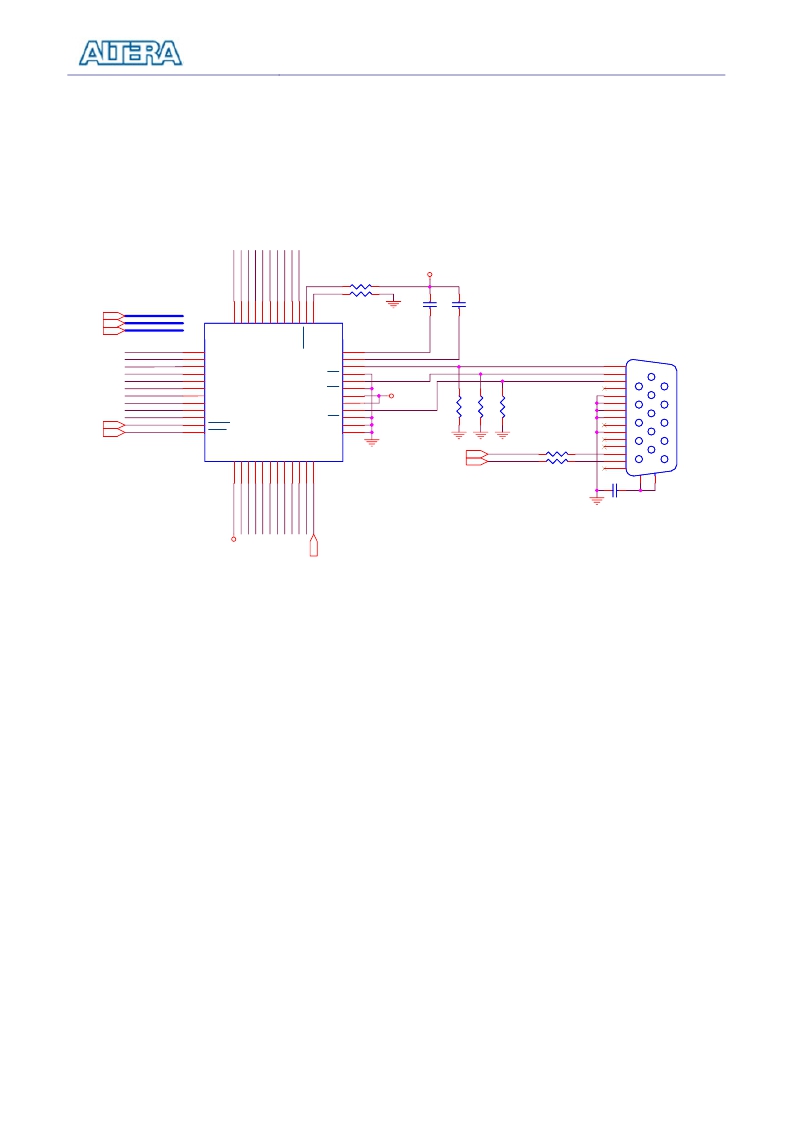

�5.7� Using� VGA�

�The� DE2-70� board� includes� a� 16-pin� D-SUB� connector� for� VGA� output.� The� VGA� synchronization�

�signals� are� provided� directly� from� the� Cyclone� II� FPGA,� and� the� Analog� Devices� ADV7123� triple�

�10-bit� high-speed� video� DAC� is� used� to� produce� the� analog� data� signals� (red,� green,� and� blue).� The�

�associated� schematic� is� given� in� Figure� 5.12� and� can� support� resolutions� of� up� to� 1600� x� 1200� pixels,�

�at� 100� MHz.�

�VGA_VCC33�

�R80�

�R81�

�4.7K�

�560�

�VGA_R[0..9]�

�VGA_G[0..9]�

�VGA_B[0..9]�

�U10�

�RSET�

�BC47�

�0.1u�

�BC48�

�0.1u�

�VGA_G0�

�VGA_G1�

�VGA_G2�

�VGA_G3�

�VGA_G4�

�VGA_G5�

�VGA_G6�

�VGA_G7�

�VGA_G8�

�VGA_G9�

�VGA_BLANK_n�

�VGA_SYNC_n�

�1�

�2�

�3�

�4�

�5�

�6�

�7�

�8�

�9�

�10�

�11�

�12�

�G0�

�G1�

�G2�

�G3�

�G4�

�G5�

�G6�

�G7�

�G8�

�G9�

�BLAN� K�

�SYNC�

�ADV7123�

�VREF�

�COMP�

�IOR�

�IOR�

�IOG�

�IOG�

�VAA�

�VAA�

�IOB�

�IOB�

�GND�

�GND�

�36�

�35�

�34�

�33�

�32�

�31�

�30�

�29�

�28�

�27�

�26�

�25�

�VGA_VCC33�

�R82�

�75�

�R83�

�75�

�R84�

�75�

�VGA_R�

�VGA_G�

�VGA_B�

�1�

�2�

�3�

�4�

�5�

�6�

�7�

�8�

�9�

�10�

�11�

�J7�

�1�

�6�

�11�

�12�

�VGA_HS�

�R85�

�47�

�13�

�VGA_VS�

�R86�

�47�

�14�

�15�

�5�

�10�

�15�

�VGA�

�BC49� 0.1u�

�VGA_VCC33�

�Figure� 5.12.� VGA� circuit� schematic.�

�The� timing� specification� for� VGA� synchronization� and� RGB� (red,� green,� blue)� data� can� be� found� on�

�various� educational� web� sites� (for� example,� search� for� “VGA� signal� timing”).� Figure� 5.13� illustrates�

�the� basic� timing� requirements� for� each� row� (horizontal)� that� is� displayed� on� a� VGA� monitor.� An�

�active-low� pulse� of� specific� duration� (time� a� in� the� figure)� is� applied� to� the� horizontal�

�synchronization� (� hsync� )� input� of� the� monitor,� which� signifies� the� end� of� one� row� of� data� and� the�

�start� of� the� next.� The� data� (RGB)� inputs� on� the� monitor� must� be� off� (driven� to� 0� V)� for� a� time� period�

�called� the� back� porch� (� b� )� after� the� hsync� pulse� occurs,� which� is� followed� by� the� display� interval� (� c� ).�

�During� the� data� display� interval� the� RGB� data� drives� each� pixel� in� turn� across� the� row� being�

�displayed.� Finally,� there� is� a� time� period� called� the� front� porch� (� d� )� where� the� RGB� signals� must�

�again� be� off� before� the� next� hsync� pulse� can� occur.� The� timing� of� the� vertical� synchronization� (� vsync� )�

�is� the� same� as� shown� in� Figure� 5.13,� except� that� a� vsync� pulse� signifies� the� end� of� one� frame� and� the�

�start� of� the� next,� and� the� data� refers� to� the� set� of� rows� in� the� frame� (horizontal� timing).� Table� 5.9� and�

�5.10� show,� for� different� resolutions,� the� durations� of� time� periods� a� ,� b� ,� c� ,� and� d� for� both� horizontal�

�and� vertical� timing.�

�Detailed� information� for� using� the� ADV7123� video� DAC� is� available� in� its� datasheet,� which� can� be�

�45�

�相关PDF资料 |

PDF描述 |

|---|---|

| P0305 | KIT MAX II MICRO |

| P0528 | BOARD DEV DE1 ALTERA |

| P100-001 | ADAPTER DB9F TO DB25M 1' |

| P2041RDB-PA | BOARD REFERENCE DESIGN P2041 |

| P25E-060S-EA | CONN SOCKET 60POS .050" GOLD |

相关代理商/技术参数 |

参数描述 |

|---|---|

| P0304U | 制造商:TECCOR 制造商全称:TECCOR 功能描述:solid state crowbar devices |

| P0304U_L | 制造商:LITTELFUSE 制造商全称:Littelfuse 功能描述:Mutiport SIDAtor |

| P0304UALRP | 功能描述:硅对称二端开关元件 50A 25/50V RoHS:否 制造商:Bourns 转折电流 VBO:40 V 最大转折电流 IBO:800 mA 不重复通态电流: 额定重复关闭状态电压 VDRM:25 V 关闭状态漏泄电流(在 VDRM IDRM 下): 保持电流(Ih 最大值):50 mA 开启状态电压:5 V 关闭状态电容 CO:120 pF 最大工作温度:+ 150 C 安装风格:SMD/SMT 封装 / 箱体:DO-214AA |

| P0304UALTP | 功能描述:硅对称二端开关元件 50A 25/50V RoHS:否 制造商:Bourns 转折电流 VBO:40 V 最大转折电流 IBO:800 mA 不重复通态电流: 额定重复关闭状态电压 VDRM:25 V 关闭状态漏泄电流(在 VDRM IDRM 下): 保持电流(Ih 最大值):50 mA 开启状态电压:5 V 关闭状态电容 CO:120 pF 最大工作温度:+ 150 C 安装风格:SMD/SMT 封装 / 箱体:DO-214AA |

| P0304UALXX | 制造商:LITTELFUSE 制造商全称:Littelfuse 功能描述:SIDACtor?? Multiport Series MS-013 are designed to protect baseband equipment |

发布紧急采购,3分钟左右您将得到回复。