- 您现在的位置:买卖IC网 > PDF目录367726 > P83C280 (NXP SEMICONDUCTORS) Microcontrollers for monitors with DDC interface, auto-sync detection and sync proc(带DDC接口,同步监测和同步处理的监视器微控制器) PDF资料下载

参数资料

| 型号: | P83C280 |

| 厂商: | NXP SEMICONDUCTORS |

| 元件分类: | 微控制器/微处理器 |

| 英文描述: | Microcontrollers for monitors with DDC interface, auto-sync detection and sync proc(带DDC接口,同步监测和同步处理的监视器微控制器) |

| 中文描述: | 8-BIT, MROM, 16 MHz, MICROCONTROLLER, PDIP42 |

| 封装: | 0.600 INCH, PLASTIC, SOT-270-1, SDIP-42 |

| 文件页数: | 42/84页 |

| 文件大小: | 420K |

| 代理商: | P83C280 |

第1页第2页第3页第4页第5页第6页第7页第8页第9页第10页第11页第12页第13页第14页第15页第16页第17页第18页第19页第20页第21页第22页第23页第24页第25页第26页第27页第28页第29页第30页第31页第32页第33页第34页第35页第36页第37页第38页第39页第40页第41页当前第42页第43页第44页第45页第46页第47页第48页第49页第50页第51页第52页第53页第54页第55页第56页第57页第58页第59页第60页第61页第62页第63页第64页第65页第66页第67页第68页第69页第70页第71页第72页第73页第74页第75页第76页第77页第78页第79页第80页第81页第82页第83页第84页

1997 Dec 12

42

Philips Semiconductors

Product specification

Microcontrollers for monitors with DDC

interface, auto-sync detection and sync proc.

P83Cx80; P87C380

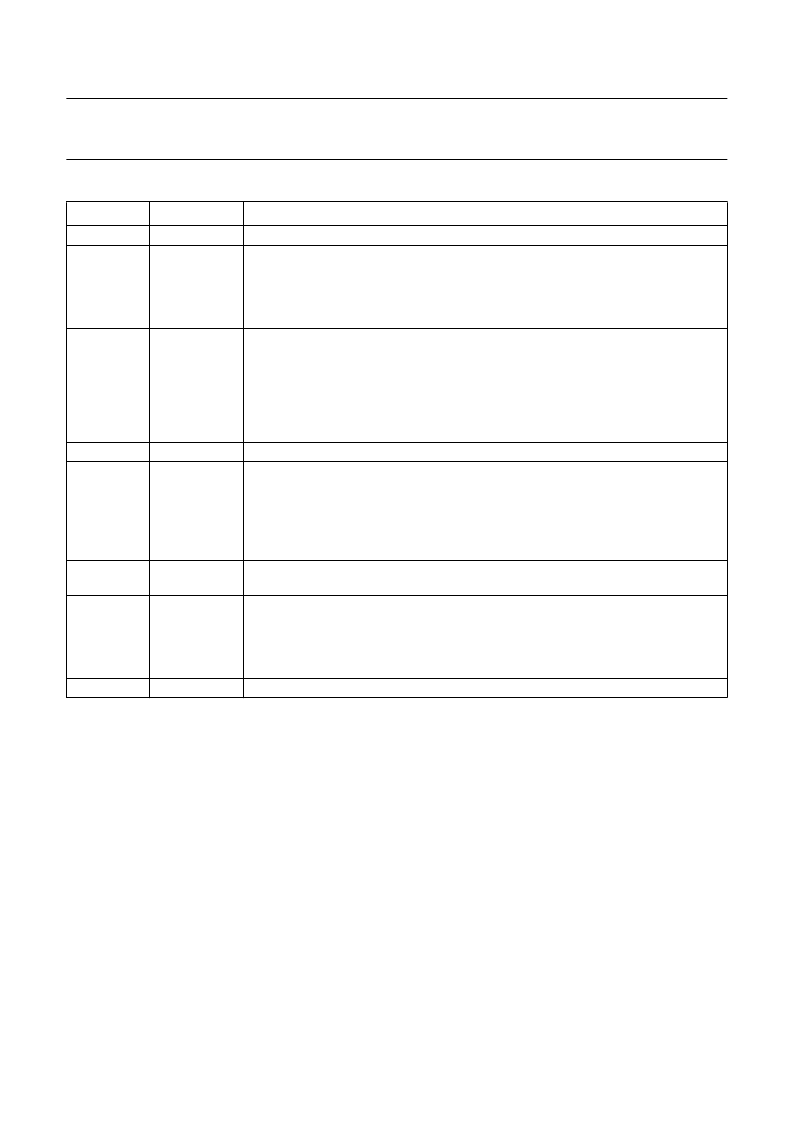

Table 37

Description of DDCCON bits

Note

1.

These bits are R/W.

BIT

SYMBOL

EX_DAT

DESCRIPTION

7

6

Reserved.

This bit defines the size of the EDID data. It is related to the function of the post

increment of the address pointer, DDCADR. When the upper limit is reached, the

address pointer will wrap around to 00H. If EX_DAT = 1, the data size is 256 bytes.

If EX_DAT = 0, the data size is 128 bytes; the addressing range for the EDID data

buffer is mapped from 0 to 127, the rest (128 to 255) can still be used by the system.

This bit indicates if the software/CPU is needed to take care of the operation of DDC1

protocol. If SWENB = 1, in DDC1 protocol, the CPU is interrupted during the period of

the 9th transmitting bit so that the software service routine can update the hold

register of the transmitter by moving new data from the appropriate area (it is not

necessary to be the RAM buffer). This transferring must be done within 40

μ

s.

If SWENB = 0, the hold register of the transmitter will be automatically updated from

the RAM buffer without the intervention of the CPU.

Reserved.

Interrupt request bit (002BH is assigned as the interrupt vector address). This bit is only

valid in DDC1 protocol while software handling is enabled (SWENB = 1). This bit is set

by hardware and should be cleared by software in an interrupt service routine. If DDC1

is fully under the hardware control (SWENB = 0), this bit can be ignored.

If DDC1_int = 1, interrupt request is pending. If DDC1_int = 0, there are no interrupt

request.

DDC1enable

(1)

DDC1 enable control bit. If DDC1enable = 1, DDC1 is enabled. If DDC1enable = 0,

DDC1 is disabled (the activity on VCLK is ignored).

SWH_int

(1)

Interrupt request bit (002BH is assigned as the interrupt vector address). This bit is

used to indicate that DDC interface switches from DDC1 to DDC2 (i.e. the

HIGH-to-LOW transition is observed on pin SCL1). This bit should be cleared by

software in an interrupt service routine. If SWH_int = 1, interrupt request is pending.

If SWH_int = 0, there is no interrupt request.

M0

(1)

DDC mode indication bit. If M0 = 0, DDC1 is set; if M0 = 1, DDC2 is set.

5

SWENB

4

3

DDC1_int

(1)

2

1

0

相关PDF资料 |

PDF描述 |

|---|---|

| P83C380 | Microcontrollers for monitors with DDC interface, auto-sync detection and sync proc(带DDC接口,同步监测和同步处理的监视器微控制器) |

| P87C380 | Microcontrollers for monitors with DDC interface, auto-sync detection and sync proc(带DDC接口,同步监测和同步处理的监视器微控制器) |

| P83C880 | Microcontrollers for monitors with DDC interface, auto-sync detection and sync proc(带DDC接口,同步监测和同步处理的监视器微控制器) |

| P83C180 | Microcontrollers for monitors with DDC interface, auto-sync detection and sync proc(带DDC接口,同步监测和同步处理的监视器微控制器) |

| P83C370AAR | Microcontrollers for PAL/SECAM TV with OSD and VST(带 OSD和 VST的在PAL/SECAM TV中应用的微控制器) |

相关代理商/技术参数 |

参数描述 |

|---|---|

| P83C366 | 制造商:PHILIPS 制造商全称:NXP Semiconductors 功能描述:Microcontrollers for PAL/SECAM TV with OSD and VST |

| P83C366BDA | 制造商:PHILIPS 制造商全称:NXP Semiconductors 功能描述:Microcontrollers for PAL/SECAM TV with OSD and VST |

| P83C366BDR | 制造商:PHILIPS 制造商全称:NXP Semiconductors 功能描述:Microcontrollers for PAL/SECAM TV with OSD and VST |

| P83C366CBP | 制造商:PHILIPS 制造商全称:NXP Semiconductors 功能描述:Microcontrollers for PAL/SECAM TV with OSD and VST |

| P83C370 | 制造商:PHILIPS 制造商全称:NXP Semiconductors 功能描述:Microcontrollers for NTSC TVs with On-Screen Display OSD and Closed Caption CC |

发布紧急采购,3分钟左右您将得到回复。