- 您现在的位置:买卖IC网 > PDF目录367726 > P83C280 (NXP SEMICONDUCTORS) Microcontrollers for monitors with DDC interface, auto-sync detection and sync proc(带DDC接口,同步监测和同步处理的监视器微控制器) PDF资料下载

参数资料

| 型号: | P83C280 |

| 厂商: | NXP SEMICONDUCTORS |

| 元件分类: | 微控制器/微处理器 |

| 英文描述: | Microcontrollers for monitors with DDC interface, auto-sync detection and sync proc(带DDC接口,同步监测和同步处理的监视器微控制器) |

| 中文描述: | 8-BIT, MROM, 16 MHz, MICROCONTROLLER, PDIP42 |

| 封装: | 0.600 INCH, PLASTIC, SOT-270-1, SDIP-42 |

| 文件页数: | 50/84页 |

| 文件大小: | 420K |

| 代理商: | P83C280 |

第1页第2页第3页第4页第5页第6页第7页第8页第9页第10页第11页第12页第13页第14页第15页第16页第17页第18页第19页第20页第21页第22页第23页第24页第25页第26页第27页第28页第29页第30页第31页第32页第33页第34页第35页第36页第37页第38页第39页第40页第41页第42页第43页第44页第45页第46页第47页第48页第49页当前第50页第51页第52页第53页第54页第55页第56页第57页第58页第59页第60页第61页第62页第63页第64页第65页第66页第67页第68页第69页第70页第71页第72页第73页第74页第75页第76页第77页第78页第79页第80页第81页第82页第83页第84页

1997 Dec 12

50

Philips Semiconductors

Product specification

Microcontrollers for monitors with DDC

interface, auto-sync detection and sync proc.

P83Cx80; P87C380

17.6

RAM buffer for the system and DDC application

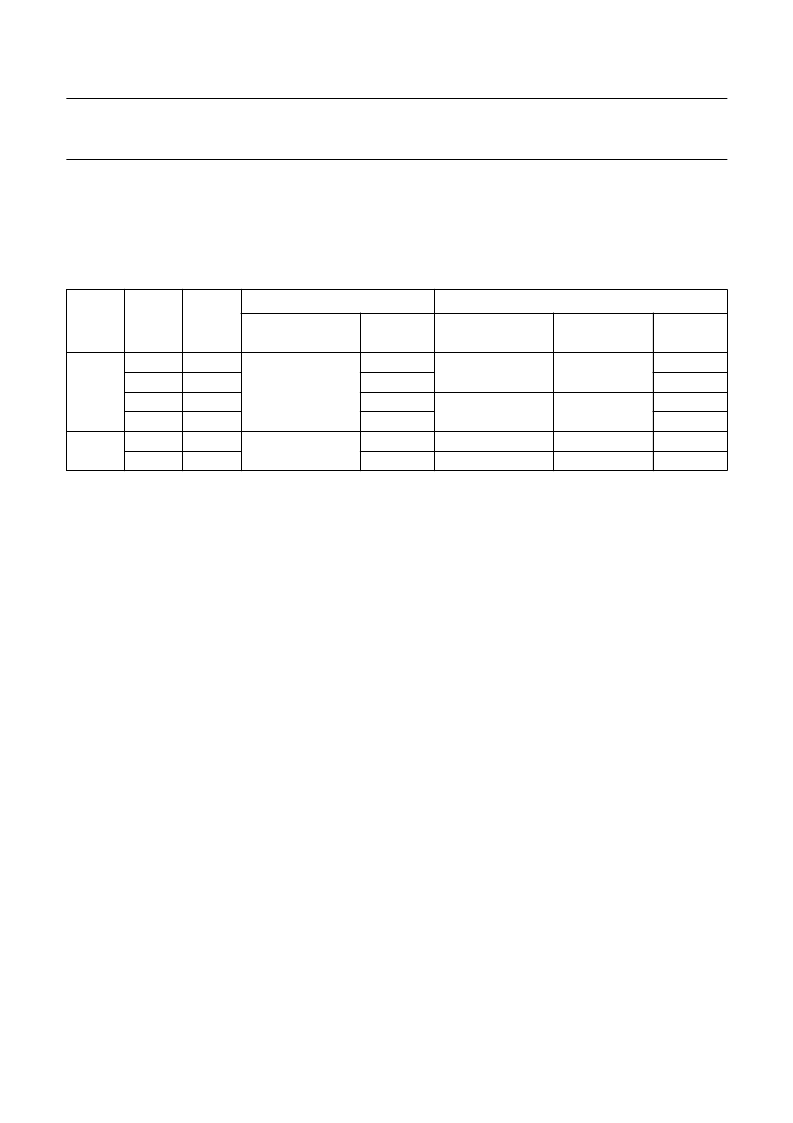

The architecture of the RAM buffer is set up in a flexible configuration to use the RAM resource to a maximum. In principle

the RAM buffer can be shared as system or DDC RAM buffer. The relationship among those applications is arranged as

shown in Table 42.

Table 42

Relation between system RAM and DDC RAM

Notes

1.

Read/write through MOVX instruction might conflict with the access from DDC1 hardware. So the access from CPU

by using MOVX instruction is forbidden.

READ/WRITE through DDCADR and RAMBUF registers has the conflicting problem also. Even the content of

DDCADR, which should be employed by DDC1 hardware, will be damaged. So it is inhibited to use this type of

access.

If DDCADR reaches 127 it will automatically wrap around to 0 after the access is done.

The access conflict can be avoided because DDC1 access is done by the interrupt service routine. However, the

EDID transferring from the RAM buffer should be finished within 40

μ

s.

If DDCADR reaches 255 it will automatically wrap around to 0 after the access is done.

2.

3.

4.

5.

18 I

2

C-BUS INTERFACE

The P83C880 has a software I

2

C-bus interface that can be used in master mode. Full details of the I

2

C-bus are given in

the 80C51 family “Data Handbook IC20”and/or the document “The I

2

C-bus and how to use it”(ordering number

9398 393 40011).

The I

2

C-bus interface lines SDA and SCL share the same pins as Port 1 lines P1.1 and P1.0 respectively; selection is

done via the S1E bit in SFR DFCON (address C0H).

MODE

EX_DAT SWENB

AUX RAM 0 TO 127

AUX RAM 128 TO 255

NORMALLY

RESERVED FOR

NOTE

NORMALLY

RESERVED FOR

AVAILABLE

FOR

NOTE

DDC1

0

0

1

1

0

1

0

1

0

1

1

1

DDC1 EDID data

1, 2 and 3

3 and 4

1 and 2

4

3

system access

2

1, 2 and 5

4 and 5

5

DDC1 EDID data

DDC2

DDC2 EDID data

DDC2 EDID data

system access

相关PDF资料 |

PDF描述 |

|---|---|

| P83C380 | Microcontrollers for monitors with DDC interface, auto-sync detection and sync proc(带DDC接口,同步监测和同步处理的监视器微控制器) |

| P87C380 | Microcontrollers for monitors with DDC interface, auto-sync detection and sync proc(带DDC接口,同步监测和同步处理的监视器微控制器) |

| P83C880 | Microcontrollers for monitors with DDC interface, auto-sync detection and sync proc(带DDC接口,同步监测和同步处理的监视器微控制器) |

| P83C180 | Microcontrollers for monitors with DDC interface, auto-sync detection and sync proc(带DDC接口,同步监测和同步处理的监视器微控制器) |

| P83C370AAR | Microcontrollers for PAL/SECAM TV with OSD and VST(带 OSD和 VST的在PAL/SECAM TV中应用的微控制器) |

相关代理商/技术参数 |

参数描述 |

|---|---|

| P83C366 | 制造商:PHILIPS 制造商全称:NXP Semiconductors 功能描述:Microcontrollers for PAL/SECAM TV with OSD and VST |

| P83C366BDA | 制造商:PHILIPS 制造商全称:NXP Semiconductors 功能描述:Microcontrollers for PAL/SECAM TV with OSD and VST |

| P83C366BDR | 制造商:PHILIPS 制造商全称:NXP Semiconductors 功能描述:Microcontrollers for PAL/SECAM TV with OSD and VST |

| P83C366CBP | 制造商:PHILIPS 制造商全称:NXP Semiconductors 功能描述:Microcontrollers for PAL/SECAM TV with OSD and VST |

| P83C370 | 制造商:PHILIPS 制造商全称:NXP Semiconductors 功能描述:Microcontrollers for NTSC TVs with On-Screen Display OSD and Closed Caption CC |

发布紧急采购,3分钟左右您将得到回复。