- 您现在的位置:买卖IC网 > PDF目录296796 > PCM9211PT (TEXAS INSTRUMENTS INC) DATACOM, TOKEN RING TRANSCEIVER, PQFP48 PDF资料下载

参数资料

| 型号: | PCM9211PT |

| 厂商: | TEXAS INSTRUMENTS INC |

| 元件分类: | 网络接口 |

| 英文描述: | DATACOM, TOKEN RING TRANSCEIVER, PQFP48 |

| 封装: | GREEN, PLASTIC, LQFP-48 |

| 文件页数: | 73/121页 |

| 文件大小: | 1219K |

| 代理商: | PCM9211PT |

第1页第2页第3页第4页第5页第6页第7页第8页第9页第10页第11页第12页第13页第14页第15页第16页第17页第18页第19页第20页第21页第22页第23页第24页第25页第26页第27页第28页第29页第30页第31页第32页第33页第34页第35页第36页第37页第38页第39页第40页第41页第42页第43页第44页第45页第46页第47页第48页第49页第50页第51页第52页第53页第54页第55页第56页第57页第58页第59页第60页第61页第62页第63页第64页第65页第66页第67页第68页第69页第70页第71页第72页当前第73页第74页第75页第76页第77页第78页第79页第80页第81页第82页第83页第84页第85页第86页第87页第88页第89页第90页第91页第92页第93页第94页第95页第96页第97页第98页第99页第100页第101页第102页第103页第104页第105页第106页第107页第108页第109页第110页第111页第112页第113页第114页第115页第116页第117页第118页第119页第120页第121页

MS

MC

MDI

ADR 6 ADR 5 ADR 4 ADR 3 ADR 2 ADR 1 ADR 0

D7

D6

D5

D4

D3

D2

D1

D0

DC

R /W

ADR 6

DC

“ 0”

MS

MC

MDI

ADR 6 ADR 5 ADR 4 ADR 3 ADR 2 ADR 1

DON ’T CARE

( DC)

ADR 0

R /W ADR 6

DC

“1 ”

MDO

D7

D6

D5

D4

D3

D2

D1

D0

“HI - Z ”

“HI -Z ”

www.ti.com

SBAS495 – JUNE 2010

Register Write Operation

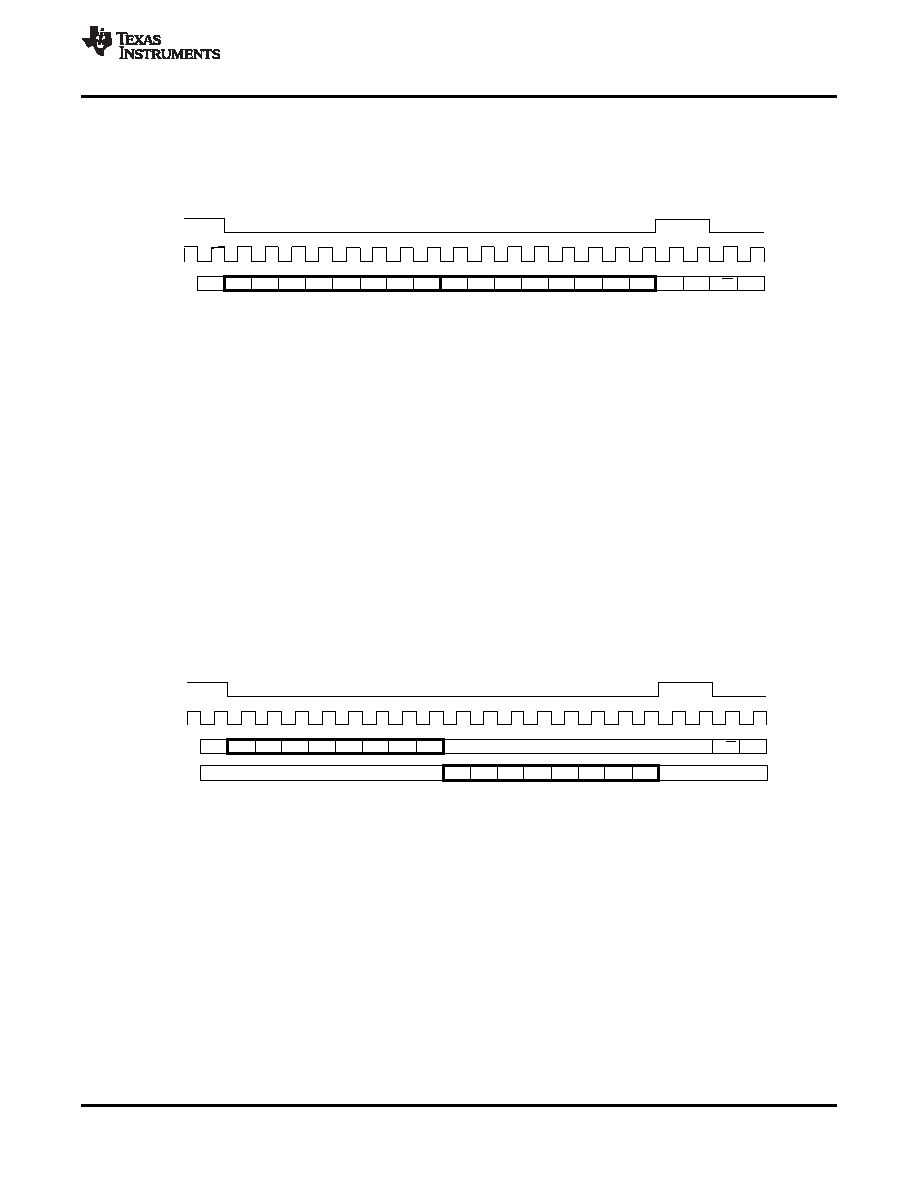

Figure 37 shows the functional timing diagram for a single write operation on the serial control port. MS is held at

'1' until a register must be written. To start the register write cycle, MS should be set to '0'. 16 clocks are then

provided on MC, corresponding to the 16 bits of the control data word on MDI. After the 16th clock cycle has

been completed, MS is set to '1' to latch the data into the indexed mode control register.

Figure 37. Register Write Operation

Channel status data are available from the Channel Status registers. To read the first 48 bits of the Channel

Status registers accurately, the read should be started 48fS after the start of the block. However, once MS is

pulled to '0', there are no time requirements in which to read the data because the registers are locked.

Both INT0 and INT1 can also be masked to highlight when the Channel Status has been updated. In many

cases, Channel Status does not change during playback (of a movie or music). Once the source changes,

though, the Channel Status changes. This change causes an interrupt, which can then be used to trigger the

DSP to read the Channel Status registers. The interrupt source is called OCSRNWx (Output Channel Status

Renewal).

The OCSRNWx flag can be held in the INTx register, or masked and brought out to the ERR/INT0 or

NPCM/INT1 pin.

Register Read Operation

Figure 38 shows the functional timing diagram for single read operations on the SPI serial control port. MS is

held high until a register is to be read. To start the register read cycle, MS is set to a low state. 16 clocks are

then provided on MC, corresponding to the first eight bits of the control data word on MDI, and second eight bits

of the read-back data word from MDO. After the 16th clock cycle has been completed, MS is set to high for next

write or read operation. MDO remains in a Hi-Z (or high impedance) state except for a period of eight MC clocks

for actual data transfer.

Figure 38. Register Read Operation

Copyright 2010, Texas Instruments Incorporated

55

Product Folder Link(s): PCM9211

相关PDF资料 |

PDF描述 |

|---|---|

| PCN11MF | STRIP TERMINAL BLOCK, 1 DECK |

| PCN12E-32S-2.54DSA | 32 CONTACT(S), FEMALE, STRAIGHT TWO PART EURO CONNECTOR, SOLDER, SOCKET |

| PCN12E-44S-2.54DSA | 44 CONTACT(S), FEMALE, STRAIGHT TWO PART EURO CONNECTOR, SOLDER, SOCKET |

| PCN12E-50S-2.54DSA | 50 CONTACT(S), FEMALE, STRAIGHT TWO PART EURO CONNECTOR, SOLDER, SOCKET |

| PCR-E68LMD | 68 CONTACT(S), MALE, RIGHT ANGLE TELECOM AND DATACOM CONNECTOR, SOLDER |

相关代理商/技术参数 |

参数描述 |

|---|---|

| PCM9211PTR | 功能描述:音频发送器、接收器、收发器 216kHz Dig Aud Inter face Transceiver RoHS:否 制造商:Cirrus Logic 工作电源电压:3.3 V, 5 V 电源电流:11.8 mA 通道数量:1 最大工作温度:+ 70 C 接口类型:I2C, SPI 安装风格:SMD/SMT 封装 / 箱体:TSSOP-28 封装: |

| PCM-93 | 功能描述:电线鉴定 Pre-Printed WM Card, Vinyl Cloth, .22" W RoHS:否 制造商:TE Connectivity / Q-Cees 产品:Labels and Signs 类型: 材料:Vinyl 颜色:Blue 宽度:0.625 in 长度:1 in |

| PCM-9342 | 制造商:ADVANTECH 制造商全称:Advantech Co., Ltd. 功能描述:X86 SoC 3.5" SBC with VGA, LCD, LAN, USB, SATA, CF, PC/104 |

| PCM-9342F-64A1E | 制造商:ADVANTECH 制造商全称:Advantech Co., Ltd. 功能描述:X86 SoC 3.5" SBC with VGA, LCD, LAN, USB, SATA, CF, PC/104 |

| PCM-9342FZ2-64A1E | 制造商:ADVANTECH 制造商全称:Advantech Co., Ltd. 功能描述:X86 SoC 3.5" SBC with VGA, LCD, LAN, USB, SATA, CF, PC/104 |

发布紧急采购,3分钟左右您将得到回复。