- 您现在的位置:买卖IC网 > PDF目录296796 > PCM9211PT (TEXAS INSTRUMENTS INC) DATACOM, TOKEN RING TRANSCEIVER, PQFP48 PDF资料下载

参数资料

| 型号: | PCM9211PT |

| 厂商: | TEXAS INSTRUMENTS INC |

| 元件分类: | 网络接口 |

| 英文描述: | DATACOM, TOKEN RING TRANSCEIVER, PQFP48 |

| 封装: | GREEN, PLASTIC, LQFP-48 |

| 文件页数: | 80/121页 |

| 文件大小: | 1219K |

| 代理商: | PCM9211PT |

第1页第2页第3页第4页第5页第6页第7页第8页第9页第10页第11页第12页第13页第14页第15页第16页第17页第18页第19页第20页第21页第22页第23页第24页第25页第26页第27页第28页第29页第30页第31页第32页第33页第34页第35页第36页第37页第38页第39页第40页第41页第42页第43页第44页第45页第46页第47页第48页第49页第50页第51页第52页第53页第54页第55页第56页第57页第58页第59页第60页第61页第62页第63页第64页第65页第66页第67页第68页第69页第70页第71页第72页第73页第74页第75页第76页第77页第78页第79页当前第80页第81页第82页第83页第84页第85页第86页第87页第88页第89页第90页第91页第92页第93页第94页第95页第96页第97页第98页第99页第100页第101页第102页第103页第104页第105页第106页第107页第108页第109页第110页第111页第112页第113页第114页第115页第116页第117页第118页第119页第120页第121页

www.ti.com

SBAS495 – JUNE 2010

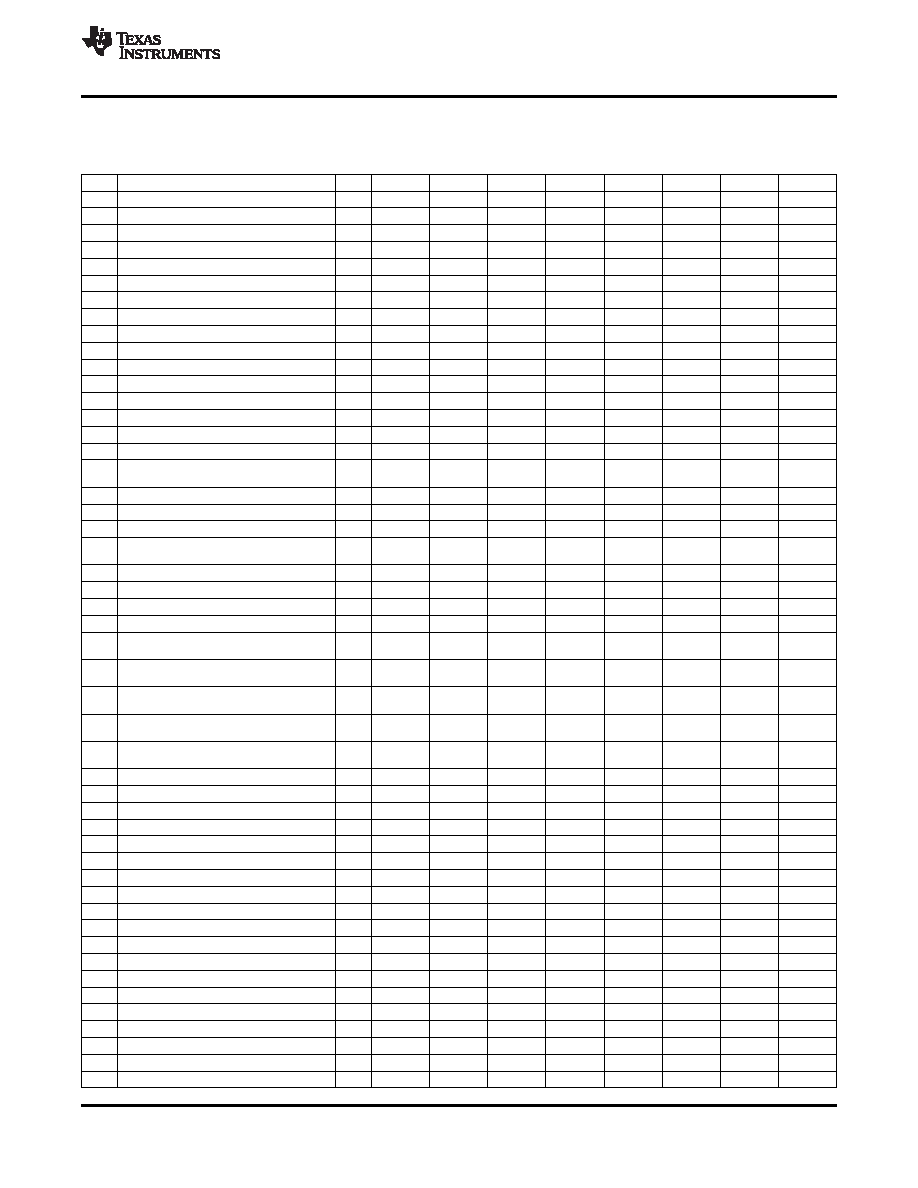

REGISTER INFORMATION

Table 35. REGISTER MAP

ADR

REGISTER DESCRIPTION

R/W

B7

B6

B5

B4

B3

B2

B1

B0

20h

ERROR Output Condition and Shared Port Settings

R/W

RSV

ERRCON

MCHR

RSV

ERRHZ

ERRSEL

NPCMHZ

NPCMSEL

21h

DIR Initial Settings 1/3

R/W

RSV

RXFSRNG

RSV

22h

DIR Initial Settings 2/3

R/W

RSV

CLKSTCON

RSV

CLKSTP

RSV

RXVDLY

23h

DIR Initial Settings 3/3

R/W

RSV

XTIWT1

XTIWT0

PRTPRO1

PRTPRO0

ERRWT1

ERRWT0

24h

Oscillation Circuit Control

R/W

OSCAUTO

RSV

XMCKEN

XMCKDIV1

XMCKDIV0

RSV

25h

ERROR Cause Setting

R/W

RSV

EFSCHG

EFSLMT

ENPCM

EVALID

EPARITY

EUNLOCK

26h

AUTO Source Selector Cause Setting

R/W

ACKSL

AERROR

RSV

AFSLMT

ANPCM

AVALID

RSV

AUNLOCK

27h

DIR Acceptable fS Range Setting and Mask

R/W

MSK128

MSK64

RSV

NOMLMT

HILMT1

HILMT0

LOLMT1

LOLMT0

28h

Non-PCM Definition Setting

R/W

RSV

CS1BPLS

NPCMP

RSV

DTSCD

PAPB

CSBIT1

29h

DTS CD/LD Detection Setting

R/W

RSV

DTS16

DTS14

DTSPRD1

DTSPRD0

2Ah

INT0 Output Cause Mask Setting

R/W

MERROR0

MNPCM0

MEMPHF0

MDTSCD0

MCSRNW0

MPCRNW0

MFSCHG0

RSV

2Bh

INT1 Output Cause Mask Setting

R/W

MERROR1

MNPCM1

MEMPHF1

MDTSCD1

MCSRNW1

MPCRNW1

MFSCHG1

MADLVL1

2Ch

INT0 Output Register

R

OERROR0

ONPCM0

OEMPHF0

ODTSCD0

OCSRNW0

OPCRNW0

OFSCHG0

RSV

2Dh

INT1 Output Register

R

OERROR1

ONPCM1

OEMPHF1

ODTSCD1

OCSRNW1

OPCRNW1

OFSCHG1

OADLVL1

2Eh

INT0, INT1 Output Polarity Setting

R/W

RSV

INT1P

RSV

ADLVLTH1

ADLVLTH0

INT0P

RSV

2Fh

DIR Output Data Format

R/W

RSV

RXFMT2

RXFMT1

RXFMT0

PSCKAUT

30h

DIR Recovered System Clock Ratio Setting

R/W

RSV

PSCK2

PSCK1

PSCK0

O

31h

XTI Source Clock Frequency Setting

R/W

RSV

XSCK1

XSCK0

XBCK1

XBCK0

XLRCK1

XLRCK0

32h

DIR Source, Sec. Bit/LR Clock Frequency Setting

R/W

RSV

PSBCK2

PSBCK1

PSBCK0

RSV

PSLRCK2

PSLRCK1

PSLRCK0

33h

XTI Source, Sec. Bit/LR Clock Frequency Setting

R/W

RSV

XSBCK2

XSBCK1

XSBCK0

RSV

XSLRCK2

XSLRCK1

XSLRCK0

DIR Input Biphase Source Select, Coax Amp.

34h

R/W

RX0DIS

RX1DIS

RSV

RXSEL3

RXSEL2

RXSEL1

RXSEL0

Control

35h

RECOUT0 Output Biphase Source Select

R/W

RSV

MPO0MUT

RO0SEL3

RO0SEL2

RO0SEL1

RO0SEL0

36h

RECOUT1 Output Biphase Source Select

R/W

RSV

MPO1MUT

RO1SEL3

RO1SEL2

RO1SEL1

RO1SEL0

37h

Port fS Calculator Measurement Target Setting

R/W

RSV

PFSTGT2

PFSTGT1

PFSTGT0

38h

Port fS Calculator Result Output

R

PFSST

PFSPO2

PFSPO1

PFSPO0

PFSOUT3

PFSOUT2

PFSOUT1

PFSOUT0

Incoming Biphase Information and Calculated fS

39h

R

SFSST

SCSBIT1

RSV

SFSOUT3

SFSOUT2

SFSOUT1

SFSOUT0

Output

PC Buffer Byte0 (Burst Preamble PC Output

3Ah

R

PC7

PC6

PC5

PC4

PC3

PC2

PC1

PC0

Register)

PC Buffer Byte1 (Burst Preamble PC Output

3Bh

R

PC15

PC14

PC13

PC12

PC11

PC10

PC9

PC8

Register)

PD Buffer Byte0 (Burst Preamble PD Output

3Ch

R

PD7

PD6

PD5

PD4

PD3

PD2

PD1

PD0

Register)

PD Buffer Byte1 (Burst Preamble PD Output

3Dh

R

PD15

PD14

PD13

PD12

PD11

PD10

PD9

PD8

Register)

40h

System Reset Control

R/W

MRST

SRST

ADDIS

RXDIS

RSV

TXDIS

XODIS

42h

ADC Function Control 1/3

R/W

RSV

ADCKOUT

ADDTRX7

ADFSLMT

ADCLK2

ADCLK1

ADCLK0

46h

ADC L-ch, digital ATT control

R/W

ADATTL7

ADATTL6

ADATTL5

ADATTL4

ADATTL3

ADATTL2

ADATTL1

ADATTL0

47h

ADC R-ch, digital ATT control

R/W

ADATTR7

ADATTR6

ADATTR5

ADATTR4

ADATTR3

ADATTR2

ADATTR1

ADATTR0

48h

ADC Function Control 2/3

R/W

RSV

ADIFMD2

ADIFMD1

ADIFMD0

RSV

ADFMT1

ADFMT0

49h

ADC Function Control 3/3

R/W

RSV

ADZCDD

ADBYP

ADPHSE

ADMUTR

ADMUTL

5Ah

DIR Channel Status Data Buffer 1/6

R

RXCS7

RXCS6

RXCS5

RXCS4

RXCS3

RXCS2

RXCS1

RXCS0

5Bh

DIR Channel Status Data Buffer 2/6

R

RXCS15

RXCS14

RXCS13

RXCS12

RXCS11

RXCS10

RXCS9

RXCS8

5Ch

DIR Channel Status Data Buffer 3/6

R

RXCS23

RXCS22

RXCS21

RXCS20

RXCS19

RXCS18

RXCS17

RXCS16

5Dh

DIR Channel Status Data Buffer 4/6

R

RXCS31

RXCS30

RXCS29

RXCS28

EXCS27

RXCS26

RXCS25

RXCS24

5Eh

DIR Channel Status Data Buffer 5/6

R

RXCS39

RXCS38

RXCS37

RXCS36

RXCS35

RXCS34

RXCS33

RXCS32

5Fh

DIR Channel Status Data Buffer 6/6

R

RXCS47

RXCS46

RXCS45

RXCS44

RXCS43

RXCS42

RXCS41

RXCS40

60h

DIT Function Control 1/3

R/W

RSV

TXSSRC2

TXSSRC1

TXSSRC0

RSV

TXPSRC2

TXPSRC1

TXPSRC0

61h

DIT Function Control 2/3

R/W

RSV

TXSCK2

TXSCK1

TXSCK0

RSV

TXFMT1

TXFMT0

62h

DIT Function Control 3/3

R/W

RSV

TXDMUT

RSV

TXVFLG

RSV

63h

DIT Channel Status Data Buffer 1/6

R/W

TXCS7

TXCS6

TXCS5

TXCS4

TXCS3

TXCS2

TXCS1

TXCS0

64h

DIT Channel Status Data Buffer 2/6

R/W

TXCS15

TXCS14

TXCS13

TXCS12

TXCS11

TXCS10

TXCS9

TXCS8

65h

DIT Channel Status Data Buffer 3/6

R/W

TXCS23

TXCS22

TXCS21

TXCS20

TXCS19

TXCS18

TXCS17

TXCS16

66h

DIT Channel Status Data Buffer 4/6

R/W

TXCS31

TXCS30

TXCS29

TXCS28

TXCS27

TXCS26

TXCS25

TXCS24

Copyright 2010, Texas Instruments Incorporated

61

Product Folder Link(s): PCM9211

相关PDF资料 |

PDF描述 |

|---|---|

| PCN11MF | STRIP TERMINAL BLOCK, 1 DECK |

| PCN12E-32S-2.54DSA | 32 CONTACT(S), FEMALE, STRAIGHT TWO PART EURO CONNECTOR, SOLDER, SOCKET |

| PCN12E-44S-2.54DSA | 44 CONTACT(S), FEMALE, STRAIGHT TWO PART EURO CONNECTOR, SOLDER, SOCKET |

| PCN12E-50S-2.54DSA | 50 CONTACT(S), FEMALE, STRAIGHT TWO PART EURO CONNECTOR, SOLDER, SOCKET |

| PCR-E68LMD | 68 CONTACT(S), MALE, RIGHT ANGLE TELECOM AND DATACOM CONNECTOR, SOLDER |

相关代理商/技术参数 |

参数描述 |

|---|---|

| PCM9211PTR | 功能描述:音频发送器、接收器、收发器 216kHz Dig Aud Inter face Transceiver RoHS:否 制造商:Cirrus Logic 工作电源电压:3.3 V, 5 V 电源电流:11.8 mA 通道数量:1 最大工作温度:+ 70 C 接口类型:I2C, SPI 安装风格:SMD/SMT 封装 / 箱体:TSSOP-28 封装: |

| PCM-93 | 功能描述:电线鉴定 Pre-Printed WM Card, Vinyl Cloth, .22" W RoHS:否 制造商:TE Connectivity / Q-Cees 产品:Labels and Signs 类型: 材料:Vinyl 颜色:Blue 宽度:0.625 in 长度:1 in |

| PCM-9342 | 制造商:ADVANTECH 制造商全称:Advantech Co., Ltd. 功能描述:X86 SoC 3.5" SBC with VGA, LCD, LAN, USB, SATA, CF, PC/104 |

| PCM-9342F-64A1E | 制造商:ADVANTECH 制造商全称:Advantech Co., Ltd. 功能描述:X86 SoC 3.5" SBC with VGA, LCD, LAN, USB, SATA, CF, PC/104 |

| PCM-9342FZ2-64A1E | 制造商:ADVANTECH 制造商全称:Advantech Co., Ltd. 功能描述:X86 SoC 3.5" SBC with VGA, LCD, LAN, USB, SATA, CF, PC/104 |

发布紧急采购,3分钟左右您将得到回复。