- 您现在的位置:买卖IC网 > PDF目录378049 > PEF2080 (SIEMENS AG) S/T Bus Interface Circuit(SBC) PDF资料下载

参数资料

| 型号: | PEF2080 |

| 厂商: | SIEMENS AG |

| 英文描述: | S/T Bus Interface Circuit(SBC) |

| 中文描述: | S / T的总线接口电路(SBC)的 |

| 文件页数: | 59/74页 |

| 文件大小: | 2620K |

| 代理商: | PEF2080 |

第1页第2页第3页第4页第5页第6页第7页第8页第9页第10页第11页第12页第13页第14页第15页第16页第17页第18页第19页第20页第21页第22页第23页第24页第25页第26页第27页第28页第29页第30页第31页第32页第33页第34页第35页第36页第37页第38页第39页第40页第41页第42页第43页第44页第45页第46页第47页第48页第49页第50页第51页第52页第53页第54页第55页第56页第57页第58页当前第59页第60页第61页第62页第63页第64页第65页第66页第67页第68页第69页第70页第71页第72页第73页第74页

Semiconductor Group

60

Electrical Characteristics

AC Characteristics

T

A

= 0 to 70 C,

V

DD

= 5 V

±

5 % for PEB 2080

T

A

= – 40 to 85 C,

V

DD

= 5 V

±

5 % for PEF 2080

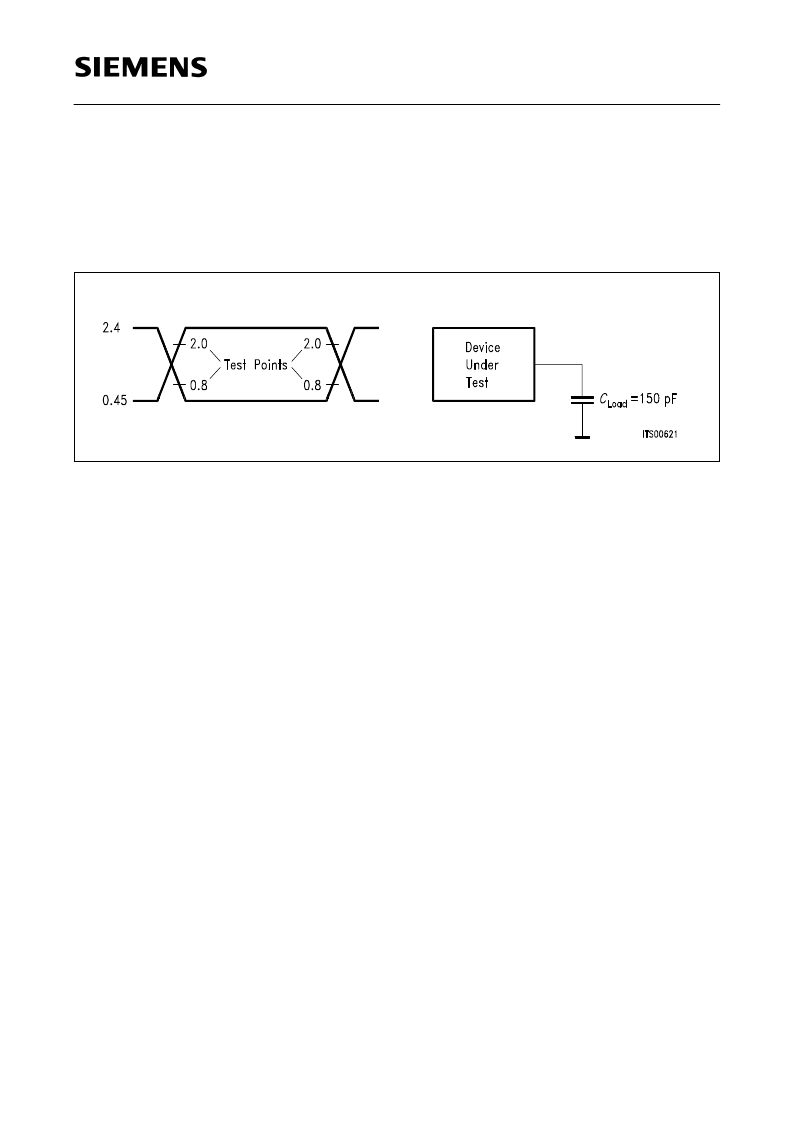

The AC testing input/output waveform is shown below.

Figure 32

Input / Output Waveform for AC Test

Jitter

In TE mode, the timing extraction jitter of the SBC conforms to CCITT Recommendation I.430

(– 7 % to + 7 % of the S-interface bit period). In the NT and LT-S applications, the clock input DCL

is used as reference clock to provide the 192-kHz clock for the S line interface. In the case of a

plesiochronous 7.68-MHz clock generated by an oscillator, the clock DCL should have a jitter of less

than 100 ns peak-to-peak. (In the case of a zero input jitter on DCL, SBC generates at most 130 ns

“self-jitter” on S interface.) In the case of a synchronous (fixed divider ratio of 15 between XTAL1

and DCL) 7.68-MHZ clock (input XTAL1), the SBC transfers the input jitter of XTAL1, DCL and FSC

to the S interface. The maximum jitter of the NT/LT-S output is limited to 260 ns peak-to-peak

(CCITT I.430).

Clock Timing

The clocks in the different operating modes are summarized in

table 7

, with duty ratios. Clock CP

is phase-locked to the receive S signal, and is derived using the internal DPLL and the

7.68 MHz

±

100 ppm crystal (TE and LT-T). A phase tracking of CP with respect to “S” is performed

once in 250

μ

s. As a consequence of this DPLL tracking, the high state of CP may be either reduced

or extended by one 7.68 MHz period (CP duty ratio 2:2 or 4:2 instead of 3:2) once every 250

μ

s.

Since DCL and FSC are derived from CP (TE mode), the high state (FSC) or the high or low state

(DCL) may likewise be reduced or extended by the same amount once every 250

μ

s. (The phase

adjustment may take place either in the sixth, seventh or eighth CP cycle counting from the

beginning of an IOM frame in TE).

The phase relationships of the auxiliary clocks are shown in

figure 29

.

相关PDF资料 |

PDF描述 |

|---|---|

| PEF22554 | Ultraframer DS3/E3/DS2/E2/DS1/E1/DS0 |

| PEF22554E | Ultraframer DS3/E3/DS2/E2/DS1/E1/DS0 |

| PEF22554HT | Ultraframer DS3/E3/DS2/E2/DS1/E1/DS0 |

| PEF2256 | Ultraframer DS3/E3/DS2/E2/DS1/E1/DS0 |

| PEF2256E | Ultraframer DS3/E3/DS2/E2/DS1/E1/DS0 |

相关代理商/技术参数 |

参数描述 |

|---|---|

| PEF2080-N | 制造商:INFINEON 制造商全称:Infineon Technologies AG 功能描述:S/T Bus Interface Circuit(SBC) |

| PEF2091 | 制造商:INFINEON 制造商全称:Infineon Technologies AG 功能描述:ICs for Communications(ISDN Echocancellation Circuit) |

| PEF2091F | 制造商:未知厂家 制造商全称:未知厂家 功能描述:?ISDN Echocancellation Circuit - 2B1Q Code? |

| PEF2091FV5.3 | 制造商:INFINEON 制造商全称:Infineon Technologies AG 功能描述:ICs for Communications(ISDN Echocancellation Circuit) |

| PEF2091HV5.3 | 制造商:INFINEON 制造商全称:Infineon Technologies AG 功能描述:ICs for Communications(ISDN Echocancellation Circuit) |

发布紧急采购,3分钟左右您将得到回复。