- 您现在的位置:买卖IC网 > PDF目录370013 > PowerNP NPe405L (IBM Microeletronics) 32-Bit Embedded Processor(32位嵌入式处理器) PDF资料下载

参数资料

| 型号: | PowerNP NPe405L |

| 厂商: | IBM Microeletronics |

| 英文描述: | 32-Bit Embedded Processor(32位嵌入式处理器) |

| 中文描述: | 32位嵌入式处理器(32位嵌入式处理器) |

| 文件页数: | 30/48页 |

| 文件大小: | 741K |

| 代理商: | POWERNP NPE405L |

第1页第2页第3页第4页第5页第6页第7页第8页第9页第10页第11页第12页第13页第14页第15页第16页第17页第18页第19页第20页第21页第22页第23页第24页第25页第26页第27页第28页第29页当前第30页第31页第32页第33页第34页第35页第36页第37页第38页第39页第40页第41页第42页第43页第44页第45页第46页第47页第48页

Advance Information

PowerNP

TM

NPe405L Embedded Processor Data Sheet

30

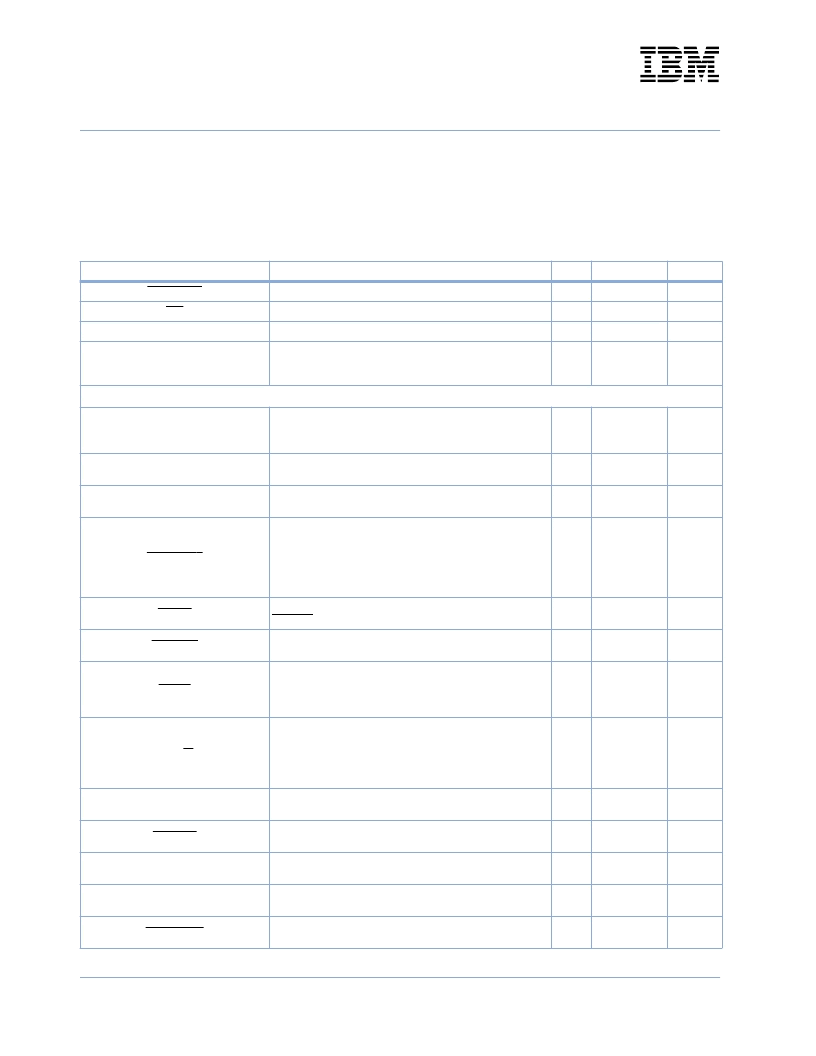

BankSel0:3

Select up to four external SDRAM banks.

O

3.3V LVTTL

WE

Write Enable.

O

3.3V LVTTL

ClkEn0:1

SDRAM Clock Enable.

O

3.3V LVTTL

MemClkOut0:1

Two copies of an SDRAM clock allows, in some cases,

glueless SDRAM attachment without requiring this signal

to be repowered by a PLL or zero-delay buffer.

O

3.3V LVTTL

External Slave Peripheral Interface

PerData0:15

Peripheral data bus used by NPe405L.

Note:

PerData00 is the most significant bit (msb) on this

bus.

I/O

5V tolerant

3.3V LVTTL

1

PerAddr4:31

Peripheral Address bus used by NPe405L.

O

5V tolerant

3.3V LVTTL

PerPar0:1

Peripheral byte parity signals.

I/O

5V tolerant

3.3V LVTTL

1

PerWBE0:1

As outputs, these pins can act as byte-enables which are

valid for an entire cycle or as write-byte-enables which are

valid for each byte on each data transfer, allowing partial

word transactions. As outputs, pins are used by either

peripheral controller or DMA controller depending upon the

type of transfer involved.

O

5V tolerant

3.3V LVTTL

2

PerWE

Peripheral Write Enable. Low when any of the two

PerWBE signals are low.

I/O

5V tolerant

3.3V LVTTL

[PerCS0:3]

Peripheral Chip Selects

O

5V tolerant

3.3V LVTTL

2

PerOE

Used by either peripheral controller or DMA controller

depending upon the type of transfer involved. When the

NPe405L is the bus master, it enables the selected

SDRAMs to drive the bus.

O

5V tolerant

3.3V LVTTL

2

PerR/W

Used by the NPe405L as an output by either the peripheral

controller or DMA controller depending upon the type of

transfer involved. High indicates a read from memory, low

indicates a write to memory.

O

5V tolerant

3.3V LVTTL

PerReady

Used by a peripheral slave to indicate it is ready to transfer

data.

I

5V tolerant

3.3V LVTTL

1

PerBLast

Used by the NPe405L to indicate the last transfer of a

memory access.

O

5V tolerant

3.3V LVTTL

4

PerClk

Peripheral Clock to be used by synchronous peripheral

slaves.

O

5V tolerant

3.3V LVTTL

PerErr

Used as an input to record external slave peripheral

errors.

I

5V tolerant

3.3V LVTTL

1, 5

[DMAReq0:3]

Used by slave peripherals to indicate they are prepared to

transfer data.

I

5V tolerant

3.3V LVTTL

1, 5

Signal Functional Description

(Part 3 of 6)

Notes:

1. Receiver input has hysteresis

2. Must pull up (recommended value is 3k

to 3.3V, 10k

to 5V

)

3. Must pull down (recommended value is 1k

)

4. If not used, must pull up (recommended value is 3k

to 3.3V)

5. If not used, must pull down (recommended value is 1k

)

6. Strapping input during reset; pull-up or pull-down required

Signal Name

Description

I/O

Type

Notes

相关PDF资料 |

PDF描述 |

|---|---|

| PowerNP NPe405 | 32-Bit Embedded Processor(32位嵌入式处理器(应用于网络方面,提供高性价比)) |

| PowerPC 401GF | 32-bit RISC Embedded Controllers(32位RISC结构嵌入式控制器) |

| PowerPC 403GA | 32-bit RISC Embedded Controllers(32位RISC结构嵌入式控制器) |

| PowerPC 403GB | 32-bit RISC Embedded Controllers(32位RISC结构嵌入式控制器) |

| PowerPC 403GC | 32-bit RISC Embedded Controllers(32位RISC结构嵌入式控制器) |

相关代理商/技术参数 |

参数描述 |

|---|---|

| POWERPAC-B | 制造商:IAR Systems 功能描述:PowerPac |

| POWERPAC-S | 制造商:IAR Systems 功能描述:PowerPac |

| POWERPAT PLUS | 制造商:Fluke Electronics 功能描述:SOFTWARE PAT |

| POWERPATPLUS | 制造商:Fluke Electronics 功能描述:Fluke Powerpat Plus |

| POWERPLUG15W | 制造商:STMICROELECTRONICS 制造商全称:STMicroelectronics 功能描述:AC/DC POWER SUPPLY |

发布紧急采购,3分钟左右您将得到回复。