- 您现在的位置:买卖IC网 > PDF目录361286 > QL3004 (QuickLogic Corp.) pASIC 3 FPGA Family High Performance and High Density with Low Cost and Complete Flexibiltiy(具有低成本和充分灵活性的高性能和高密度的pASIC 3现场可编程门阵列) PDF资料下载

参数资料

| 型号: | QL3004 |

| 厂商: | QuickLogic Corp. |

| 英文描述: | pASIC 3 FPGA Family High Performance and High Density with Low Cost and Complete Flexibiltiy(具有低成本和充分灵活性的高性能和高密度的pASIC 3现场可编程门阵列) |

| 中文描述: | 帕希奇3 FPGA系列高性能与高密度的低成本和完整Flexibiltiy(具有低成本和充分灵活性的高性能和高密度的帕希奇3现场可编程门阵列) |

| 文件页数: | 2/10页 |

| 文件大小: | 254K |

| 代理商: | QL3004 |

2

Preliminary

7-2

pASIC 3 FPGA

TM

Family

Family Summary

The pASIC 3 family is fabricated on a 0.35mm 4-

layer metal process using QuickLogic’s patented

ViaLink

“

technology to provide a unique combination

of high performance, high density, low cost, and

complete flexibility. The five devices in the family

range from 4,000 usable PLD gates with 82 I/Os to

60,000 usable PLD gates with 3163 I/Os, making

them among the largest FPGAs available. While

other FPGA families sacrifice performance to reach

these densities, the pASIC 3 family is the fastest

available from any vendor at any density level - with

16-bit counter speeds that exceed 300 MHz and

datapath speeds over 400 MHz.

With die sizes as small as half those of competing

FPGAs, pASIC 3 devices provide high levels of den-

sity and performance at a lower cost. The pASIC 3

family also provides 100% routability, even with all

logic cells used and I/O pins fixed. This capability is

critical for larger designs completed using high-level

hardware description languages such as Verilog and

VHDL.

Devices in the pASIC 3 family are based on an array

of highly flexible logic cells which have been opti-

mized to efficiently implement a wide range of logic

functions at high speed. Each cell can implement

one large function, five independent smaller func-

tions, or any combination in-between.

Logic cells are configured and interconnected by

rows and columns of routing metal and ViaLink

metal-to-metal antifuses. Because ViaLink antifuses

are small, fast, and are placed between metal layers

above the logic cells (rather than on the silicon sub-

strate), they can be located at every routing track

junction. This approach allows abundant intercon-

nect resources with small die sizes.

pASIC 3 family members feature 3.3 volt operation

with multi-volt compatible I/Os. Thus the devices

can easily operate in 3 volt only systems, as well as

mixed 3.3 volt/5 volt systems.

A wide range of additional family features comple-

ments the pASIC 3 family. All members include 5

volt and 3 volt PCI-compliant speed grades capable

of implementing bus master and target applications

at 33 MHz with zero wait states. I/O pins provide

individually-controlled output enables, dedicated

input/feedback registers, and full JTAG capability for

boundary scan and test. Different family members in

the same package are pin-compatible with one

another, permitting easy design migration within the

family. In addition, pASIC 3 devices provide the ben-

efits of non-volatility, high design security, immediate

functionality on power-up, and self-contained single

chip solutions.

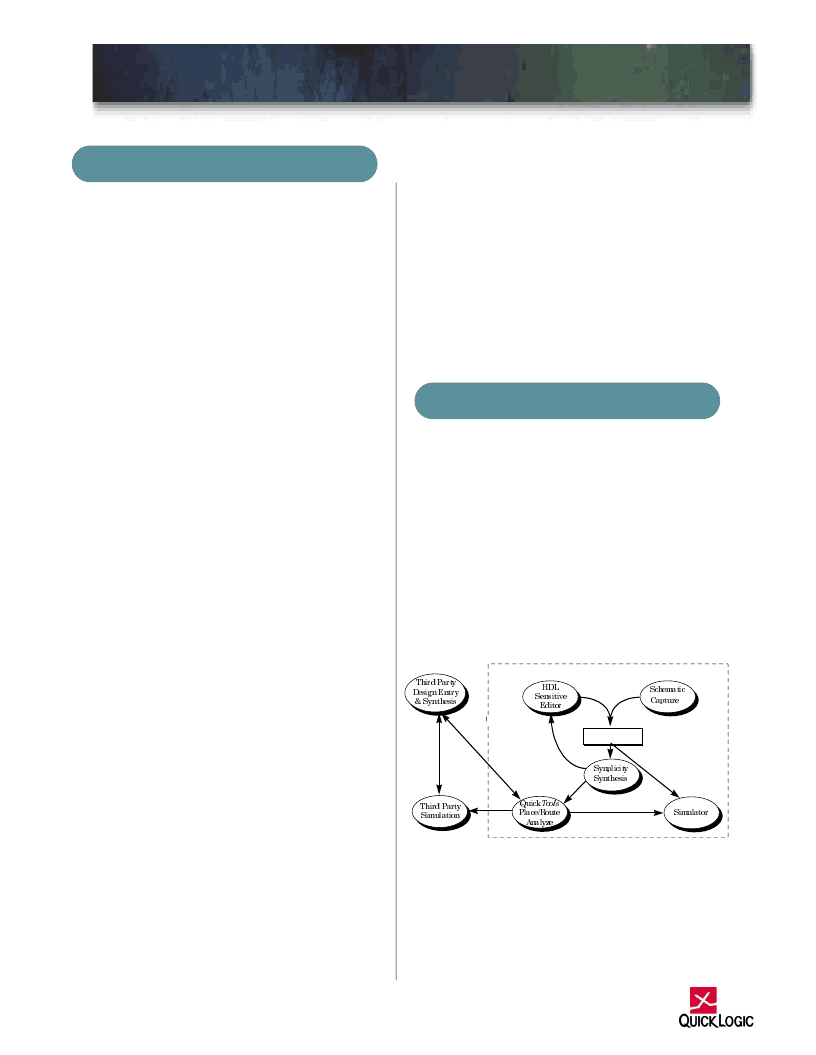

Software support for the pASIC 3 family is available

through three basic packages. The turnkey PC-based

QuickWorks

package, shown in Figure 1, provides

the most complete FPGA software solution from

design entry, to logic synthesis, to place and route, to

simulation. QuickWorks includes VHDL, Verilog,

schematic, boolean, and mixed-mode entry with fast

and efficient logic synthesis provided by the inte-

grated Synplicity Synplify Lite

tool, specially tuned

to take advantage of the pASIC 3 architecture.

QuickWorks also provides functional and timing sim-

ulation for guaranteed timing and source-level debug-

ging.

FIGURE 1. QuickWorks Tool Suite

The PC/Sun/HP-based QuickTools

and PC-based

QuickWorks

-Lite packages are a subset of Quick-

Works and provide a solution for designers who use

Cadence, Mentor, Synopsys, Viewlogic, Intergraph,

or other third-party tools for design entry, synthesis,

F

AMILY

S

UMMARY

D

EVELOPMENT

T

OOLS

6LPXODWRU

Verilog

VHDL

Schematic

4XLFN

7RROV

3ODFH5RXW H

$QDO\]H

Mixed Mode

QuickBoolean

7KLUG3DUW\

'HVLJQ(QWU\

6\QWKHVLV

7KLUG3DUW\

6LPXODWLRQ

+'/

6HQVLWLYH

(GLWRU

6FKHPDWLF

&DSWXUH

6\QSOLFLW\

6\QWKHVLV

相关PDF资料 |

PDF描述 |

|---|---|

| QL3012 | pASIC3 FPGA Combining High Performance and High Density(高性能和高密度相结合的pASIC3现场可编程门阵列) |

| QL3040 | pASIC3 FPGA Combining High Performance and High Density(高性能和高密度相结合的pASIC3现场可编程门阵列) |

| QL3060 | pASIC3 FPGA Combining High Performance and High Density(高性能和高密度相结合的pASIC3现场可编程门阵列) |

| QL3025 | pASIC3 FPGA Combining High Performance and High Density(高性能和高密度相结合的pASIC3现场可编程门阵列) |

| QL4009-3PF84C | CONV DC/DC 10W DUL 5V +-12V PCB |

相关代理商/技术参数 |

参数描述 |

|---|---|

| QL3012 | 制造商:未知厂家 制造商全称:未知厂家 功能描述:60,000 Usable PLD Gate pASIC3 FPGA Combining High Performance and High Density |

| QL3012-0PF100C | 制造商:未知厂家 制造商全称:未知厂家 功能描述:Field Programmable Gate Array (FPGA) |

| QL3012-0PF100C-5224 | 制造商:QuickLogic Corporation 功能描述:QLGQL3012-0PF100C-5224 QL3012-0PF100C-52 |

| QL3012-0PF100I | 制造商:未知厂家 制造商全称:未知厂家 功能描述:Field Programmable Gate Array (FPGA) |

| QL3012-0PF100I-5762 | 制造商:QuickLogic Corporation 功能描述: |

发布紧急采购,3分钟左右您将得到回复。