- 您现在的位置:买卖IC网 > PDF目录361286 > QL3004 (QuickLogic Corp.) pASIC 3 FPGA Family High Performance and High Density with Low Cost and Complete Flexibiltiy(具有低成本和充分灵活性的高性能和高密度的pASIC 3现场可编程门阵列) PDF资料下载

参数资料

| 型号: | QL3004 |

| 厂商: | QuickLogic Corp. |

| 英文描述: | pASIC 3 FPGA Family High Performance and High Density with Low Cost and Complete Flexibiltiy(具有低成本和充分灵活性的高性能和高密度的pASIC 3现场可编程门阵列) |

| 中文描述: | 帕希奇3 FPGA系列高性能与高密度的低成本和完整Flexibiltiy(具有低成本和充分灵活性的高性能和高密度的帕希奇3现场可编程门阵列) |

| 文件页数: | 7/10页 |

| 文件大小: | 254K |

| 代理商: | QL3004 |

7-7

pASIC 3 FPGA

TM

Family

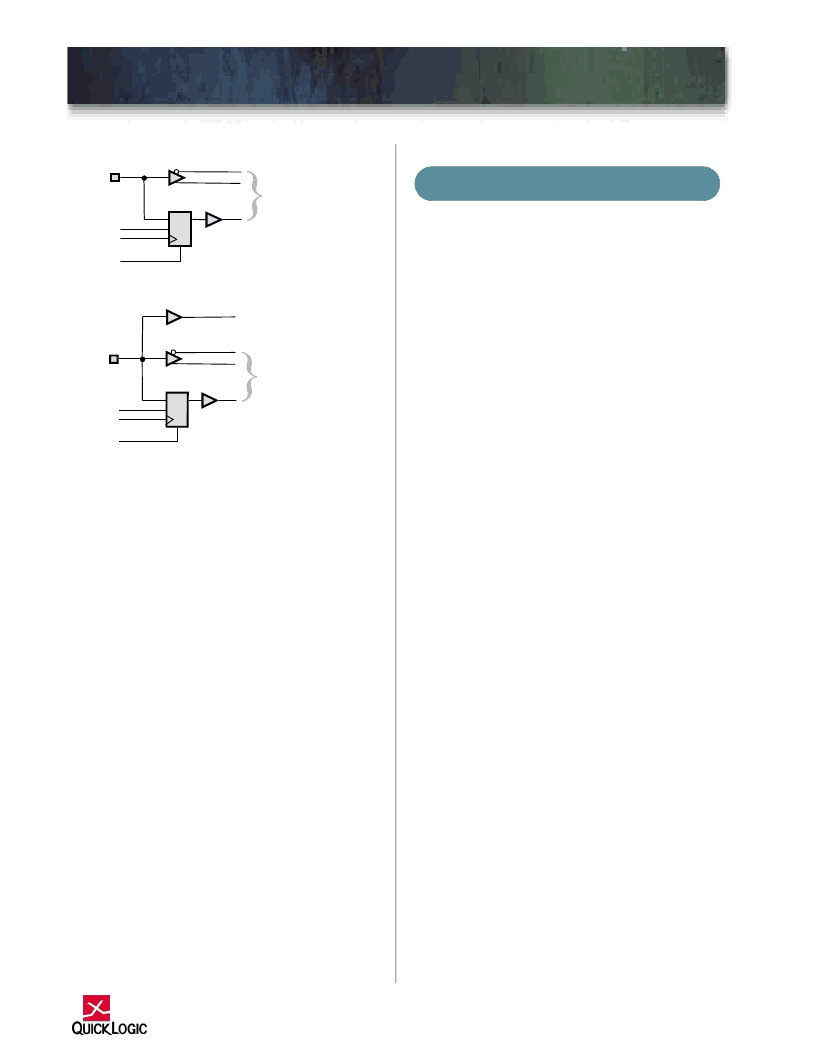

FIGURE 8. Basic Input Cell

FIGURE 9. Input Cell with Network Driver

Input-only pins are special low-skew, high-drive-cur-

rent pins for driving high fan-out nets. As shown in

Figure 10a, each input-only pin is associated with an

input cell which can provide true or complement

combinatorial or true registered signals to the device.

Figure 10b shows that a subset of the input-only pins

can also drive one of two types of special highly-dis-

tributed, buffered networks typically used for routing

clock or control signals. These networks are

described in detail in the following Routing Resources

section of this data sheet.

JTAG pins support IEEE standard 1149.1a to pro-

vide boundary scan capability for pASIC 3 devices.

Boundary scan can be used to test pin connections

and to view the state of internal nodes. Test data and

commands are serially shifted into the device, then

results are serially shifted out and examined. The fol-

lowing public instructions are supported: BYPASS,

EXTEST, and SAMPLE/PRELOAD.

Six pins are dedicated to JTAG and programming

functions on each pASIC 3 device, and are unavail-

able for general design input and output signals. TDI

and TDO are JTAG test data input and output,

shifted by control clock TCK. TMS is JTAG test

mode select and TRSTB is JTAG test reset input.

Most of the five JTAG pins also have separate func-

tions used only during device programming. A sixth

pin, STM, is used only for programming

.

Routing Resources

Five types of routing resources are provided in pASIC

3 devices: segmented wires, dual wires, express

wires, quad wires, and distributed networks. Seg-

mented wires run vertically throughout the routing

array and dual wires run horizontally. Segmented

and dual wires are predominantly used for local con-

nections. They effectively traverse one or two logic

cells and then use a ViaLink element to continue to

the next cell or to change direction. Their low resis-

tance and capacitance provide high performance for

local logic cell connections.

Express lines run the length of the device uninter-

rupted. These lines have a higher capacitance than

segmented wires, but provide higher performance for

long routes or high fan-out nets.

Quad wires are similar to segmented wires in that

they are used for local interconnect, but instead of

having ViaLink elements at each logic cell, they have

ViaLink elements every fourth logic cell. As a result,

these wires are typically used to implement interme-

diate length or medium fan-out nets.

Distributed networks are highly buffered, well distrib-

uted routing structures designed to provide low-skew

signals for high fan-out nets. One type, called the

"array" network, routes array logic cell flip-flop clock,

set, and reset signals. The second type, called the

"global" network, routes array logic cell flip-flop con-

trols, input and I/O register controls, I/O cell output

enable controls, and the F1 logic cell input. Array

networks can only be driven by specific input-only

pins. Global networks can be driven by specific

input-only pins, or by any other pin or any logic cell

output.

Routing wires are contained within horizontal and

vertical channels running above logic cells within the

logic cell array. By programming the appropriate

ViaLink elements, any logic cell output can be con-

nected to any other logic cell input. QuickLogic

’

s

four-layer metal ViaLink process provides abundant

wire and programming resources, allowing 100%

routability and pin-out maintainability with no manual

routing. The place and route software not only auto-

matically routes the design, but automatically allo-

cates signals to the appropriate types of wires (based

D

E

R

Q

To Logic Array

D

E

R

Q

To Logic Array

To Array or Global

Network

R

OUTING

R

ESOURCES

相关PDF资料 |

PDF描述 |

|---|---|

| QL3012 | pASIC3 FPGA Combining High Performance and High Density(高性能和高密度相结合的pASIC3现场可编程门阵列) |

| QL3040 | pASIC3 FPGA Combining High Performance and High Density(高性能和高密度相结合的pASIC3现场可编程门阵列) |

| QL3060 | pASIC3 FPGA Combining High Performance and High Density(高性能和高密度相结合的pASIC3现场可编程门阵列) |

| QL3025 | pASIC3 FPGA Combining High Performance and High Density(高性能和高密度相结合的pASIC3现场可编程门阵列) |

| QL4009-3PF84C | CONV DC/DC 10W DUL 5V +-12V PCB |

相关代理商/技术参数 |

参数描述 |

|---|---|

| QL3012 | 制造商:未知厂家 制造商全称:未知厂家 功能描述:60,000 Usable PLD Gate pASIC3 FPGA Combining High Performance and High Density |

| QL3012-0PF100C | 制造商:未知厂家 制造商全称:未知厂家 功能描述:Field Programmable Gate Array (FPGA) |

| QL3012-0PF100C-5224 | 制造商:QuickLogic Corporation 功能描述:QLGQL3012-0PF100C-5224 QL3012-0PF100C-52 |

| QL3012-0PF100I | 制造商:未知厂家 制造商全称:未知厂家 功能描述:Field Programmable Gate Array (FPGA) |

| QL3012-0PF100I-5762 | 制造商:QuickLogic Corporation 功能描述: |

发布紧急采购,3分钟左右您将得到回复。