- 您现在的位置:买卖IC网 > PDF目录361286 > QL3004 (QuickLogic Corp.) pASIC 3 FPGA Family High Performance and High Density with Low Cost and Complete Flexibiltiy(具有低成本和充分灵活性的高性能和高密度的pASIC 3现场可编程门阵列) PDF资料下载

参数资料

| 型号: | QL3004 |

| 厂商: | QuickLogic Corp. |

| 英文描述: | pASIC 3 FPGA Family High Performance and High Density with Low Cost and Complete Flexibiltiy(具有低成本和充分灵活性的高性能和高密度的pASIC 3现场可编程门阵列) |

| 中文描述: | 帕希奇3 FPGA系列高性能与高密度的低成本和完整Flexibiltiy(具有低成本和充分灵活性的高性能和高密度的帕希奇3现场可编程门阵列) |

| 文件页数: | 4/10页 |

| 文件大小: | 254K |

| 代理商: | QL3004 |

4

Preliminary

7-4

pASIC 3 FPGA

TM

Family

Four Layer Metal CMOS Process

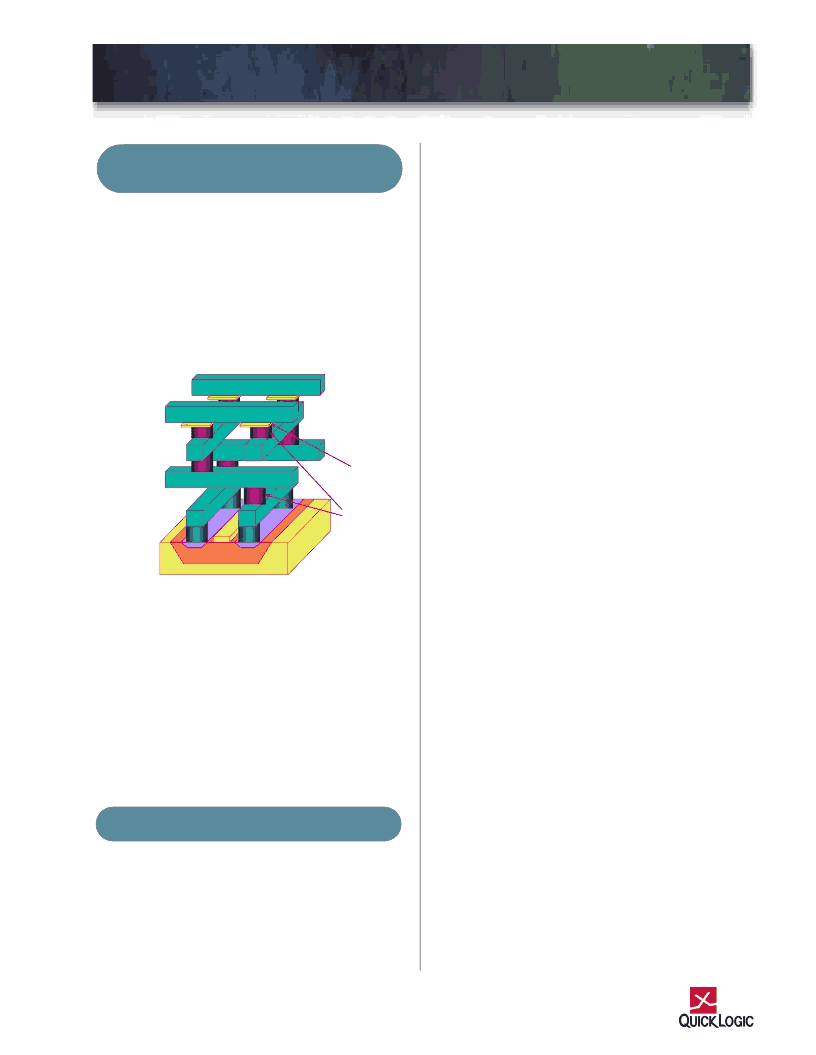

QuickLogic pASIC 3 devices are fabricated on a

conventional high-volume CMOS process. The base

technology is a 0.35 micron, n-well CMOS

technology with a single polysilicon layer and four

layers of metal interconnect as shown in Figure 3.

The only deviation from the standard process flow

occurs when a single mask is used for the amorphous

silicon to form the ViaLink elements between the

metal deposition steps.

FIGURE 3. Four Layer Metal ViaLink

Structure

As the size of a ViaLink

via is identical to that of a

standard metal interconnect via, programmable ele-

ments can be packed very densely. The packing den-

sity is limited only by the minimum dimensions of the

metal-line to metal-line pitch. As a result, pASIC 3

devices typically have four to six times the number of

programmable elements per usable logic gate, with

smaller die sizes, than do SRAM-based FPGAs. Fur-

thermore, the ViaLink technology can easily scale to

smaller process geometries in the future.

Array of Logic Cells

The pASIC 3 device architecture consists of an array

of user-configurable logic building blocks, called logic

cells, set beneath a grid of metal wiring channels sim-

ilar to those of a gate array. Through ViaLink ele-

ments located at the wire intersections, the output(s)

of any cell may be programmed to connect to the

input(s) of any other cell. By moving all interconnect

resources above the logic cells, die sizes are less than

half of two-layer metal technologies, as shown in Fig-

ure 4.

The regular and orthogonal interconnect makes the

pASIC 3 architecture similar in structure and perfor-

mance to a metal-masked gate array. It also ensures

that system operating speed is far less sensitive to

partitioning and placement decisions, as minor revi-

sions to a logic design can easily be incorporated

without re-routing problems, resulting in only small

changes in performance.

Adequate wiring resources permit 100% automatic

placement and routing of designs using up to 100%

of the logic cells and I/O pins. This capability has

been demonstrated on designs that also include a

high percentage of fixed pin placements.

The pASIC 3 logic cell, shown in Figure 5, is a gen-

eral-purpose building block that can implement most

TTL and gate array macro library functions. It is

equivalent to the pASIC 2 cell, allowing easy design

upgrades. The cell has been optimized to maintain

the inherent speed advantage of the ViaLink technol-

ogy while ensuring maximum logic flexibility. Since

the logic cell has multiple outputs, it can implement

one large function or multiple smaller independent

functions in parallel.

The function of a logic cell is determined by the logic

levels applied to the inputs of the AND gates and

multiplexers. ViaLink sites located on signal wires tied

to the gate inputs perform the dual role of configur-

ing the logic function of a cell and establishing con-

nections between cells.

F

OUR

L

AYER

M

ETAL

CMOS P

ROCESS

Metal 3

Horiz. Tracks

Metal 4

Vert. Tracks

Logic Cell Wiring

ViaLink

Amorphous

Silicon

Antifuse

Tungsten

Plug Via

A

RRAY

OF

L

OGIC

C

ELLS

相关PDF资料 |

PDF描述 |

|---|---|

| QL3012 | pASIC3 FPGA Combining High Performance and High Density(高性能和高密度相结合的pASIC3现场可编程门阵列) |

| QL3040 | pASIC3 FPGA Combining High Performance and High Density(高性能和高密度相结合的pASIC3现场可编程门阵列) |

| QL3060 | pASIC3 FPGA Combining High Performance and High Density(高性能和高密度相结合的pASIC3现场可编程门阵列) |

| QL3025 | pASIC3 FPGA Combining High Performance and High Density(高性能和高密度相结合的pASIC3现场可编程门阵列) |

| QL4009-3PF84C | CONV DC/DC 10W DUL 5V +-12V PCB |

相关代理商/技术参数 |

参数描述 |

|---|---|

| QL3012 | 制造商:未知厂家 制造商全称:未知厂家 功能描述:60,000 Usable PLD Gate pASIC3 FPGA Combining High Performance and High Density |

| QL3012-0PF100C | 制造商:未知厂家 制造商全称:未知厂家 功能描述:Field Programmable Gate Array (FPGA) |

| QL3012-0PF100C-5224 | 制造商:QuickLogic Corporation 功能描述:QLGQL3012-0PF100C-5224 QL3012-0PF100C-52 |

| QL3012-0PF100I | 制造商:未知厂家 制造商全称:未知厂家 功能描述:Field Programmable Gate Array (FPGA) |

| QL3012-0PF100I-5762 | 制造商:QuickLogic Corporation 功能描述: |

发布紧急采购,3分钟左右您将得到回复。