- 您现在的位置:买卖IC网 > PDF目录269903 > QLPXA263B1C400 (INTEL CORP) 32-BIT, 400 MHz, RISC PROCESSOR, PBGA294 PDF资料下载

参数资料

| 型号: | QLPXA263B1C400 |

| 厂商: | INTEL CORP |

| 元件分类: | 微控制器/微处理器 |

| 英文描述: | 32-BIT, 400 MHz, RISC PROCESSOR, PBGA294 |

| 封装: | 13 X 13 MM, 1.4MM PITCH, PLASTIC, TPBGA-294 |

| 文件页数: | 44/44页 |

| 文件大小: | 1302K |

| 代理商: | QLPXA263B1C400 |

第1页第2页第3页第4页第5页第6页第7页第8页第9页第10页第11页第12页第13页第14页第15页第16页第17页第18页第19页第20页第21页第22页第23页第24页第25页第26页第27页第28页第29页第30页第31页第32页第33页第34页第35页第36页第37页第38页第39页第40页第41页第42页第43页当前第44页

Package Information

Intel PXA255 Processor Electrical, Mechanical, and Thermal Specification

9

Some of the processor pins can be connected to multiple signals. The GAFRn_m registers

determine the signal connected to the pin. Some signals can go to multiple pins. The signal must be

routed to one pin only by using the GAFRn_m registers. Because this is true, some pins are listed

twice—once in each unit that can use the pin. Not all peripherals can be used simutaneously in one

design because different peripherals share the same pins.

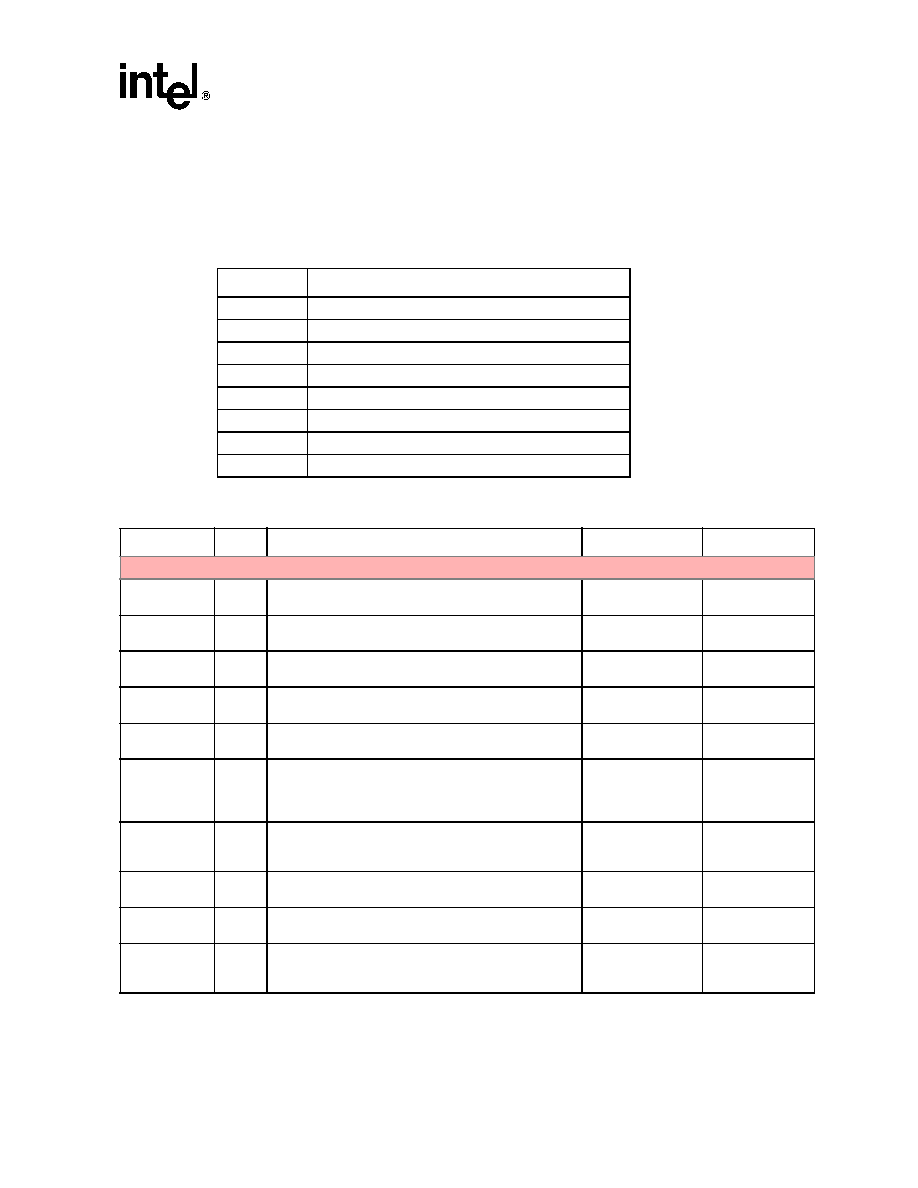

Table 2. Processor Pin Types

Type

Function

IC

CMOS input

OC

CMOS output

OCZ

CMOS output, Hi-Z

ICOCZ

CMOS bidirectional, Hi-Z

IA

Analog Input

OA

Analog output

IAOA

Analog bidirectional

SUP

Supply pin (either VCC or VSS)

Table 3. Pin and Signal Descriptions for the PXA255 Processor (Sheet 1 of 9)

Pin Name

Type

Signal Descriptions

Reset State

Sleep State

Memory Controller Pins

MA[25:0]

OCZ

Memory address bus. (output) Signals the address

requested for memory accesses.

Driven Low

MD[15:0]

ICOCZ

Memory data bus. (input/output) Lower 16 bits of the

data bus.

Hi-Z

Driven Low

MD[31:16]

ICOCZ

Memory data bus. (input/output) Used for 32-bit

memories.

Hi-Z

Driven Low

nOE

OCZ

Memory output enable. (output) Connect to the output

enables of memory devices to control data bus drivers.

Driven High

Note [4]

nWE

OCZ

Memory write enable. (output) Connect to the write

enables of memory devices.

Driven High

Note [4]

nSDCS[3:0]

OCZ

SDRAM CS for banks 3 through 0. (output) Connect to

the chip select (CS) pins for SDRAM. For the PXA255

processor processor nSDCS0 can be Hi-Z, nSDCS1-3

cannot.

Driven High

Note [5]

DQM[3:0]

OCZ

SDRAM DQM for data bytes 3 through 0. (output)

Connect to the data output mask enables (DQM) for

SDRAM.

Driven Low

nSDRAS

OCZ

SDRAM RAS. (output) Connect to the row address

strobe (RAS) pins for all banks of SDRAM.

Driven High

nSDCAS

OCZ

SDRAM CAS. (output) Connect to the column address

strobe (CAS) pins for all banks of SDRAM.

Driven High

SDCKE[0]

OC

Synchronous Static Memory clock enable. (output)

Connect to the CKE pins of SMROM. The memory

controller provides control register bits for de-assertion.

Driven Low

相关PDF资料 |

PDF描述 |

|---|---|

| QL5810-66CPTN196I | PCI BUS CONTROLLER, PBGA196 |

| QL5820-33BPTN196C | PCI BUS CONTROLLER, PBGA196 |

| QL5842-33BPSN484M | PCI BUS CONTROLLER, PBGA484 |

| QT83C154XXX-L | 8-BIT, MROM, 6 MHz, MICROCONTROLLER, PQFP44 |

| QC87C251SQ | 8-BIT, UVPROM, 12 MHz, MICROCONTROLLER, CDIP40 |

相关代理商/技术参数 |

参数描述 |

|---|---|

| QLQGT3T131TA | 制造商:Panasonic Industrial Company 功能描述:COIL |

| QLS08ZH-N | 制造商:Power-One 功能描述:QUARTER BRICK DCDC - Bulk |

| QLS08ZH-NT | 功能描述:DC/DC转换器 RoHS:否 制造商:Murata 产品: 输出功率: 输入电压范围:3.6 V to 5.5 V 输入电压(标称): 输出端数量:1 输出电压(通道 1):3.3 V 输出电流(通道 1):600 mA 输出电压(通道 2): 输出电流(通道 2): 安装风格:SMD/SMT 封装 / 箱体尺寸: |

| QLS-1 | 制造商:LAUREL ELECTRONICS 功能描述:CURRENT LOOP SPLITTER RETRANSM 制造商:LAUREL ELECTRONICS 功能描述:CURRENT LOOP SPLITTER RETRANSMITTER; Accuracy: 0.02%; Input Type:Selectable Current; No. of Output Channels:4; Output Type:Selectable Current; Power Consumption:3.5W |

| QLS12ZG-NT | 功能描述:DC/DC转换器 5V/12A OUT NEG-LOGIC QUARTER BRICK RoHS:否 制造商:Murata 产品: 输出功率: 输入电压范围:3.6 V to 5.5 V 输入电压(标称): 输出端数量:1 输出电压(通道 1):3.3 V 输出电流(通道 1):600 mA 输出电压(通道 2): 输出电流(通道 2): 安装风格:SMD/SMT 封装 / 箱体尺寸: |

发布紧急采购,3分钟左右您将得到回复。