- 您现在的位置:买卖IC网 > PDF目录69310 > R5F2138CFJFP FLASH, 20 MHz, MICROCONTROLLER, PQFP80 PDF资料下载

参数资料

| 型号: | R5F2138CFJFP |

| 元件分类: | 微控制器/微处理器 |

| 英文描述: | FLASH, 20 MHz, MICROCONTROLLER, PQFP80 |

| 封装: | 12 X 12 MM, 0.50 MM PITCH, PLASTIC, LQFP-80 |

| 文件页数: | 9/30页 |

| 文件大小: | 483K |

| 代理商: | R5F2138CFJFP |

第1页第2页第3页第4页第5页第6页第7页第8页当前第9页第10页第11页第12页第13页第14页第15页第16页第17页第18页第19页第20页第21页第22页第23页第24页第25页第26页第27页第28页第29页第30页

67

ATmega165A/PA/325A/PA/3250A/PA/645A/P/6450A/P [DATASHEET]

8285E–AVR–02/2013

The following subsections shortly describe the alternate functions for each port, and relate the overriding signals to

the alternate function. Refer to the alternate function description for further details.

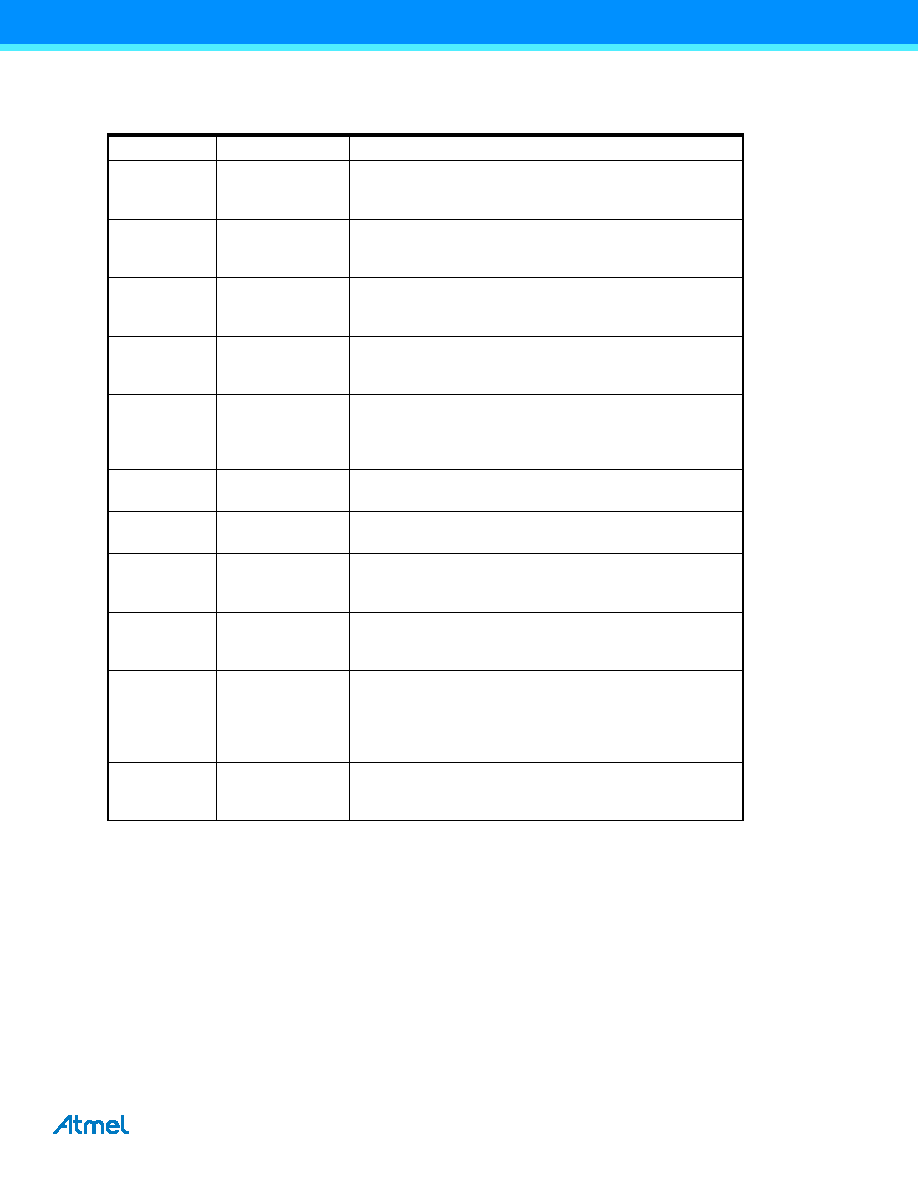

Table 14-2.

Generic description of overriding signals for alternate functions.

Signal name

Full name

Description

PUOE

Pull-up Override

Enable

If this signal is set, the pull-up enable is controlled by the PUOV

signal. If this signal is cleared, the pull-up is enabled when

{DDxn, PORTxn, PUD} = 0b010.

PUOV

Pull-up Override

Value

If PUOE is set, the pull-up is enabled/disabled when PUOV is

set/cleared, regardless of the setting of the DDxn, PORTxn,

and PUD Register bits.

DDOE

Data Direction

Override Enable

If this signal is set, the Output Driver Enable is controlled by the

DDOV signal. If this signal is cleared, the Output driver is

enabled by the DDxn Register bit.

DDOV

Data Direction

Override Value

If DDOE is set, the Output Driver is enabled/disabled when

DDOV is set/cleared, regardless of the setting of the DDxn

Register bit.

PVOE

Port Value

Override Enable

If this signal is set and the Output Driver is enabled, the port

value is controlled by the PVOV signal. If PVOE is cleared, and

the Output Driver is enabled, the port Value is controlled by the

PORTxn Register bit.

PVOV

Port Value

Override Value

If PVOE is set, the port value is set to PVOV, regardless of the

setting of the PORTxn Register bit.

PTOE

Port Toggle

Override Enable

If PTOE is set, the PORTxn Register bit is inverted.

DIEOE

Digital Input

Enable Override

Enable

If this bit is set, the Digital Input Enable is controlled by the

DIEOV signal. If this signal is cleared, the Digital Input Enable

is determined by MCU state (Normal mode, sleep mode).

DIEOV

Digital Input

Enable Override

Value

If DIEOE is set, the Digital Input is enabled/disabled when

DIEOV is set/cleared, regardless of the MCU state (Normal

mode, sleep mode).

DI

Digital Input

This is the Digital Input to alternate functions. In the figure, the

signal is connected to the output of the schmitt trigger but

before the synchronizer. Unless the Digital Input is used as a

clock source, the module with the alternate function will use its

own synchronizer.

AIO

Analog

Input/Output

This is the Analog Input/output to/from alternate functions. The

signal is connected directly to the pad, and can be used bi-

directionally.

相关PDF资料 |

PDF描述 |

|---|---|

| R5F2138CHJFP | FLASH, 20 MHz, MICROCONTROLLER, PQFP80 |

| R5F2138AFJFP | FLASH, 20 MHz, MICROCONTROLLER, PQFP80 |

| R5F2138CCNFP | 8-BIT, FLASH, 20 MHz, MICROCONTROLLER, PQFP80 |

| R5F21386CNFP | 8-BIT, FLASH, 20 MHz, MICROCONTROLLER, PQFP80 |

| R5F213G1DDSP | 8-BIT, FLASH, 20 MHz, MICROCONTROLLER, PDSO24 |

相关代理商/技术参数 |

参数描述 |

|---|---|

| R5F2138CMDFD | 制造商:RENESAS 制造商全称:Renesas Technology Corp 功能描述:The R8C/38M Group has data flash (1 KB × 4 blocks) with the background operation |

| R5F2138CMDFP | 制造商:RENESAS 制造商全称:Renesas Technology Corp 功能描述:The R8C/38M Group has data flash (1 KB × 4 blocks) with the background operation |

| R5F2138CMDFP#30 | 制造商:Renesas Electronics Corporation 功能描述:IC MCU 16BIT 128KB FLASH 80LQFP |

| R5F2138CMDFP#V0 | 制造商:Renesas Electronics Corporation 功能描述:IC MCU 16BIT 128KB FLASH 80LQFP |

| R5F2138CMDXXXFD | 制造商:RENESAS 制造商全称:Renesas Technology Corp 功能描述:The R8C/38M Group has data flash (1 KB × 4 blocks) with the background operation |

发布紧急采购,3分钟左右您将得到回复。