- 您现在的位置:买卖IC网 > PDF目录69312 > R5F2L3ACCNFP 8-BIT, FLASH, 20 MHz, MICROCONTROLLER, PQFP100 PDF资料下载

参数资料

| 型号: | R5F2L3ACCNFP |

| 元件分类: | 微控制器/微处理器 |

| 英文描述: | 8-BIT, FLASH, 20 MHz, MICROCONTROLLER, PQFP100 |

| 封装: | 14 X 14 MM, 0.50 MM PITCH, PLASTIC, LQFP-100 |

| 文件页数: | 42/74页 |

| 文件大小: | 959K |

| 代理商: | R5F2L3ACCNFP |

第1页第2页第3页第4页第5页第6页第7页第8页第9页第10页第11页第12页第13页第14页第15页第16页第17页第18页第19页第20页第21页第22页第23页第24页第25页第26页第27页第28页第29页第30页第31页第32页第33页第34页第35页第36页第37页第38页第39页第40页第41页当前第42页第43页第44页第45页第46页第47页第48页第49页第50页第51页第52页第53页第54页第55页第56页第57页第58页第59页第60页第61页第62页第63页第64页第65页第66页第67页第68页第69页第70页第71页第72页第73页第74页

48

2588F–AVR–06/2013

ATtiny261/461/861

the next time-out will generate a reset. To avoid the Watchdog Reset, WDIE must be set after

each interrupt.

Bit 4 – WDCE: Watchdog Change Enable

This bit must be set when the WDE bit is written to logic zero. Otherwise, the Watchdog will not

be disabled. Once written to one, hardware will clear this bit after four clock cycles. Refer to the

description of the WDE bit for a Watchdog disable procedure. This bit must also be set when

changing the prescaler bits. See “Timed Sequences for Changing the Configuration of the

Bit 3 – WDE: Watchdog Enable

When the WDE is written to logic one, the Watchdog Timer is enabled, and if the WDE is written

to logic zero, the Watchdog Timer function is disabled. WDE can only be cleared if the WDCE bit

has logic level one. To disable an enabled Watchdog Timer, the following procedure must be

followed:

1.

In the same operation, write a logic one to WDCE and WDE. A logic one must be writ-

ten to WDE even though it is set to one before the disable operation starts.

2.

Within the next four clock cycles, write a logic 0 to WDE. This disables the Watchdog.

In safety level 2, it is not possible to disable the Watchdog Timer, even with the algorithm

described above. See “Timed Sequences for Changing the Configuration of the Watchdog

In safety level 1, WDE is overridden by WDRF in MCUSR. See “MCUSR – MCU Status Regis-

ter” on page 47 for description of WDRF. This means that WDE is always set when WDRF is set.

To clear WDE, WDRF must be cleared before disabling the Watchdog with the procedure

described above. This feature ensures multiple resets during conditions causing failure, and a

safe start-up after the failure.

Note:

If the watchdog timer is not going to be used in the application, it is important to go through a

watchdog disable procedure in the initialization of the device. If the Watchdog is accidentally

enabled, for example by a runaway pointer or brown-out condition, the device will be reset, which

in turn will lead to a new watchdog reset. To avoid this situation, the application software should

always clear the WDRF flag and the WDE control bit in the initialization routine.

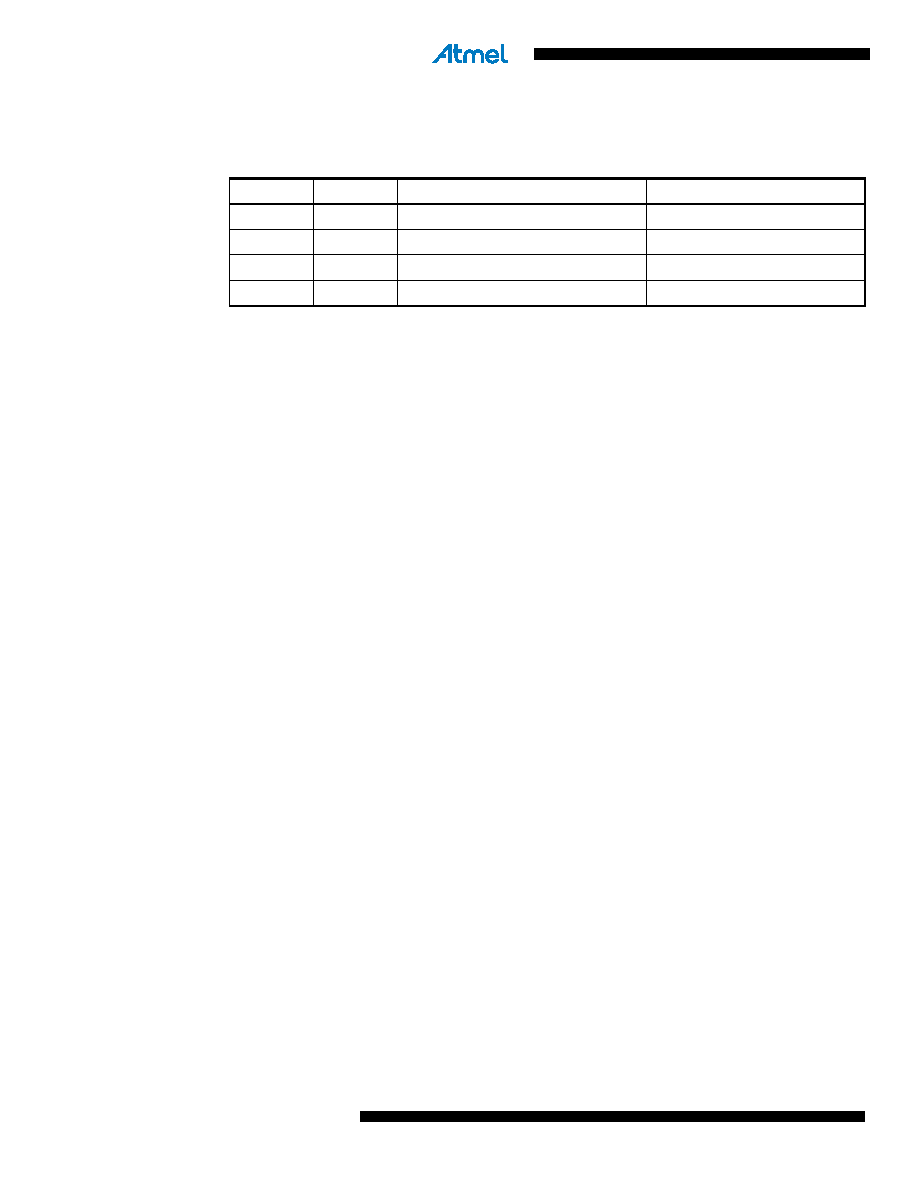

Table 8-2.

Watchdog Timer Configuration

WDE

WDIE

Watchdog Timer State

Action on Time-out

0

Stopped

None

0

1

Running

Interrupt

1

0

Running

Reset

1

Running

Interrupt

相关PDF资料 |

PDF描述 |

|---|---|

| R5F2L38ACNFA | 8-BIT, FLASH, 20 MHz, MICROCONTROLLER, PQFP80 |

| R5F2L38CCNFP | 8-BIT, FLASH, 20 MHz, MICROCONTROLLER, PQFP80 |

| R5F2L387CDFP | 8-BIT, FLASH, 20 MHz, MICROCONTROLLER, PQFP80 |

| R5F2L387CNFP | 8-BIT, FLASH, 20 MHz, MICROCONTROLLER, PQFP80 |

| R5F2L368CDFP | 8-BIT, FLASH, 20 MHz, MICROCONTROLLER, PQFP64 |

相关代理商/技术参数 |

参数描述 |

|---|---|

| R5F2L3ACCNFP#30 | 制造商:Renesas Electronics Corporation 功能描述:IC MCU 16BIT 128KB FLASH 100LQFP |

| R5F2L3ACCNFP#U1 | 制造商:Renesas Electronics Corporation 功能描述: |

| R5F2L3ACCNFP#V0 | 功能描述:MCU 1KB FLASH 128K ROM 100-LQFP RoHS:是 类别:集成电路 (IC) >> 嵌入式 - 微控制器, 系列:R8C/Lx/3AC 标准包装:250 系列:80C 核心处理器:8051 芯体尺寸:8-位 速度:16MHz 连通性:EBI/EMI,I²C,UART/USART 外围设备:POR,PWM,WDT 输入/输出数:40 程序存储器容量:- 程序存储器类型:ROMless EEPROM 大小:- RAM 容量:256 x 8 电压 - 电源 (Vcc/Vdd):4.5 V ~ 5.5 V 数据转换器:A/D 8x10b 振荡器型:内部 工作温度:-40°C ~ 85°C 封装/外壳:68-LCC(J 形引线) 包装:带卷 (TR) |

| R5F2L3ACMDFA#U0 | 制造商:Renesas Electronics Corporation 功能描述:R8C/L3AM 128+4/10 100QFP 14X20 制造商:Renesas Electronics Corporation 功能描述:R8C/L3AM 128+4/10 100QFP 14X20 -40 TO +85 - Trays 制造商:Renesas Electronics Corporation 功能描述:IC MCU 16BIT 128KB FLASH 100LQFP |

| R5F2L3ACMNFA#U0 | 制造商:Renesas Electronics Corporation 功能描述:R8C/L3AM 128+4/10 100QFP 14X20 制造商:Renesas Electronics Corporation 功能描述:R8C/L3AM 128+4/10 100QFP 14X20 -20 TO +85 - Trays 制造商:Renesas Electronics Corporation 功能描述:IC MCU 16BIT 128KB FLASH 100LQFP 制造商:Renesas Electronics Corporation 功能描述:MCU,R8C,16bit,20MHz,128KB Flash,QFP100 |

发布紧急采购,3分钟左右您将得到回复。