- 您现在的位置:买卖IC网 > PDF目录69335 > SAB-C167CS-LMCA (INFINEON TECHNOLOGIES AG) 16-BIT, 25 MHz, MICROCONTROLLER, PQFP144 PDF资料下载

参数资料

| 型号: | SAB-C167CS-LMCA |

| 厂商: | INFINEON TECHNOLOGIES AG |

| 元件分类: | 微控制器/微处理器 |

| 英文描述: | 16-BIT, 25 MHz, MICROCONTROLLER, PQFP144 |

| 封装: | PLASTIC, MQFP-144 |

| 文件页数: | 62/84页 |

| 文件大小: | 1082K |

| 代理商: | SAB-C167CS-LMCA |

第1页第2页第3页第4页第5页第6页第7页第8页第9页第10页第11页第12页第13页第14页第15页第16页第17页第18页第19页第20页第21页第22页第23页第24页第25页第26页第27页第28页第29页第30页第31页第32页第33页第34页第35页第36页第37页第38页第39页第40页第41页第42页第43页第44页第45页第46页第47页第48页第49页第50页第51页第52页第53页第54页第55页第56页第57页第58页第59页第60页第61页当前第62页第63页第64页第65页第66页第67页第68页第69页第70页第71页第72页第73页第74页第75页第76页第77页第78页第79页第80页第81页第82页第83页第84页

C167CS-4R

C167CS-L

Data Sheet

61

V2.2, 2001-08

Sample time and conversion time of the C167CS’s A/D Converter are programmable.

Table 14 should be used to calculate the above timings.

The limit values for

fBC must not be exceeded when selecting ADCTC.

Converter Timing Example:

Assumptions:

fCPU = 25 MHz (i.e. tCPU = 40 ns), ADCTC = ‘00’, ADSTC = ‘00’.

Basic clock

fBC

=

fCPU / 4 = 6.25 MHz, i.e. tBC = 160 ns.

Sample time

tS

=

tBC × 8 = 1280 ns.

Conversion time

tC

=

tS + 40 tBC + 2 tCPU = (1280 + 6400 + 80) ns = 7.8 s.

5) As the default basic clock after reset is f

BC = fCPU / 4 the ADC’s prescaler (ADCTC) must be programmed to

a valid factor as early as possible. A timeframe of approx. 6000 CPU clock cycles is sufficient to ensure a

proper reset calibration. This corresponds to minimum 300 instructions (worst case: external MUX bus with

maximum waitstates). This is required for

fCPU > 33 MHz and is recommended for fCPU > 25 MHz.

During the reset calibration conversions can be executed (with the current accuracy). The time required for

these conversions is added to the total reset calibration time.

6) During the conversion the ADC’s capacitance must be repeatedly charged or discharged. The internal

resistance of the reference voltage source must allow the capacitance to reach its respective voltage level

within each conversion step. The maximum internal resistance results from the programmed conversion

timing.

7) Not 100% tested, guaranteed by design and characterization.

8) During the sample time the input capacitance C

AIN can be charged/discharged by the external source. The

internal resistance of the analog source must allow the capacitance to reach its final voltage level within

tS.

After the end of the sample time

tS, changes of the analog input voltage have no effect on the conversion result.

Values for the sample time

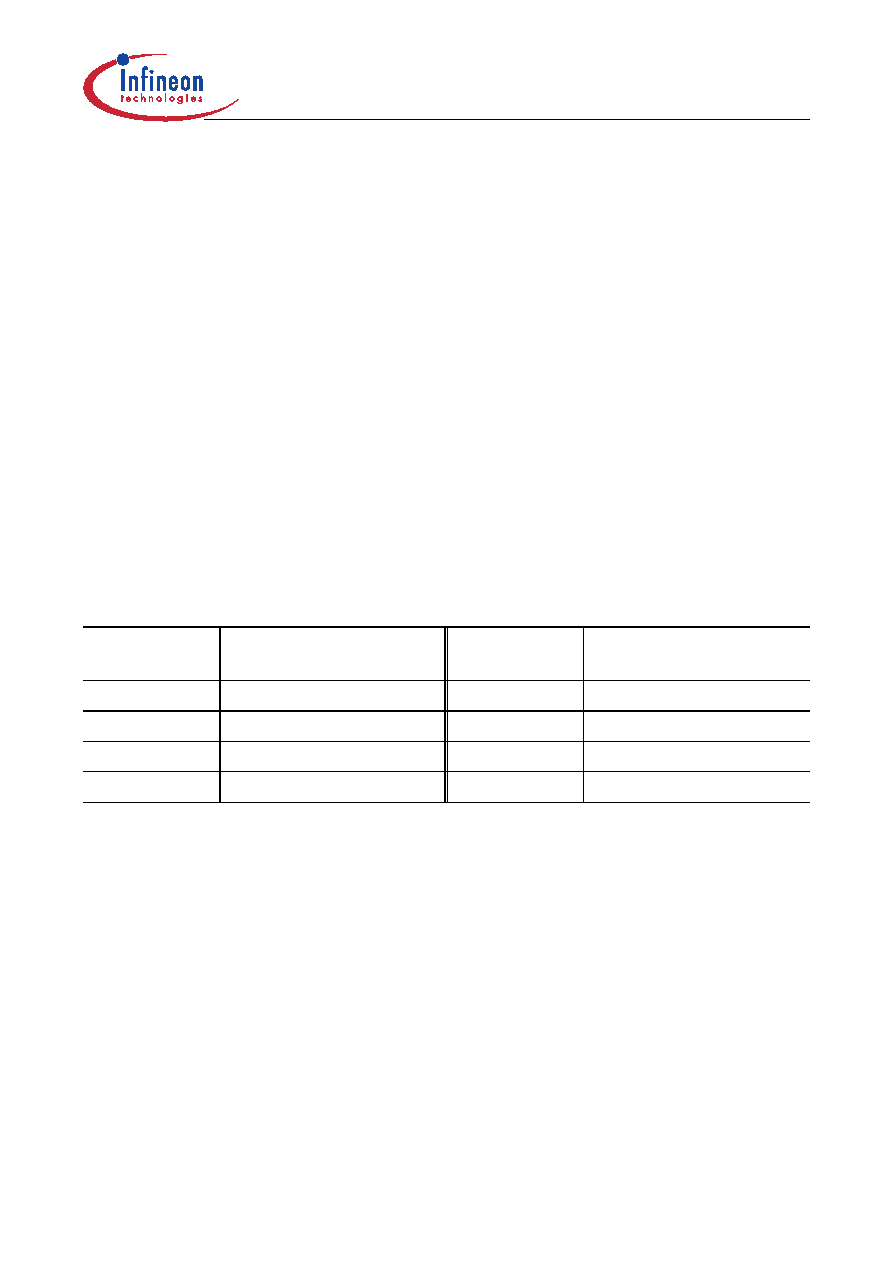

Table 14

A/D Converter Computation Table

ADCON.15|14

(ADCTC)

A/D Converter

Basic Clock

fBC

ADCON.13|12

(ADSTC)

Sample time

tS

00

fCPU / 4

00

tBC × 8

01

fCPU / 2

01

tBC × 16

10

fCPU / 16

10

tBC × 32

11

fCPU / 8

11

tBC × 64

相关PDF资料 |

PDF描述 |

|---|---|

| SAB-C167CS-4R33M | 16-BIT, MROM, 33 MHz, MICROCONTROLLER, PQFP144 |

| SAB-C167CS-4RM | 16-BIT, MROM, 25 MHz, MICROCONTROLLER, PQFP144 |

| SAK-C167CS-LM | 16-BIT, 25 MHz, MICROCONTROLLER, PQFP144 |

| SAB-C167CS-4R40M | 16-BIT, MROM, 40 MHz, MICROCONTROLLER, PQFP144 |

| SAK-C167CS-4R40M | 16-BIT, MROM, 40 MHz, MICROCONTROLLER, PQFP144 |

相关代理商/技术参数 |

参数描述 |

|---|---|

| SABC167CSLMCA+ | 制造商:Infineon Technologies AG 功能描述: |

| SABC167CSLMCA+X | 制造商:Infineon Technologies AG 功能描述:MCU 16-Bit C166 CISC/RISC ROMLess 3.3V/5V 144-Pin MQFP |

| SAB-C167SR-L33M | 制造商:INFINEON 制造商全称:Infineon Technologies AG 功能描述:16-Bit Single-Chip Microcontroller |

| SAB-C167SR-LM | 制造商:INFINEON 制造商全称:Infineon Technologies AG 功能描述:16-Bit CMOS Single-Chip Microcontroller |

| SABC167SR-LM | 制造商:Infineon Technologies AG 功能描述:MCU 16-bit C166 CISC/RISC ROMLess 5V 144-Pin MQFP |

发布紧急采购,3分钟左右您将得到回复。