- 您现在的位置:买卖IC网 > PDF目录97070 > SN74GTLPH16912DL (TEXAS INSTRUMENTS INC) GTL/TVC SERIES, 18-BIT REGISTERED TRANSCEIVER, TRUE OUTPUT, PDSO56 PDF资料下载

参数资料

| 型号: | SN74GTLPH16912DL |

| 厂商: | TEXAS INSTRUMENTS INC |

| 元件分类: | 总线收发器 |

| 英文描述: | GTL/TVC SERIES, 18-BIT REGISTERED TRANSCEIVER, TRUE OUTPUT, PDSO56 |

| 封装: | SSOP-56 |

| 文件页数: | 5/10页 |

| 文件大小: | 143K |

| 代理商: | SN74GTLPH16912DL |

SN74GTLPH16912

18-BIT LVTTL-TO-GTL+ UNIVERSAL BUS TRANSCEIVER

SCES288 – OCTOBER 1999

4

POST OFFICE BOX 655303

DALLAS, TEXAS 75265

absolute maximum ratings over operating free-air temperature range (unless otherwise noted)

Supply voltage range, VCC and BIAS VCC

–0.5 V to 4.6 V

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

Input voltage range, VI (see Note 1): A-port and control inputs

–0.5 V to 7 V

. . . . . . . . . . . . . . . . . . . . . . . . . . .

B port and VREF

–0.5 V to 4.6 V

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

Voltage range applied to any output in the high-impedance or power-off state, VO

(see Note 1): A port

–0.5 V to 7 V

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

B port

–0.5 V to 4.6 V

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

Current into any output in the low state, IO: A port

48 mA

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

B port

100 mA

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

Current into any A-port output in the high state, IO (see Note 2)

48 mA

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

Continuous current through each VCC or GND

±100 mA

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

Input clamp current, IIK (VI < 0)

–50 mA

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

Output clamp current, IOK (VO < 0)

–50 mA

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

Package thermal impedance,

θJA (see Note 3): DGG package

64

°C/W

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

DGV package

48

°C/W

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

DL package

56

°C/W

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

Storage temperature range, Tstg

–65

°C to 150°C

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

Stresses beyond those listed under “absolute maximum ratings” may cause permanent damage to the device. These are stress ratings only, and

functional operation of the device at these or any other conditions beyond those indicated under “recommended operating conditions” is not

implied. Exposure to absolute-maximum-rated conditions for extended periods may affect device reliability.

NOTES:

1. The input and output negative-voltage ratings may be exceeded if the input and output clamp-current ratings are observed.

2. This current flows only when the output is in the high state and VO > VCC.

3. The package thermal impedance is calculated in accordance with JESD 51.

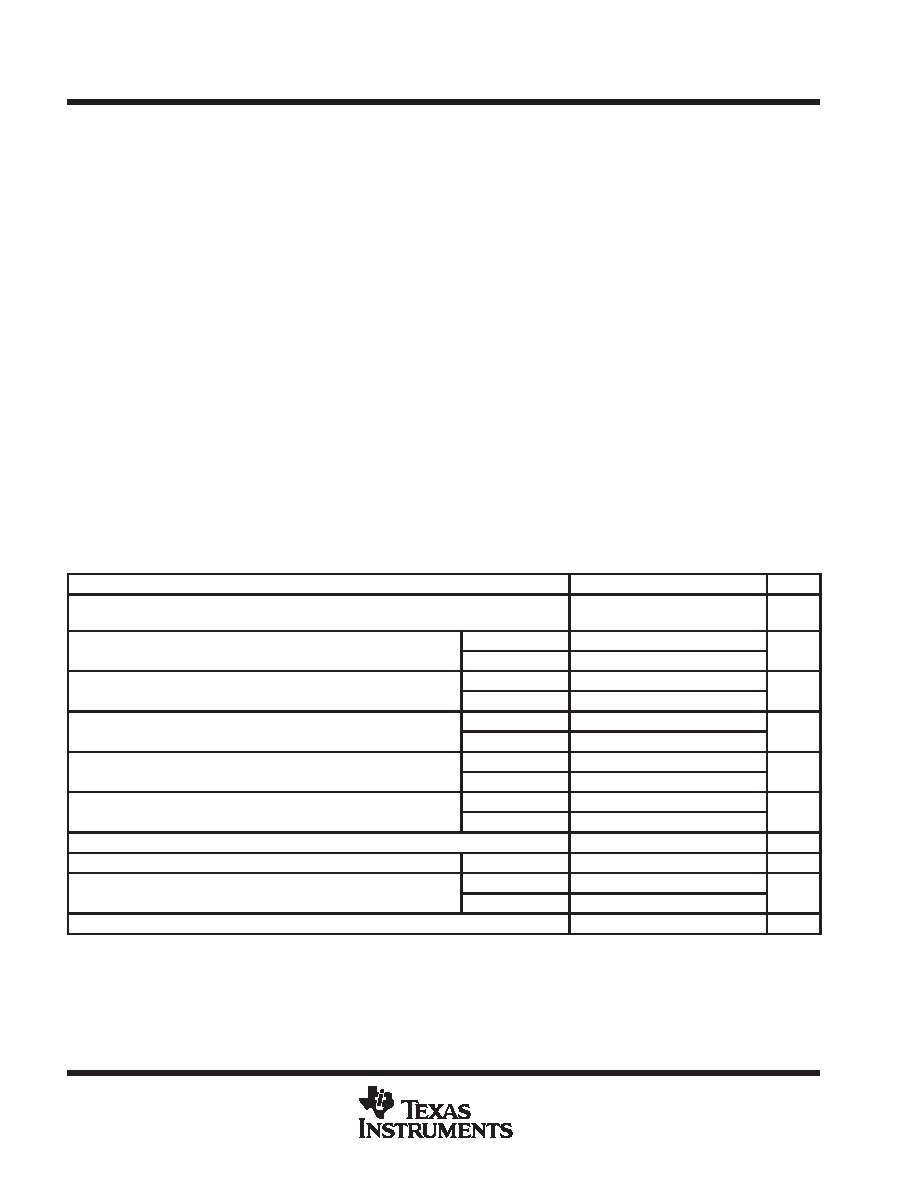

recommended operating conditions (see Notes 4 through 6)

MIN

NOM

MAX

UNIT

VCC,

BIAS VCC

Supply voltage

3.15

3.3

3.45

V

VTT

Termination voltage

GTL

1.14

1.2

1.26

V

VTT

Termination voltage

GTL+

1.35

1.5

1.65

V

VREF

Supply voltage

GTL

0.74

0.8

0.87

V

VREF

Supply voltage

GTL+

0.87

1

1.1

V

VI

Input voltage

B port

VTT

V

VI

Input voltage

Except B port

VCC

V

VIH

High level input voltage

B port

VREF+0.05

V

VIH

High-level input voltage

Except B port

2

V

VIL

Low level input voltage

B port

VREF–0.05

V

VIL

Low-level input voltage

Except B port

0.8

V

IIK

Input clamp current

–18

mA

IOH

High-level output current

A port

–24

mA

IOL

Low level output current

A port

24

mA

IOL

Low-level output current

B port

50

mA

TA

Operating free-air temperature

–40

85

°C

NOTES:

4. All unused inputs of the device must be held at VCC or GND to ensure proper device operation. Refer to the TI application report,

Implications of Slow or Floating CMOS Inputs, literature number SCBA004.

5. Normal connection sequence is GND first, BIAS VCC = 3.3 V second, and VCC = 3.3 V, I/O, control inputs, VTT and VREF (any order)

last. However, if the B-port I/O precharge is not required, the acceptable connection sequence is GND first and VCC = 3.3 V,

BIAS VCC = 3.3 V, I/O, control inputs, VTT and VREF (any order) last. When VCC is connected, the BIAS VCC circuitry is disabled.

6. VTT and RTT can be adjusted to accommodate backplane impedances as long as they do not exceed the DC absolute IOL ratings.

Similarly, VREF can be adjusted to optimize noise margins, but normally is 2/3 VTT.

PRODUCT

PREVIEW

相关PDF资料 |

PDF描述 |

|---|---|

| SN74GTLPH16945DGGR | GTLP SERIES, DUAL 8-BIT TRANSCEIVER, TRUE OUTPUT, PDSO48 |

| SN74GTLPH306PWLE | GTL/TVC SERIES, 8-BIT TRANSCEIVER, TRUE OUTPUT, PDSO24 |

| SN74H102N | TTL/H/L SERIES, NEGATIVE EDGE TRIGGERED J-K FLIP-FLOP, COMPLEMENTARY OUTPUT, PDIP14 |

| SN74H102J | TTL/H/L SERIES, NEGATIVE EDGE TRIGGERED J-K FLIP-FLOP, COMPLEMENTARY OUTPUT, CDIP14 |

| SN74H106N | TTL/H/L SERIES, DUAL NEGATIVE EDGE TRIGGERED J-K FLIP-FLOP, COMPLEMENTARY OUTPUT, PDIP16 |

相关代理商/技术参数 |

参数描述 |

|---|---|

| SN74GTLPH16912GR | 功能描述:转换 - 电压电平 18-Bit LVTTL-to-GTLP Univ Bus Transceiver RoHS:否 制造商:Micrel 类型:CML/LVDS/LVPECL to LVCMOS/LVTTL 传播延迟时间:1.9 ns 电源电流:14 mA 电源电压-最大:3.6 V 电源电压-最小:3 V 最大工作温度:+ 85 C 安装风格:SMD/SMT 封装 / 箱体:MLF-8 |

| SN74GTLPH16912VR | 功能描述:总线收发器 18-Bit LVTTL-to-GTLP Univ Bus Transceiver RoHS:否 制造商:Fairchild Semiconductor 逻辑类型:CMOS 逻辑系列:74VCX 每芯片的通道数量:16 输入电平:CMOS 输出电平:CMOS 输出类型:3-State 高电平输出电流:- 24 mA 低电平输出电流:24 mA 传播延迟时间:6.2 ns 电源电压-最大:2.7 V, 3.6 V 电源电压-最小:1.65 V, 2.3 V 最大工作温度:+ 85 C 封装 / 箱体:TSSOP-48 封装:Reel |

| SN74GTLPH16916GR | 功能描述:特定功能逻辑 17-Bit LVTTL-to-GTLP Univ Bus Trnscvr RoHS:否 制造商:Texas Instruments 产品: 系列:SN74ABTH18502A 工作电源电压:5 V 封装 / 箱体:LQFP-64 封装:Tube |

| SN74GTLPH16916VR | 功能描述:特定功能逻辑 17-Bit LVTTL-to-GTLP Univ Bus Trnscvr RoHS:否 制造商:Texas Instruments 产品: 系列:SN74ABTH18502A 工作电源电压:5 V 封装 / 箱体:LQFP-64 封装:Tube |

| SN74GTLPH16927GR | 功能描述:特定功能逻辑 18-Bit LVTTL-to-GTLP Bus Trnscvr RoHS:否 制造商:Texas Instruments 产品: 系列:SN74ABTH18502A 工作电源电压:5 V 封装 / 箱体:LQFP-64 封装:Tube |

发布紧急采购,3分钟左右您将得到回复。