- 您现在的位置:买卖IC网 > PDF目录373461 > SN74LVTH18516 (Texas Instruments, Inc.) 3.3-V ABT Scan Test Device With 18-Bit Universal Bus Transceivers(3.3VABT扫描测试装置(18位通用总线收发器)) PDF资料下载

参数资料

| 型号: | SN74LVTH18516 |

| 厂商: | Texas Instruments, Inc. |

| 英文描述: | 3.3-V ABT Scan Test Device With 18-Bit Universal Bus Transceivers(3.3VABT扫描测试装置(18位通用总线收发器)) |

| 中文描述: | 的3.3V ABT生根粉扫描测试设备与18位通用总线收发器(3.3VABT扫描测试装置(18位通用总线收发器)) |

| 文件页数: | 3/36页 |

| 文件大小: | 769K |

| 代理商: | SN74LVTH18516 |

第1页第2页当前第3页第4页第5页第6页第7页第8页第9页第10页第11页第12页第13页第14页第15页第16页第17页第18页第19页第20页第21页第22页第23页第24页第25页第26页第27页第28页第29页第30页第31页第32页第33页第34页第35页第36页

SN54LVTH18516, SN54LVTH182516, SN74LVTH18516, SN74LVTH182516

3.3-V ABT SCAN TEST DEVICES

WITH 18-BIT UNIVERSAL BUS TRANSCEIVERS

SCBS672B – AUGUST 1996 – REVISED JUNE 1997

3

POST OFFICE BOX 655303

DALLAS, TEXAS 75265

description (continued)

Data flow in each direction is controlled by latch-enable (LEAB and LEBA), clock-enable (CLKENAB and

CLKENBA), clock (CLKAB and CLKBA), select (SAB and SBA), and output-enable (OEAB and OEBA) inputs.

For A-to-B data flow, the device registers operate in the transparent mode when LEAB is high. When LEAB is

low, the A-bus data is latched while CLKENAB is high and/or CLKAB is held at a static low or high logic level.

Otherwise, if LEAB is low and CLKENAB is low, A-bus data is stored on a low-to-high transition of CLKAB. When

SAB is low, real-time A data is selected for presentation to the B bus (real-time data mode). When SAB is high,

stored A-data is selected for presentation to the B bus (stored data mode). When OEAB is low, the B outputs

are active. When OEAB is high, the B outputs are in the high-impedance state. B-to-A data flow is similar to

A-to-B data flow but uses the LEBA, CLKENBA, CLKBA, SBA, and OEBA inputs. Figure 1 illustrates the four

fundamental bus-management functions that are performed with the ’LVTH18516 and ’LVTH182516.

In the test mode, the normal operation of the SCOPE

universal bus transceivers is inhibited, and the test

circuitry is enabled to observe and control the I/O boundary of the device. When enabled, the test circuitry

performs boundary-scan test operations according to the protocol described in IEEE Std 1149.1-1990.

Four dedicated test pins are used to observe and control the operation of the test circuitry: test data input (TDI),

test data output (TDO), test mode select (TMS), and test clock (TCK). Additionally, the test circuitry performs

other testing functions such as parallel-signature analysis (PSA) on data inputs and pseudo-random pattern

generation (PRPG) from data outputs. All testing and scan operations are synchronized to the TAP interface.

Active bus-hold circuitry is provided to hold unused or floating data inputs at a valid logic level.

The B-port outputs of ’LVTH182516, which are designed to source or sink up to 12 mA, include equivalent 25-

series resistors to reduce overshoot and undershoot.

The SN54LVTH18516 and SN54LVTH182516 are characterized for operation over the full military temperature

range of –55

°

C to 125

°

C. The SN74LVTH18516 and SN74LVTH182516 are characterized for operation from

–40

°

C to 85

°

C.

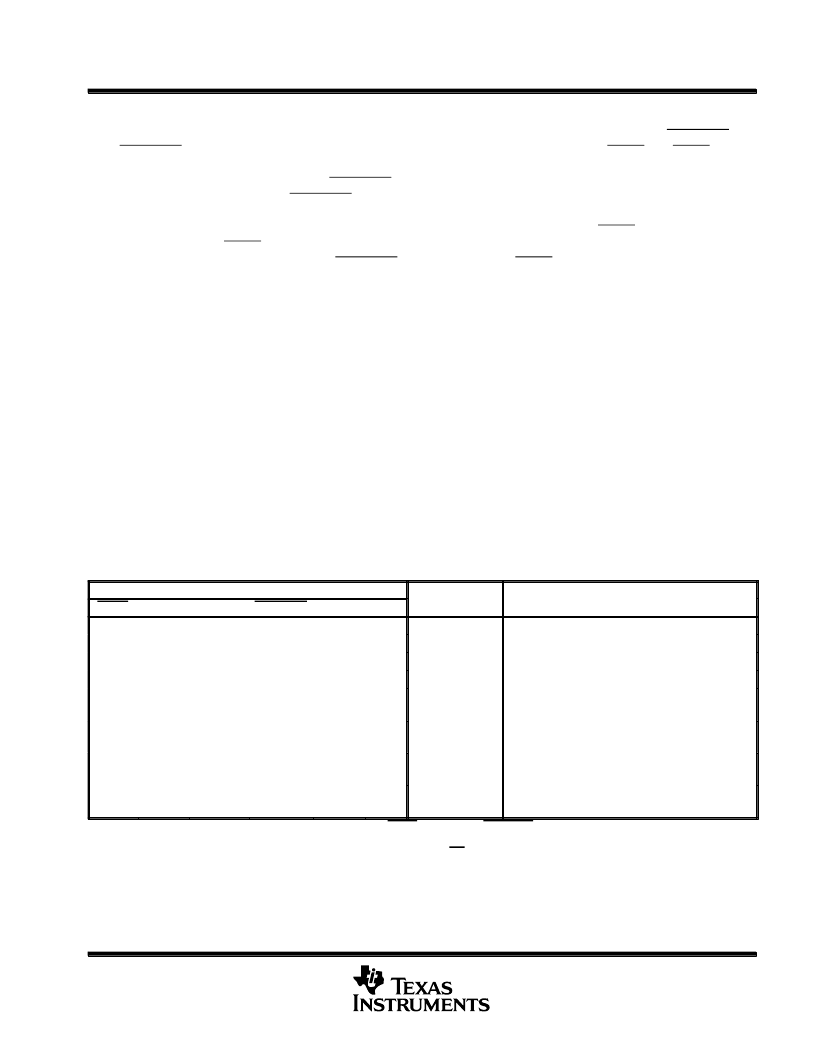

FUNCTION TABLE

(normal mode, each register)

INPUTS

OUTPUT

B

OPERATION OR FUNCTION

OEAB

SAB

LEAB

CLKENAB

CLKAB

A

H

X

X

X

X

X

Z

Isolation

L

L

X

X

X

L

L

Real-time A data to B bus

L

L

X

X

X

H

H

Real-time A data to B bus

L

H

X

X

X

X

QA0

Stored A data to B bus

X

X

H

X

X

X

Unspecified§

Store A data

(A

→

QA)

Store A data

(A

→

QA)

Hold A data

(QA0

→

QA)

Hold A data

(QA0

→

QA)

X

X

L

L

↑

X

Unspecified§

X

X

L

L

L

X

Unspecified§

X

X

L

H

X

X

Unspecified§

A-to-B data flow is shown. B-to-A data flow is similar but uses OEBA, SBA, LEBA, CLKENBA, and CLKBA.

Output level of internal register before the indicated steady-state input conditions are established.

§The data output functions are enabled or disabled by various signals at the OE and S inputs. Data input functions are always enabled.

P

相关PDF资料 |

PDF描述 |

|---|---|

| SN54LVTH182516 | 3.3-V ABT Scan Test Device With 18-Bit Universal Bus Transceivers(3.3VABT扫描测试装置(18位通用总线收发器)) |

| SN74LVTH182516 | 3.3-V ABT Scan Test Device With 18-Bit Universal Bus Transceivers(3.3V ABT扫描测试装置(18位通用总线收发器)) |

| SN54LVTH18640 | 3.3-V ABT Scan Test Device With 18-Bit Inverting Bus Transceivers(3.3V ABT 扫描检测装置(18位反相总线收发器)) |

| SN54LVTH182640 | 3.3-V ABT Scan Test Device With 18-Bit Inverting Bus Transceivers(3.3V ABT 扫描检测装置(18位反相总线收发器)) |

| SN74LVTH182640 | 3.3-V ABT Scan Test Device With 18-Bit Inverting Bus Transceivers(3.3V ABT 扫描检测装置(18位反相总线收发器)) |

相关代理商/技术参数 |

参数描述 |

|---|---|

| SN74LVTH18646APM | 功能描述:特定功能逻辑 3.3-V ABT w/18-Bit Trnscvr & Register RoHS:否 制造商:Texas Instruments 产品: 系列:SN74ABTH18502A 工作电源电压:5 V 封装 / 箱体:LQFP-64 封装:Tube |

| SN74LVTH18646APMG4 | 功能描述:特定功能逻辑 3.3-V ABT w/18-Bit Trnscvr & Register RoHS:否 制造商:Texas Instruments 产品: 系列:SN74ABTH18502A 工作电源电压:5 V 封装 / 箱体:LQFP-64 封装:Tube |

| SN74LVTH18652APM | 功能描述:特定功能逻辑 3.3-V ABT w/18-Bit Trnscvr & Register RoHS:否 制造商:Texas Instruments 产品: 系列:SN74ABTH18502A 工作电源电压:5 V 封装 / 箱体:LQFP-64 封装:Tube |

| SN74LVTH18652APMG4 | 功能描述:特定功能逻辑 3.3-V ABT w/18-Bit Trnscvr & Register RoHS:否 制造商:Texas Instruments 产品: 系列:SN74ABTH18502A 工作电源电压:5 V 封装 / 箱体:LQFP-64 封装:Tube |

| SN74LVTH2245DBR | 功能描述:总线收发器 Tri-St ABT Octal Bus RoHS:否 制造商:Fairchild Semiconductor 逻辑类型:CMOS 逻辑系列:74VCX 每芯片的通道数量:16 输入电平:CMOS 输出电平:CMOS 输出类型:3-State 高电平输出电流:- 24 mA 低电平输出电流:24 mA 传播延迟时间:6.2 ns 电源电压-最大:2.7 V, 3.6 V 电源电压-最小:1.65 V, 2.3 V 最大工作温度:+ 85 C 封装 / 箱体:TSSOP-48 封装:Reel |

发布紧急采购,3分钟左右您将得到回复。