- 您现在的位置:买卖IC网 > PDF目录98145 > ST72652C4T1/XXX (STMICROELECTRONICS) 8-BIT, MROM, MICROCONTROLLER, PQFP48 PDF资料下载

参数资料

| 型号: | ST72652C4T1/XXX |

| 厂商: | STMICROELECTRONICS |

| 元件分类: | 微控制器/微处理器 |

| 英文描述: | 8-BIT, MROM, MICROCONTROLLER, PQFP48 |

| 封装: | 7 X 7 MM, ROHS COMPLIANT, TQFP-48 |

| 文件页数: | 117/161页 |

| 文件大小: | 2656K |

| 代理商: | ST72652C4T1/XXX |

第1页第2页第3页第4页第5页第6页第7页第8页第9页第10页第11页第12页第13页第14页第15页第16页第17页第18页第19页第20页第21页第22页第23页第24页第25页第26页第27页第28页第29页第30页第31页第32页第33页第34页第35页第36页第37页第38页第39页第40页第41页第42页第43页第44页第45页第46页第47页第48页第49页第50页第51页第52页第53页第54页第55页第56页第57页第58页第59页第60页第61页第62页第63页第64页第65页第66页第67页第68页第69页第70页第71页第72页第73页第74页第75页第76页第77页第78页第79页第80页第81页第82页第83页第84页第85页第86页第87页第88页第89页第90页第91页第92页第93页第94页第95页第96页第97页第98页第99页第100页第101页第102页第103页第104页第105页第106页第107页第108页第109页第110页第111页第112页第113页第114页第115页第116页当前第117页第118页第119页第120页第121页第122页第123页第124页第125页第126页第127页第128页第129页第130页第131页第132页第133页第134页第135页第136页第137页第138页第139页第140页第141页第142页第143页第144页第145页第146页第147页第148页第149页第150页第151页第152页第153页第154页第155页第156页第157页第158页第159页第160页第161页

ST72651AR6

59/161

Doc ID 7215 Rev 4

Data Transfer Coprocessor (Cont’d)

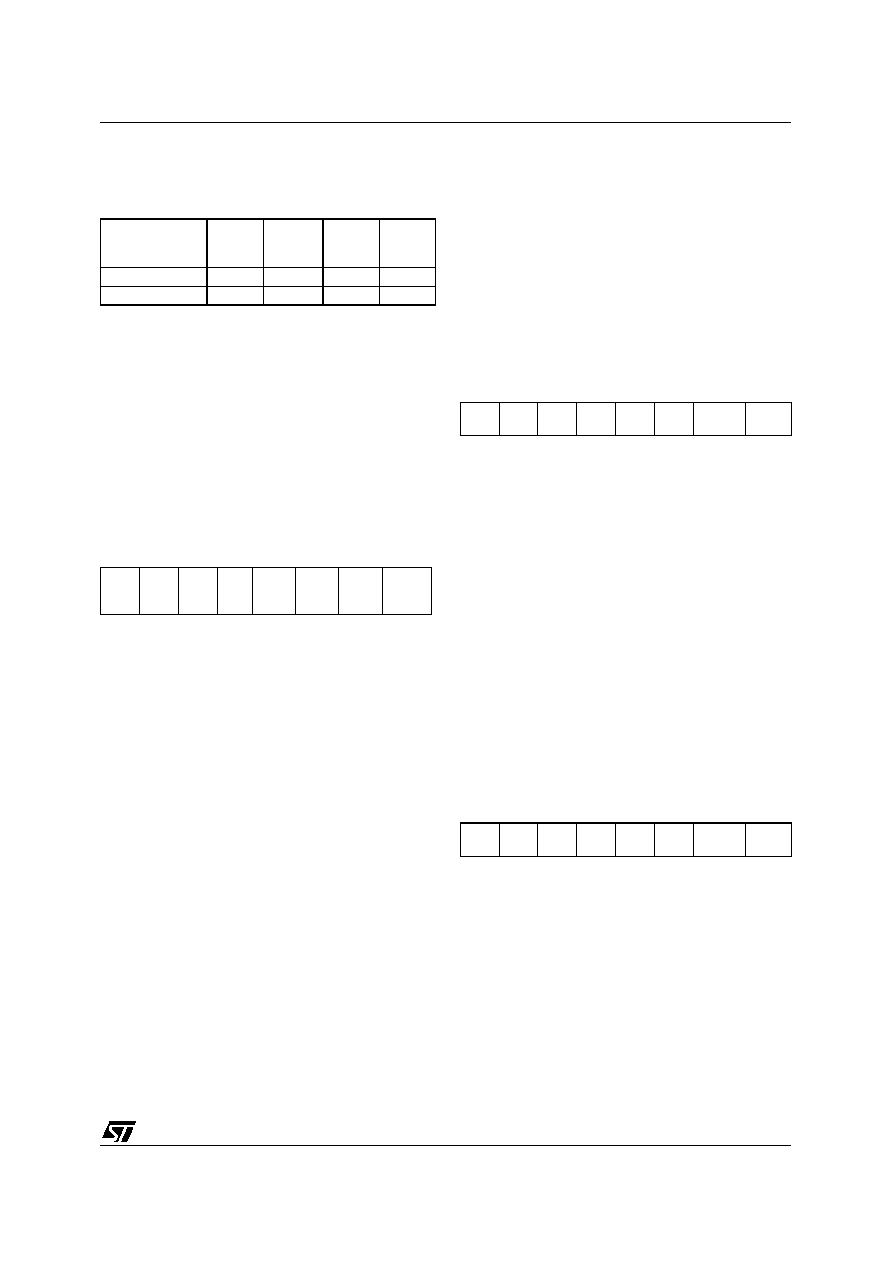

11.2.7 Interrupts

Note: The DTC interrupt events are connected to

the same interrupt vector (see Interrupts chapter).

They generate an interrupt if the corresponding

Enable Control Bit is set and the I-bit in the CC

register is reset (RIM instruction).

11.2.8 Register Description

DTC CONTROL REGISTER (DTCCR)

Read/Write

Reset Value: 0000 0000 (00h)

Bit 7:5 = Reserved. Must be left at reset value.

Bit 4 = ERREN Error Interrupt Enable

This bit is set and cleared by software.

0: Error interrupt disabled

1: Error interrupt enabled

Bit 3 = STOPEN Stop Interrupt Enable

This bit is set and cleared by software.

0: Stop interrupt disabled

1: Stop interrupt enabled

Bit 2 = LOAD Load Enable

This bit is set and cleared by software. It can only

be set while RUN=0.

0: Write access to DTC RAM disabled

1: Write access DTC RAM enabled

Bit 1 = INIT Initialization

This bit is set and cleared by software.

0: Do not copy DTCPR to DTC

1: Copy the DTCPR pointer to DTC

Bit 0 = RUN START/STOP Control

This bit is set and cleared by software. It can only

be set while LOAD=0. It is also cleared by hard-

ware when STOP=1

0: Stop DTC

1: Start DTC

DTC STATUS REGISTER (DTCSR)

Read/Write

Reset Value: 0000 0000 (00h)

Bit 7:2 = Reserved. Forced by hardware to 0.

Bit 1 = ERROR Error Flag

This bit is set by hardware and cleared by software

reading this register.

0: No Error event occurred

1: Error event occurred (DTC is running)

Bit 0 = STOP Stop Flag

This bit is set by hardware and cleared by software

reading this register.

0: No Stop event occurred

1: Stop event occurred (DTC terminated execution

at the current instruction)

DTC POINTER REGISTER (DTCPR)

Write Only

Reset Value: 0000 0000 (00h)

Bit 7:0 = PC[7:0] Pointer Register.

This register is written by software. It gives the ad-

dress of an entry point in the protocol software that

has previously been loaded in the DTC RAM.

Note: To start executing the function, after writing

this address, set the INIT bit.

Interrupt Event

Event

Flag

Enable

Control

Bit

Exit

from

Wait

Exit

from

Halt

Error

ERROR ERREN

Yes

No

Stop

STOP

STOPEN

Yes

No

70

000

ERR

EN

STOP

EN

LOAD

INIT

RUN

70

00

000

0

ERROR

STOP

70

MSB

LSB

1

相关PDF资料 |

PDF描述 |

|---|---|

| ST7267R8T1L/XXX | 16-BIT, MROM, 30 MHz, RISC MICROCONTROLLER, PQFP64 |

| ST7267C8T1/XXX | 16-BIT, MROM, 30 MHz, RISC MICROCONTROLLER, PQFP48 |

| ST72774S9T1/XXX | 8-BIT, MROM, 8 MHz, MICROCONTROLLER, PQFP44 |

| ST72E734J6D0 | 8-BIT, UVPROM, 8 MHz, MICROCONTROLLER, CDIP42 |

| ST72T774S9T1 | 8-BIT, OTPROM, 8 MHz, MICROCONTROLLER, PQFP44 |

相关代理商/技术参数 |

参数描述 |

|---|---|

| ST7265X-EVAL/MS | 制造商:STMicroelectronics 功能描述:ST6 EVAL BD - Bulk |

| ST7265X-EVAL/PFD | 制造商:STMicroelectronics 功能描述:USB FLASH EVAL - Bulk |

| ST7266 | 制造商:6940 功能描述:ST7266 |

| ST7267C8T1L | 制造商:STMicroelectronics 功能描述: |

| ST72681/R12 | 制造商:STMicroelectronics 功能描述:CONTROLLER FOR HIGH-PERFORMANCE BUS-POWERED USB 2.0 FLASH DR - Trays |

发布紧急采购,3分钟左右您将得到回复。