- 您现在的位置:买卖IC网 > PDF目录98149 > STP1080ABGA-83 SPECIALTY MICROPROCESSOR CIRCUIT, PBGA256 PDF资料下载

参数资料

| 型号: | STP1080ABGA-83 |

| 元件分类: | 微控制器/微处理器 |

| 英文描述: | SPECIALTY MICROPROCESSOR CIRCUIT, PBGA256 |

| 封装: | PLASTIC, BGA-256 |

| 文件页数: | 16/22页 |

| 文件大小: | 124K |

| 代理商: | STP1080ABGA-83 |

193

Companion Device for 167/200 MHz UltraSPARC-I Systems

UltraSPARC-I Data Buffer (UDB-I)

STP1080A

July 1997

TECHNICAL OVERVIEW

Data Buffering

UltraSPARC-I can have multiple outstanding request types, and be responding to multiple request types from

the Interconnect (receiving interrupts, delivering snoop data). However, except for noncacheable stores,

UltraSPARC-I can have only one outstanding request of each type. ‘Outstanding” implies that the address is

driven to the interconnect, but not the data.

There is storage for 1 64-byte external cache line. Eight outstanding noncacheable stores are allowed (16-bytes

of data due to compression) using the full interconnect bandwidth of 1 per interconnect cycle).

64-byte Buffers

64-byte buffers are provided for READs from the DataBus, and for SNOOPs and Writebacks from the

EcacheBus.

16-byte Buffers

The UDB can hold data for 8 noncacheable stores in progress.This store data comes from UltraSPARC-I’s store

buffer.

8-byte Buffers

Two interrupts, each consisting of three 64-bit packets, are also buffered in UDB. One buffer holds data going

from the cpu to the UPA, while the other holds data going from the UPA to the cpu.

Sub-Block Ordering

The UDB delivers and receives 16-byte subblocks in desired-word-rst order. Subsequent blocks are deliv-

ered in order, wrapping to the beginning of the block, if necessary. UDB does no data re-ordering.

All 64-byte write-backs from UltraSPARC-I are delivered starting with subblock 0.Data returned for snoops is

desired subblock rst also. The UDB chips supply pending CopyBack data in the correct order for a snoop.

ECC/Parity

ECC is 8 bits per 64 data bits. It is one of the single-error correcting, double error (and nibble-error) detecting

codes. The implementation has separate trees for ECC checking and correcting. Correctable errors are xed in

the same cycle as they are detected. The UDB will log the syndrome for the error (to help in diagnosing

multi-bit errors). There are some CSR read/write registers for enabling/disabling ECC. (accessible through

special ASI load/stores). There are two trap modes:

1. Trap on any ECC error

2. Trap on non-correctable ECC error

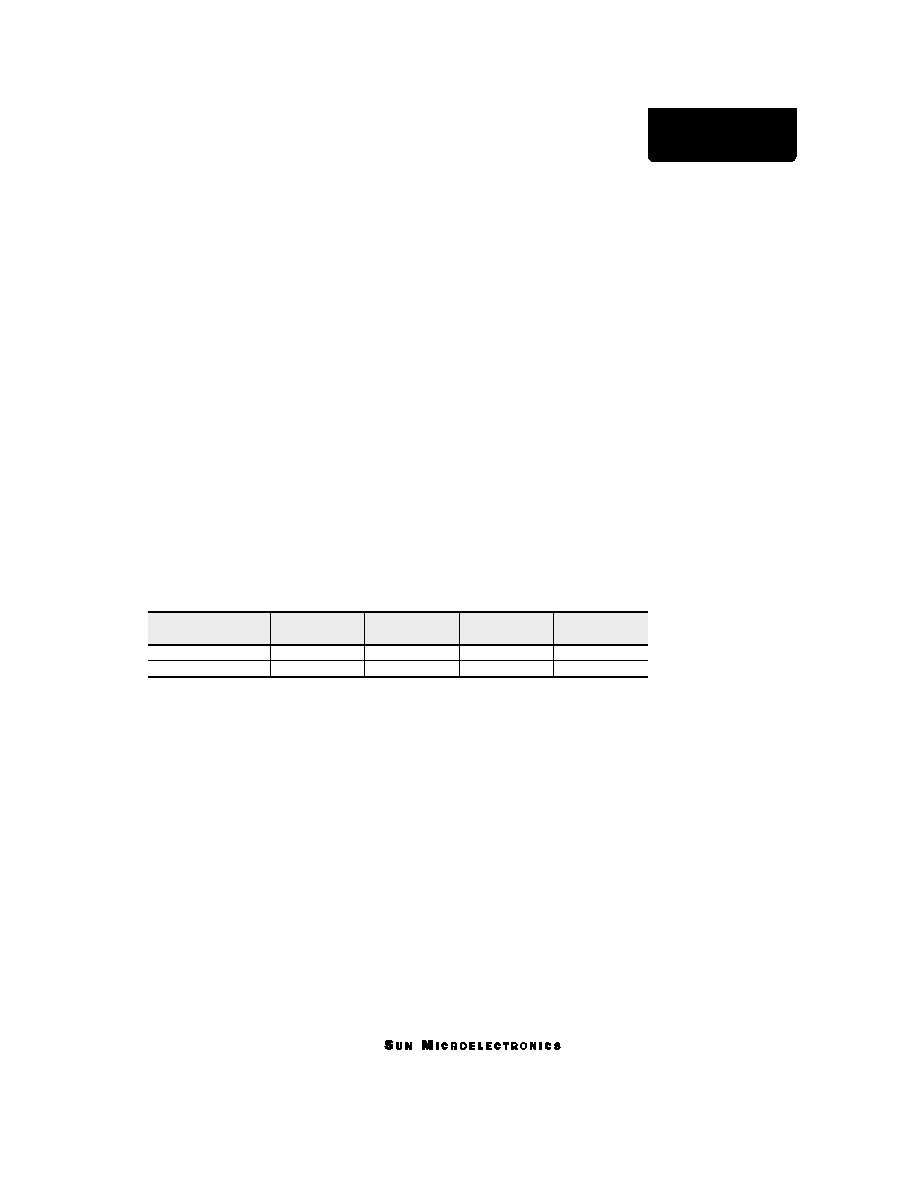

TABLE 1: Mondo Vector Format

Component

Interrupt _0

(Cycle 1)

Interrupt_1

(Cycle 2)

Interrupt_2

(Cycle 3)

Interrupt_3

(Cycle 4)

UDB_h

Data0

Data1

Data2

xxxxxx

UDB_l

xxxxxx

相关PDF资料 |

PDF描述 |

|---|---|

| STP1081ABGA-125 | SPECIALTY MICROPROCESSOR CIRCUIT, PBGA256 |

| STP1081ABGA-150 | SPECIALTY MICROPROCESSOR CIRCUIT, PBGA256 |

| STP1091PGA-75 | 2M X 1, CACHE CONTROLLER, CPGA376 |

| STP1100BGA-100 | 32-BIT, 100 MHz, RISC PROCESSOR, PBGA272 |

| STP2001QFP | MULTIFUNCTION PERIPHERAL, PQFP16 |

相关代理商/技术参数 |

参数描述 |

|---|---|

| STP1081ABGA-125 | 制造商:未知厂家 制造商全称:未知厂家 功能描述:Address/Data Buffer |

| STP1081ABGA-150 | 制造商:未知厂家 制造商全称:未知厂家 功能描述:ASIC |

| STP1091PGA-75 | 制造商:未知厂家 制造商全称:未知厂家 功能描述:Cache Controller |

| STP1091PGA-90 | 制造商:未知厂家 制造商全称:未知厂家 功能描述:Cache Controller |

| STP10LN80K5 | 功能描述:MOSFET N-CH 800V 8A TO-220 制造商:stmicroelectronics 系列:MDmesh?? 包装:管件 零件状态:有效 FET 类型:MOSFET N 通道,金属氧化物 FET 功能:标准 漏源极电压(Vdss):800V 电流 - 连续漏极(Id)(25°C 时):8A(Tc) 不同?Id,Vgs 时的?Rds On(最大值):630 毫欧 @ 4A,10V 不同 Id 时的 Vgs(th)(最大值):5V @ 100μA 不同 Vgs 时的栅极电荷(Qg):15nC @ 10V 不同 Vds 时的输入电容(Ciss):427pF @ 100V 功率 - 最大值:110W 工作温度:-55°C ~ 150°C(TJ) 安装类型:通孔 封装/外壳:TO-220-3 供应商器件封装:TO-220 标准包装:50 |

发布紧急采购,3分钟左右您将得到回复。