- 您现在的位置:买卖IC网 > PDF目录98149 > STP1080ABGA-83 SPECIALTY MICROPROCESSOR CIRCUIT, PBGA256 PDF资料下载

参数资料

| 型号: | STP1080ABGA-83 |

| 元件分类: | 微控制器/微处理器 |

| 英文描述: | SPECIALTY MICROPROCESSOR CIRCUIT, PBGA256 |

| 封装: | PLASTIC, BGA-256 |

| 文件页数: | 22/22页 |

| 文件大小: | 124K |

| 代理商: | STP1080ABGA-83 |

199

Companion Device for 167/200 MHz UltraSPARC-I Systems

UltraSPARC-I Data Buffer (UDB-I)

STP1080A

July 1997

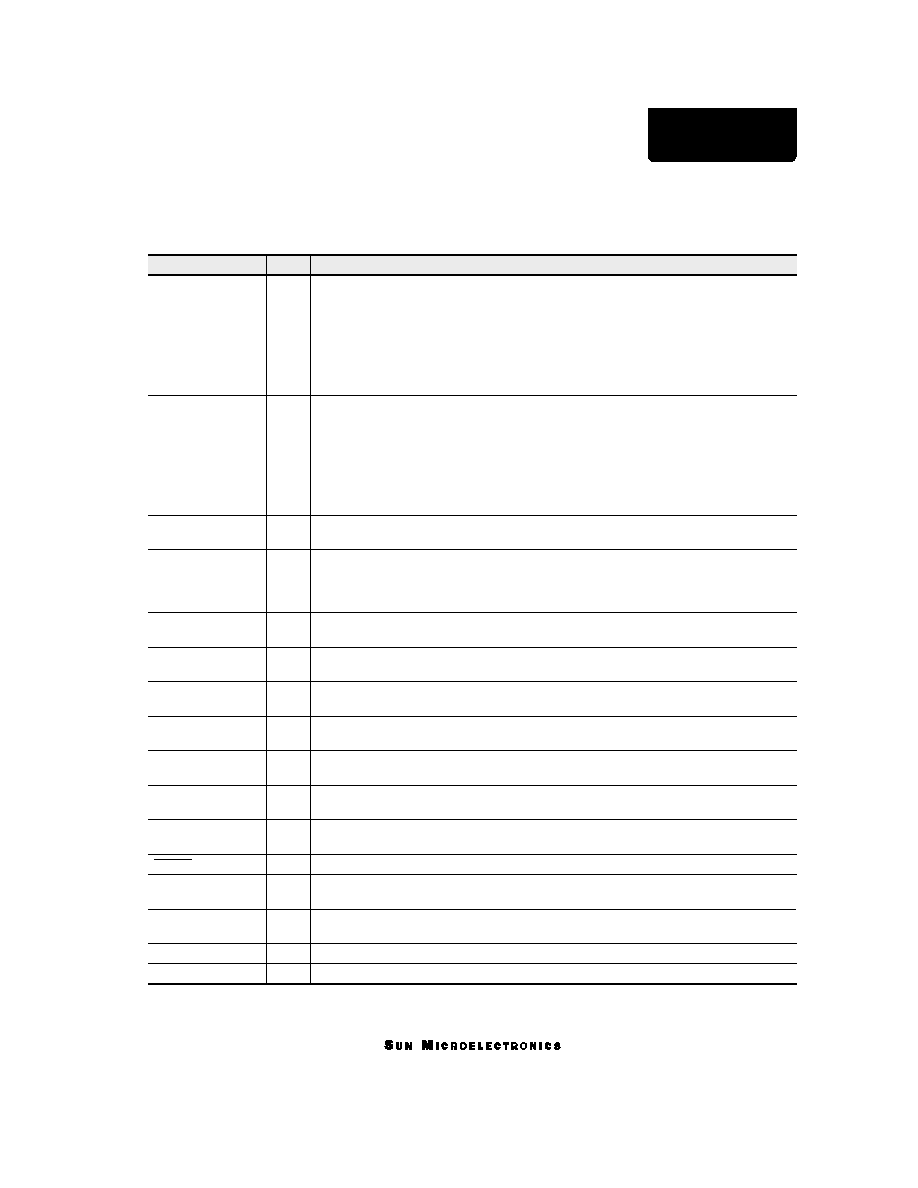

SIGNAL DESCRIPTIONS

Symbol

Type

Name and Function

EDATA[63:0]

I/O

The UDB chip does data transfers over this bus with both the E-Cache RAMs and the

UltraSPARC-I. On E-Cache misses, this bus is an output, and supplies data to the E-Cache

RAMs from one of its buffers. On E-Cache write-backs, data is transferred from the E-Cache

RAMs on this bus into one of the UDB chip buffers. Two UDB chips, each handle half the width

of the 128 bit data bus from the UltraSPARC-I and E-Cache. Non-cacheable loads and stores

transfer data directly between the UltraSPARC-I and the UDB chips on this bus. Also, special

ASI loads and stores from the UltraSPARC-I for writing/reading certain control/status registers

on the UDB chip for enabling/disabling ECC will also be supported over this bus.

EDPAR[7:0]

I/O

The UDB chip does data transfers over this bus with both the E-Cache RAMs and the

UltraSPARC-I. On E-Cache misses, this bus is an output, and supplies data to the E-Cache

RAMs from one of its buffers. On E-Cache write-backs, data is transferred from the E-Cache

RAMs on this bus into one of the UDB chip buffers. Two UDB chips, each handle half the width

of the 128 bit data bus from the UltraSPARC-I and E-Cache. Non-cacheable loads and stores

transfer data directly between the UltraSPARC-I and the UDB chips on this bus. Also, special

ASI loads and stores from the UltraSPARC-I for writing/reading certain control/status registers

on the UDB chip for enabling/disabling ECC will also be supported over this bus

SYSDATA[63:0]

I/O

The UDB chip does data transfers with the system interconnect over this bus. Data is transferred

at the system interconnect clock rate.

SYSECC[7:0]

I/O

Eight ECC check bits for the 64-bit data being transferred will be generated by the UDB chip, for

all UltraSPARC-I writes to the system interconnect, and the SYSECC bus will then be congured

as an output. On input, good ECC check bits generated by slaves will be transferred to the UDB

chip over this bus, and checked inside the UDB chip

UDB_CE

O

These are pins driven by the UDB to tell the UltraSPARC-I that it has detected a correctable ECC

error on the data that it received from the interconnect, i.e. a single bit error.

UDB_UE

O

This pin is driven by the UDB chip to tell the UltraSPARC-I that it has detected an uncorrectable

ECC error on the data that it received from the interconnect.

S_REPLY[3:0]

I

These pins are connected to an unidirectional4 bit bus that receives encoded acknowledges

from the System Controller in response to an address transaction sent out by UltraSPARC-I.

SYSID[4:0]

I

This bus is used to convey a ve-bit system node ID to the UDB chip from the system

interconnect.

SYSCLK[1:0]

I

This is an input from the clock controller chip, and has the same frequency as the system clock.

It is a differential, PECL clock

EXT_EVENT

I

This is an input signal used to indicate the clock should be stopped. It is a debug signal which is

set inactive on production systems. This signal powers down the STP1080 when asserted.

PLL_BYPASS

I

When asserted this pin caused the phase-lock loop to be bypassed. The clock from the

differential receiver is directly passed to the clock trunk.

RESET

I

This signal is asserted when an external reset request occurs.

UDB_CNTL[4:0]

I

These pins are used by the UltraSPARC-I to tell the UDB when to load its buffers from the

external cache data bus and when to drive the content of these buffers on to this bus.

UDB_H

I

This pin is hardwired to VDD for UDB_h (the UDB chip for the most signicant 72 bits) and to

GND for UDB_l (the UDB chip for the least signicant 72 bits).

EPD

I

This input from the CPU signals external power-down.

TDI

I

IEEE 1149 test data input. This pin is internally pulled to logic one when not driven.

相关PDF资料 |

PDF描述 |

|---|---|

| STP1081ABGA-125 | SPECIALTY MICROPROCESSOR CIRCUIT, PBGA256 |

| STP1081ABGA-150 | SPECIALTY MICROPROCESSOR CIRCUIT, PBGA256 |

| STP1091PGA-75 | 2M X 1, CACHE CONTROLLER, CPGA376 |

| STP1100BGA-100 | 32-BIT, 100 MHz, RISC PROCESSOR, PBGA272 |

| STP2001QFP | MULTIFUNCTION PERIPHERAL, PQFP16 |

相关代理商/技术参数 |

参数描述 |

|---|---|

| STP1081ABGA-125 | 制造商:未知厂家 制造商全称:未知厂家 功能描述:Address/Data Buffer |

| STP1081ABGA-150 | 制造商:未知厂家 制造商全称:未知厂家 功能描述:ASIC |

| STP1091PGA-75 | 制造商:未知厂家 制造商全称:未知厂家 功能描述:Cache Controller |

| STP1091PGA-90 | 制造商:未知厂家 制造商全称:未知厂家 功能描述:Cache Controller |

| STP10LN80K5 | 功能描述:MOSFET N-CH 800V 8A TO-220 制造商:stmicroelectronics 系列:MDmesh?? 包装:管件 零件状态:有效 FET 类型:MOSFET N 通道,金属氧化物 FET 功能:标准 漏源极电压(Vdss):800V 电流 - 连续漏极(Id)(25°C 时):8A(Tc) 不同?Id,Vgs 时的?Rds On(最大值):630 毫欧 @ 4A,10V 不同 Id 时的 Vgs(th)(最大值):5V @ 100μA 不同 Vgs 时的栅极电荷(Qg):15nC @ 10V 不同 Vds 时的输入电容(Ciss):427pF @ 100V 功率 - 最大值:110W 工作温度:-55°C ~ 150°C(TJ) 安装类型:通孔 封装/外壳:TO-220-3 供应商器件封装:TO-220 标准包装:50 |

发布紧急采购,3分钟左右您将得到回复。