参数资料

| 型号: | SY89230UMG |

| 厂商: | Micrel Inc |

| 文件页数: | 4/15页 |

| 文件大小: | 0K |

| 描述: | IC CLOCK DIVIDER LVPECL 16-MLF |

| 标准包装: | 100 |

| 系列: | Precision Edge® |

| 类型: | 时钟除法器 |

| PLL: | 无 |

| 输入: | CML,LVDS,PECL |

| 输出: | LVPECL |

| 电路数: | 1 |

| 比率 - 输入:输出: | 1:1 |

| 差分 - 输入:输出: | 是/是 |

| 频率 - 最大: | 3.2GHz |

| 除法器/乘法器: | 是/无 |

| 电源电压: | 2.375 V ~ 3.6 V |

| 工作温度: | -40°C ~ 85°C |

| 安装类型: | 表面贴装 |

| 封装/外壳: | 16-VFQFN 裸露焊盘,16-MLF? |

| 供应商设备封装: | 16-MLF?(3x3) |

| 包装: | 管件 |

| 产品目录页面: | 1090 (CN2011-ZH PDF) |

| 其它名称: | 576-2112-5 576-2112-5-ND 576-2964-5 |

12

Copyright 2005 Cirrus Logic, Inc.

DS651UM23

Version 2.3

CobraNet Hardware User’s Manual

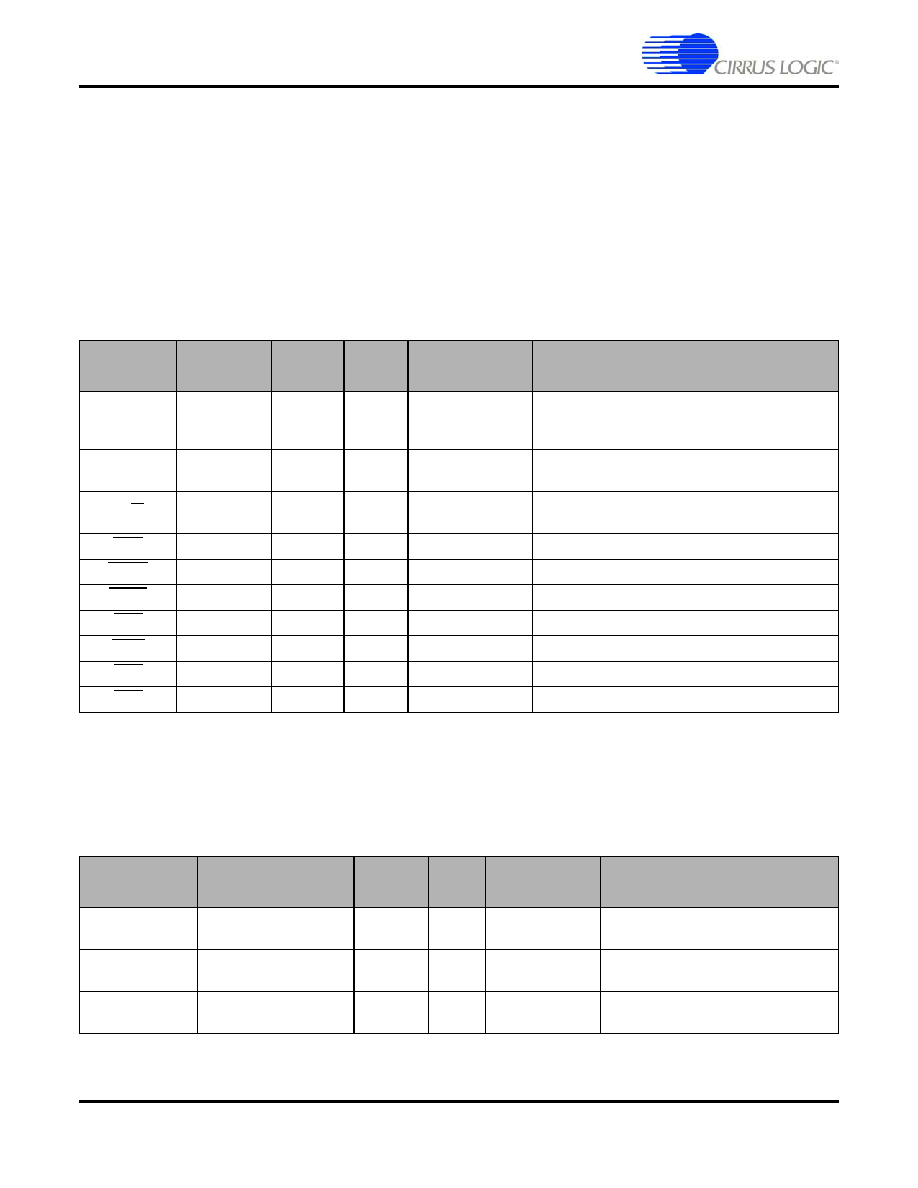

Pinout and Signal Descriptions

4.2

Signal Descriptions

4.2.1 Host Port Signals

The host port is used to manage and monitor the CobraNet interface. Electrical operation

and protocol is detailed in the "Host Management Interface (HMI)" on page 23 of this

Manual.

The host port can operate in two modes in order to accomodate Motorola or Intel style

interfaces. The default mode is Motorola. Intel mode is set via a firmware modification.

4.2.2 Asynchronous Serial Port (UART Bridge) Signals

Level-shifting drive circuits are typically required between these signals and any external

connections.

Table 2-1: Host Port Signals

Signal

Description

Direction

CM-2

Pin #

CS1810xx/

CS4961xx Pin #

Notes

HDATA[7:0]

Host Data

In/Out

J1:A19,

A[17:11]

111, 112, 114,

115, 117, 118,

102, 121

Host port data.

HADDR[3:0]

Host Address

In

J1:A20,

A[10:8]

105, 106, 109,110

Host port address.

HRW

Host

Direction

In

J1:A4

107

Host port transfer direction (Motorola mode).

HRD

Host Read

In

J1:A4

107

Host Read (Intel mode).

HREQ

Host Request

Out

J1:A6

140

Host port data request.

HACK

Host Alert

Out

J1:A3

102

Host port interrupt request.

HDS

Host Strobe

In

J1:A5

103

Host port strobe (Motorola mode).

HWR

Host Write

In

J1:A5

103

Host Write (Intel mode).

HEN

Host Enable

In

J1:A7

104

Host Port Enable.

HCS

Select

In

J1:A7

104

Select (Intel mode).

Signal

Description

Direction

CM-2

Pin #

CS1810xx/

CS4961xx Pin #

Notes

UART_RXD

Asynchronous Serial

Receive Data

In

J1:A1

26

Pull-up to VCC if unused.

UART_TXD

Asynchronous Serial

Transmit Data

Out

J1:B1

25

UART_TX_OE

Transmit Drive Enable

Out

J1:A2

23

Enable transmit (active high) drive for

two wire multi-drop interface.

相关PDF资料 |

PDF描述 |

|---|---|

| VE-JTN-MZ-S | CONVERTER MOD DC/DC 18.5V 25W |

| SY89545LMG TR | IC MUX 4:1 LVDS DIFF 3.3V 32-MLF |

| SY10EL34LZG | IC CLK GEN /2/4/8 3.3/5V 16-SOIC |

| ADF4156BRUZ | IC PLL FRAC-N FREQ SYNTH 16TSSOP |

| ADF4156BCPZ | IC PLL FRAC-N FREQ SYNTH 20LFCSP |

相关代理商/技术参数 |

参数描述 |

|---|---|

| SY89230UMG TR | 功能描述:时钟驱动器及分配 Divide-by-3 and 5 LVPECL Clock Divider with Internal Termination and FSI (3.2GHz) RoHS:否 制造商:Micrel 乘法/除法因子:1:4 输出类型:Differential 最大输出频率:4.2 GHz 电源电压-最大: 电源电压-最小:5 V 最大工作温度:+ 85 C 封装 / 箱体:SOIC-8 封装:Reel |

| SY89230UMGTR | 制造商:MICREL 制造商全称:Micrel Semiconductor 功能描述:3.2GHz Precision, LVPECL ÷3, ÷5 Clock Divider |

| SY89231U | 制造商:MICREL 制造商全称:Micrel Semiconductor 功能描述:1GHz Precision, LVPECL ±3, ±5 Clock Divider with Fail-Safe Input and Internal Termination |

| SY89231UMG | 功能描述:时钟驱动器及分配 Divide-by-3 and 5 LVDS Clock Divider with Internal Termination and FSI (3.2GHz) RoHS:否 制造商:Micrel 乘法/除法因子:1:4 输出类型:Differential 最大输出频率:4.2 GHz 电源电压-最大: 电源电压-最小:5 V 最大工作温度:+ 85 C 封装 / 箱体:SOIC-8 封装:Reel |

| SY89231UMG TR | 功能描述:时钟驱动器及分配 Divide-by-3 and 5 LVDS Clock Divider with Internal Termination and FSI (3.2GHz) RoHS:否 制造商:Micrel 乘法/除法因子:1:4 输出类型:Differential 最大输出频率:4.2 GHz 电源电压-最大: 电源电压-最小:5 V 最大工作温度:+ 85 C 封装 / 箱体:SOIC-8 封装:Reel |

发布紧急采购,3分钟左右您将得到回复。