- 您现在的位置:买卖IC网 > PDF目录225277 > T431616D (Electronic Theatre Controls, Inc.) 1M x 16 SDRAM 512K x 16bit x 2Banks Synchronous DRAM PDF资料下载

参数资料

| 型号: | T431616D |

| 厂商: | Electronic Theatre Controls, Inc. |

| 英文描述: | 1M x 16 SDRAM 512K x 16bit x 2Banks Synchronous DRAM |

| 中文描述: | 100万× 16内存为512k × 16Bit的X 2Banks同步DRAM |

| 文件页数: | 1/74页 |

| 文件大小: | 781K |

| 代理商: | T431616D |

当前第1页第2页第3页第4页第5页第6页第7页第8页第9页第10页第11页第12页第13页第14页第15页第16页第17页第18页第19页第20页第21页第22页第23页第24页第25页第26页第27页第28页第29页第30页第31页第32页第33页第34页第35页第36页第37页第38页第39页第40页第41页第42页第43页第44页第45页第46页第47页第48页第49页第50页第51页第52页第53页第54页第55页第56页第57页第58页第59页第60页第61页第62页第63页第64页第65页第66页第67页第68页第69页第70页第71页第72页第73页第74页

TE

CH

tm

T431616D/E

TM Technology Inc. reserves the right

P. 1

Publication Date: FEB. 2007

to change products or specifications without notice.

Revision: A

SDRAM

1M x 16 SDRAM

512K x 16bit x 2Banks Synchronous DRAM

FEATURES

Fast access time: 5/6/7 ns

Fast clock rate: 200/166/143 MHz

Self refresh mode: standard and low power

Internal pipelined architecture

512K word x 16-bit x 2-bank

Programmable Mode registers

- CAS# Latency: 1, 2, or 3

- Burst Length: 1, 2, 4, 8, or full page

- Burst Type: interleaved or linear burst

- Burst stop function

Individual byte controlled by LDQM and UDQM

Auto Refresh and Self Refresh

4096 refresh cycles/64ms

CKE power down mode

JEDEC standard +3.3V±0.3V power supply

Interface: LVTTL

50-pin 400 mil plastic TSOP II package

60-ball, 6.4x10.1mm VFBGA package

Lead Free Package available for both TSOP II and

VFBGA

Low Operating Current for T431616E

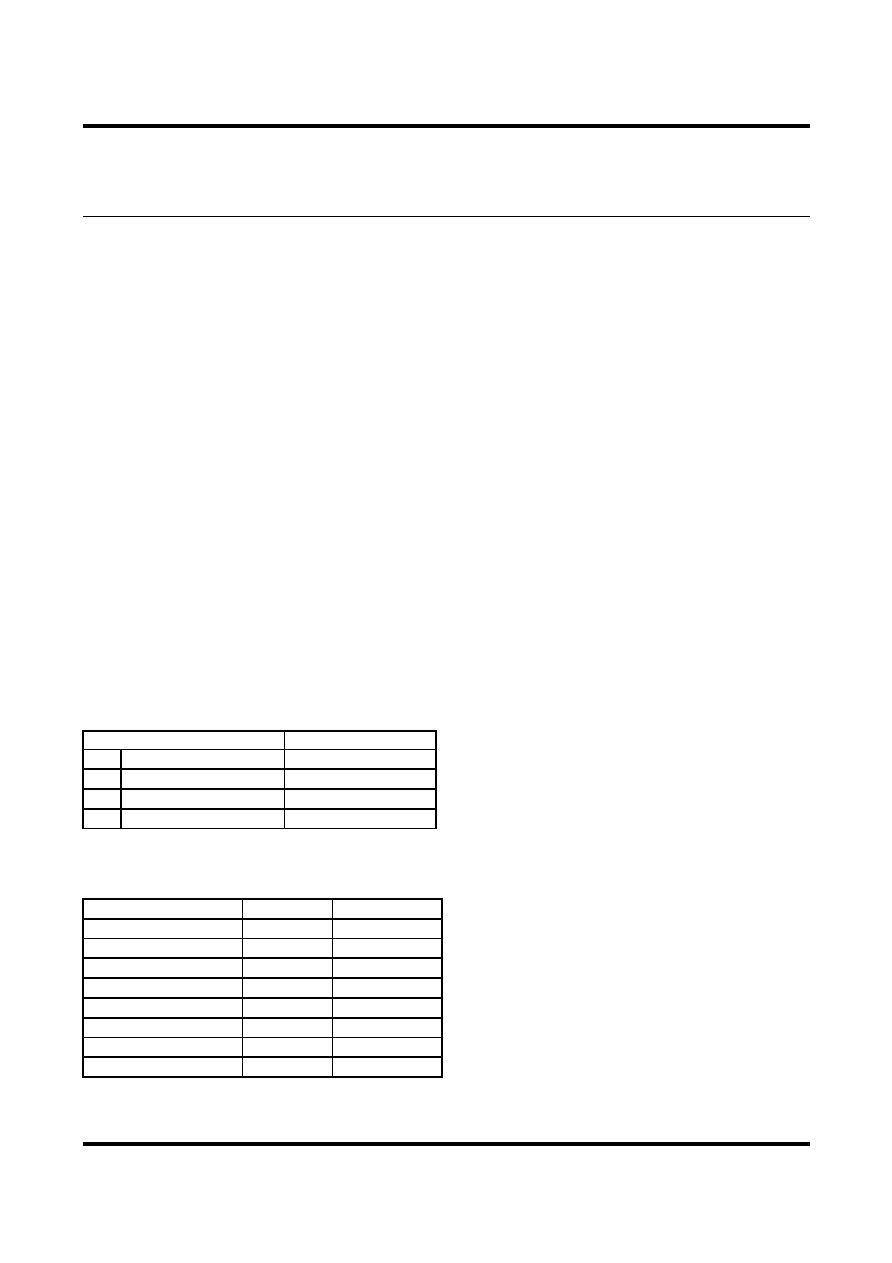

Key Specifications

T431616D/E

-5/6/7

tCK3 Clock Cycle time(min.)

5/6/7ns

tRAS Row Active time(max.)

35/42/42 ns

tAC3 Access time from CLK(max.)

4.5/5/5.5 ns

tRC

Row Cycle time(min.)

48/54/63 ns

ORDERING INFORMATION

Part Number

Frequency

Package

T431616D-5S/C

200MHz

TSOP II / VFBGA

T431616D-5SG/CG

200MHz

TSOP II / VFBGA

T431616D-6S/C

166MHz

TSOP II / VFBGA

T431616D-6SG/CG

166MHz

TSOP II / VFBGA

T431616D-7S/C

143MHz

TSOP II / VFBGA

T431616D-7SG/CG

143MHz

TSOP II / VFBGA

T431616E-7S/C

143MHz

TSOP II / VFBGA

T431616E-7SG/CG

143MHz

TSOP II / VFBGA

G : indicates Lead Free Package

GRNERAL DESCRIPTION

The T431616D/E SDRAM is a high-speed CMOS

synchronous DRAM containing 16 Mbits. It is internally

configured as a dual 512K word x 16 DRAM with a

synchronous interface (all signals are registered on the

positive edge of the clock signal, CLK). Each of the

512K x 16 bit banks is organized as 2048 rows by 256

columns by 16 bits. Read and write accesses to the

SDRAM are burst oriented; accesses start at a selected

location and continue for a programmed number of

locations in a programmed sequence. Accesses begin

with the registration of a BankActivate command which

is then followed by a Read or Write command.

The T431616D/E provides for programmable Read

or Write burst lengths of 1, 2, 4, 8, or full page, with a

burst termination option. An auto precharge function

may be enabled to provide a self-timed row precharge

that is initiated at the end of the burst sequence. The

refresh functions, either Auto or Self Refresh are easy to

use. By having a programmable mode register, the

system can choose the most suitable modes to maximize

its performance. These devices are well suited for

applications requiring high memory bandwidth and

particularly well suited to high performance PC

applications

相关PDF资料 |

PDF描述 |

|---|---|

| T431616E | 1M x 16 SDRAM 512K x 16bit x 2Banks Synchronous DRAM |

| T450N | 0 MHz - 10000 MHz 50 ohm RF/MICROWAVE TERMINATION |

| T451N | 0 MHz - 10000 MHz 50 ohm RF/MICROWAVE TERMINATION |

| T523-020.00M | TCXO, CLIPPED SINE OUTPUT, 20 MHz |

| T613-020.00M | TCXO, CLIPPED SINE OUTPUT, 20 MHz |

相关代理商/技术参数 |

参数描述 |

|---|---|

| T431616D-5C | 制造商:TMT 制造商全称:TMT 功能描述:1M x 16 SDRAM 512K x 16bit x 2Banks Synchronous DRAM |

| T431616D-5CG | 制造商:TMT 制造商全称:TMT 功能描述:1M x 16 SDRAM 512K x 16bit x 2Banks Synchronous DRAM |

| T431616D-5S | 制造商:TMT 制造商全称:TMT 功能描述:1M x 16 SDRAM 512K x 16bit x 2Banks Synchronous DRAM |

| T431616D-5SG | 制造商:TMT 制造商全称:TMT 功能描述:1M x 16 SDRAM 512K x 16bit x 2Banks Synchronous DRAM |

| T431616D-6C | 制造商:TMT 制造商全称:TMT 功能描述:1M x 16 SDRAM 512K x 16bit x 2Banks Synchronous DRAM |

发布紧急采购,3分钟左右您将得到回复。