- 您现在的位置:买卖IC网 > PDF目录297494 > TC55VBM316ATGN40 512K X 16 STANDARD SRAM, 55 ns, PDSO48 PDF资料下载

参数资料

| 型号: | TC55VBM316ATGN40 |

| 元件分类: | SRAM |

| 英文描述: | 512K X 16 STANDARD SRAM, 55 ns, PDSO48 |

| 封装: | 12 X 20 MM, 0.50 MM PITCH, PLASTIC, TSOP1-48 |

| 文件页数: | 1/15页 |

| 文件大小: | 209K |

| 代理商: | TC55VBM316ATGN40 |

TC55VBM316ATGN/ASGN40,55

2002-05-14

1/15

TENTATIVE

TOSHIBA MOS DIGITAL INTEGRATED CIRCUIT SILICON GATE CMOS

524,288-WORD BY 16-BIT/1,048,576-WORD BY 8-BIT FULL CMOS STATIC RAM

DESCRIPTION

The TC55VBM316ATGN/ASGN is a 8,388,608-bit static random access memory (SRAM) organized as 524,288

words by 16 bits/1,048,576 words by 8 bits. Fabricated using Toshiba's CMOS Silicon gate process technology, this

device operates from a single 2.3 to 3.6 V power supply. Advanced circuit technology provides both high speed and

low power at an operating current of 3 mA/MHz and a minimum cycle time of 40 ns. It is automatically placed in

low-power mode at 0.7

A standby current (at VDD = 3 V, Ta = 25°C, typical) when chip enable ( CE1 ) is asserted

high or (CE2) is asserted low. There are three control inputs. CE1 and CE2 are used to select the device and for

data retention control, and output enable ( OE ) provides fast memory access. Data byte control pin ( LB , UB )

provides lower and upper byte access. This device is well suited to various microprocessor system applications

where high speed, low power and battery backup are required. And, with a guaranteed operating extreme

temperature range of

40° to 85°C, the TC55VBM316ATGN/ASGN can be used in environments exhibiting extreme

temperature conditions. The TC55VBM316ATGN/ASGN is available in a plastic 48-pin thin-small-outline package

(TSOP).

FEATURES

Low-power dissipation

Operating: 9 mW/MHz (typical)

Single power supply voltage of 2.3 to 3.6 V

Power down features using CE1 and CE2

Data retention supply voltage of 1.5 to 3.6 V

Direct TTL compatibility for all inputs and outputs

Wide operating temperature range of 40° to 85°C

Standby Current (maximum):

3.6 V

10

A

3.0 V

5

A

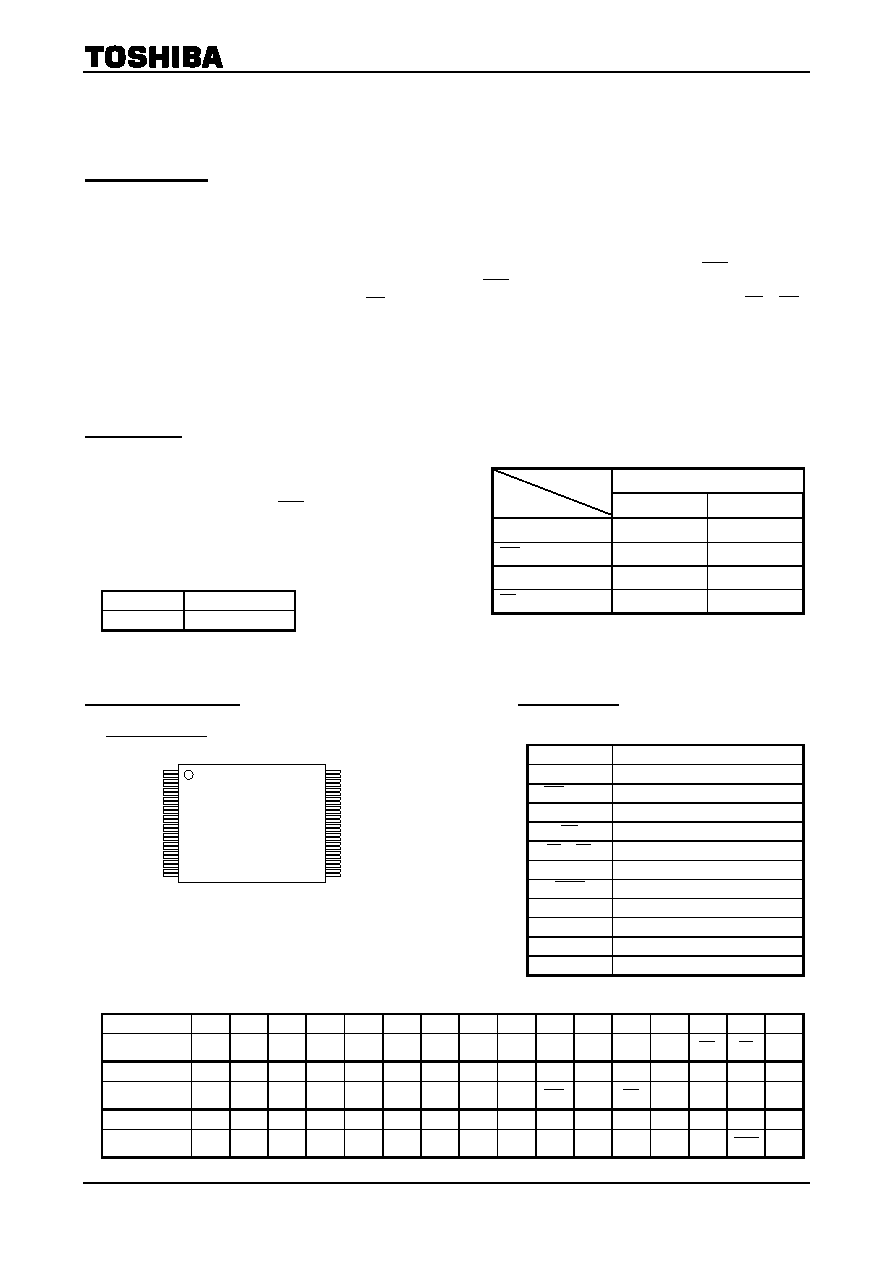

PIN ASSIGNMENT (TOP VIEW)

PIN NAMES

48 PIN TSOP

A0~A18

Address Inputs (Word Mode)

A-1~A18

Address Inputs (Byte Mode)

1

CE

, CE2

Chip Enable

R/W

Read/Write Control

OE

Output Enable

LB , UB

Data Byte Control

I/O1~I/O16

Data Inputs/Outputs

BYTE

Byte (

×8 mode) Enable

VDD

Power

GND

Ground

NC

No Connection

OP*

Option

*: OP pin must be open or connected to GND.

Pin No.

1

2

3

4

5

6

7

8

9

10

11

12

13

14

15

16

Pin Name

A15

A14

A13

A12

A11

A10

A9

A8

NC

R/W

CE2

OP

UB

LB

A18

Pin No.

17

18

19

20

21

22

23

24

25

26

27

28

29

30

31

32

Pin Name

A17

A7

A6

A5

A4

A3

A2

A1

A0

1

CE

GND

OE

I/O1

I/O9

I/O2

I/O10

Pin No.

33

34

35

36

37

38

39

40

41

42

43

44

45

46

47

48

Pin Name

I/O3

I/O11

I/O4

I/O12

VDD

I/O5

I/O13

I/O6

I/O14

I/O7

I/O15

I/O8

I/O16

/A-1

GND

BYTE

A16

Access Times (maximum):

TC55VBM316ATGN/ASGN

40

55

Access Time

40 ns

55 ns

1

CE

Access Time

40 ns

55 ns

CE2

Access Time

40 ns

55 ns

OE

Access Time

25 ns

30 ns

Package:

TSOPⅠ48-P-1220-0.50 (ATGN) (Weight:

g typ)

TSOPⅠ48-P-1214-0.50 (ASGN) (Weight:

g typ)

(Normal)

25

48

24

1

相关PDF资料 |

PDF描述 |

|---|---|

| TC55VD1618FF-133 | 1M X 18 STANDARD SRAM, 4.2 ns, PQFP100 |

| TC55VZM216AFTN12 | 256K X 16 CACHE SRAM, 12 ns, PDSO44 |

| TC59SM808BFTL-70 | 32M X 8 SYNCHRONOUS DRAM, 5.4 ns, PDSO54 |

| TC643VPA | BRUSHLESS DC MOTOR CONTROLLER, PDIP8 |

| TC74A23F | RELAY SWITCH; N RELAY SWITCH; FREQUENCY RANGE: DC-4 GHz; SWICH TYPE: SPDT; FEATURE: FAILSAFE; ACTUATING VOLTAGE: 12; VSWR: 1.20:1 @ 4 GHz |

相关代理商/技术参数 |

参数描述 |

|---|---|

| TC55VBM416AFTN55 | 功能描述:IC SRAM 16MBIT 55NS 48TSOP RoHS:否 类别:集成电路 (IC) >> 存储器 系列:- 标准包装:576 系列:- 格式 - 存储器:闪存 存储器类型:闪存 - NAND 存储容量:512M(64M x 8) 速度:- 接口:并联 电源电压:2.7 V ~ 3.6 V 工作温度:-40°C ~ 85°C 封装/外壳:48-TFSOP(0.724",18.40mm 宽) 供应商设备封装:48-TSOP 包装:托盘 其它名称:497-5040 |

| TC55VBM416ATGN55LA | 制造商:Toshiba 功能描述:Cut Tape |

| TC55VCM208ASTN40 | 制造商:TOSHIBA 制造商全称:Toshiba Semiconductor 功能描述:524,288-WORD BY 8-BIT FULL CMOS STATIC RAM |

| TC55VCM208ASTN55 | 制造商:TOSHIBA 制造商全称:Toshiba Semiconductor 功能描述:524,288-WORD BY 8-BIT FULL CMOS STATIC RAM |

| TC55VCM216ASTN40 | 制造商:TOSHIBA 制造商全称:Toshiba Semiconductor 功能描述:TENTATIVE TOSHIBA MOS DIGITAL INTEGRATED CIRCUIT SILICON GATE CMOS |

发布紧急采购,3分钟左右您将得到回复。