- 您现在的位置:买卖IC网 > PDF目录98215 > TFP501PZP (TEXAS INSTRUMENTS INC) SPECIALTY CONSUMER CIRCUIT, PQFP100 PDF资料下载

参数资料

| 型号: | TFP501PZP |

| 厂商: | TEXAS INSTRUMENTS INC |

| 元件分类: | 消费家电 |

| 英文描述: | SPECIALTY CONSUMER CIRCUIT, PQFP100 |

| 封装: | 14 X 14 MM, 1 MM HEIGHT, 0.50 MM PITCH, GREEN, PLASTIC, HTQFP-100 |

| 文件页数: | 5/24页 |

| 文件大小: | 373K |

| 代理商: | TFP501PZP |

TFP501

PanelBus HDCP DIGITAL RECEIVER

SLDS127B JULY 2001 REVISED AUGUST 2002

13

POST OFFICE BOX 655303

DALLAS, TEXAS 75265

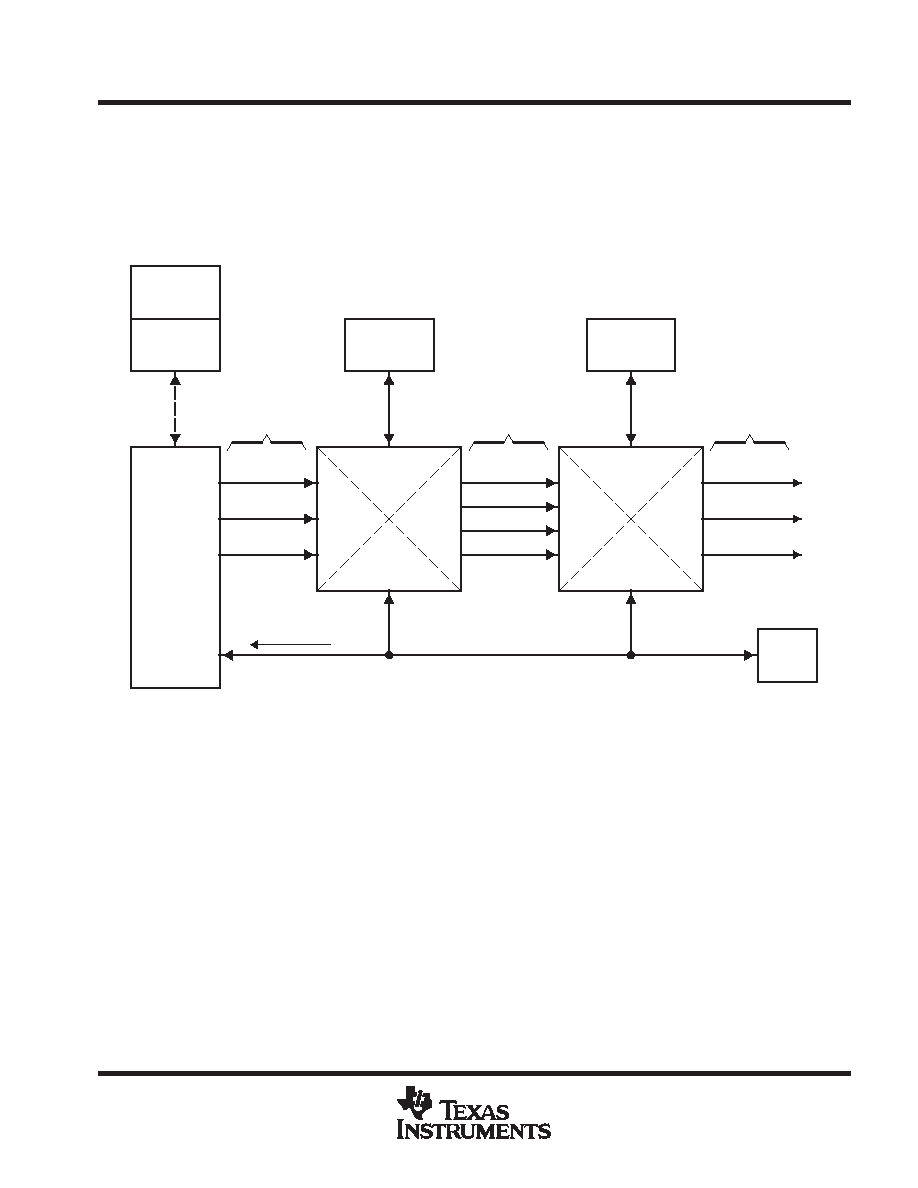

high-bandwidth digital content protection (HDCP) overview (continued)

The HDCP keys must also be protected from access. TI has chosen to avoid the inconvenience and possible

circuit board damage from using epoxy or other barriers between the EEPROM and DVI receiver. An encryption

scheme is used to protect the HDCP device key values passing from an off-chip EEPROM to the HDCP receiver

via a dedicated I2C interface. When the HDCP device keys are needed, the encrypted values are read from the

EEPROM, decrypted, and used to enable HDCP functionality. TI’s HDCP solution provides real advantages with

respect to lower systems level cost, ease of implementation, high performance, and exceptional security.

S/W

Application

Program

Upstream

Decrypt

CPU

and

North

Bridge

and

Graphics

Controller

TFP510

DVI-HDCP TX

(PC’s DVI Output)

PROM

Key

Decrypt

C Keys and KSV

Upstream

Encrypt

DE

Pixel Data

Clock

Input

Stream

Encrypted Keys

A Keys and KSV

D Keys and KSV

I2C

Encrypted M0

I2C

TFP501

DVI-HDCP RX

(Display’s DVI Input)

PROM

Key

Decrypt

I2C

Slave I/F

Channel 2

Channel 0

Channel C

HDCP Encrypted

TMDS Link

Encrypted Keys

B Keys and KSV

I2C

Channel 1

EDID

PROM

Control and Authentication and Key Exchange

KSV = Key Selection Vector

M0 = 64-Bit Secret Value

DE

Pixel Data

Clock

Output

Stream

T

.M.D.S.

Decode

HDPC

Decrypt

HDCP

Encrypt

T

.M.D.S.

Encode

Figure 13. TI’s HDCP Implementation for PC and Display System

TFP501 clocking and data synchronization

The TFP501 receives a clock reference from the DVI transmitter, such as the TFP510, that has a period equal

to the pixel time, t(pixel). The frequency of this clock is also referred to as the pixel rate. Since the T.M.D.S.

encoded data on Rx[2:0] contains 10 bits per 8-bit pixel, it follows that the Rx[2:0] serial bit rate is 10 times the

pixel rate. For example, the required pixel rate to support an UXGA resolution with 60 Hz refresh rate is

165 MHz. The T.M.D.S. serial bit rate is 10x the pixel rate or 1.65 Gb/s. Due to the transmission of this high speed

digital bit stream on three separate channels (or twisted-pair wires) of long distances (35 meters), phase

synchronization between the data steams and the input reference clock is not assured. In addition, skew

between the three data channels is common. The TFP501 uses a 4x oversampling scheme of the input data

streams to achieve reliable synchronization with up to 1-T(pixel) channel-to-channel skew tolerance.

Accumulated jitter on the clock and data lines due to reflections and external noise sources is also typical of

high-speed serial data transmission. The TFP501 is designed for high jitter tolerance.

相关PDF资料 |

PDF描述 |

|---|---|

| TFP503PZPG4 | SPECIALTY CONSUMER CIRCUIT, PQFP100 |

| TFP503PZP | SPECIALTY CONSUMER CIRCUIT, PQFP100 |

| TFP510PAPG4 | SPECIALTY CONSUMER CIRCUIT, PQFP64 |

| TFP510PAP | SPECIALTY CONSUMER CIRCUIT, PQFP64 |

| TFP513PAPG4 | SPECIALTY CONSUMER CIRCUIT, PQFP64 |

相关代理商/技术参数 |

参数描述 |

|---|---|

| TFP501PZPG4 | 制造商:Texas Instruments 功能描述:PNL BUS HDCP DGTL RCVR 100HTQFP - Rail/Tube |

| TFP503 | 制造商:TI 制造商全称:Texas Instruments 功能描述:PANELBUS HDCP DIGITAL RECEIVER |

| TFP503PZP | 制造商:Texas Instruments 功能描述:PANELBUS DVI RECEIVER 165MHZ PLUS HDCP |

| TFP503PZPG4 | 制造商:Texas Instruments 功能描述:DGTL RCVR 1RX 100HTQFP - Rail/Tube |

| TFP50N06 | 制造商:TAK_CHEONG 制造商全称:Tak Cheong Electronics (Holdings) Co.,Ltd 功能描述:N-Channel Power MOSFET 50A, 60V, 0.023Ω |

发布紧急采购,3分钟左右您将得到回复。