- 您现在的位置:买卖IC网 > PDF目录98215 > TFP501PZP (TEXAS INSTRUMENTS INC) SPECIALTY CONSUMER CIRCUIT, PQFP100 PDF资料下载

参数资料

| 型号: | TFP501PZP |

| 厂商: | TEXAS INSTRUMENTS INC |

| 元件分类: | 消费家电 |

| 英文描述: | SPECIALTY CONSUMER CIRCUIT, PQFP100 |

| 封装: | 14 X 14 MM, 1 MM HEIGHT, 0.50 MM PITCH, GREEN, PLASTIC, HTQFP-100 |

| 文件页数: | 6/24页 |

| 文件大小: | 373K |

| 代理商: | TFP501PZP |

TFP501

PanelBus HDCP DIGITAL RECEIVER

SLDS127B JULY 2001 REVISED AUGUST 2002

14

POST OFFICE BOX 655303

DALLAS, TEXAS 75265

TFP501 clocking and data synchronization (continued)

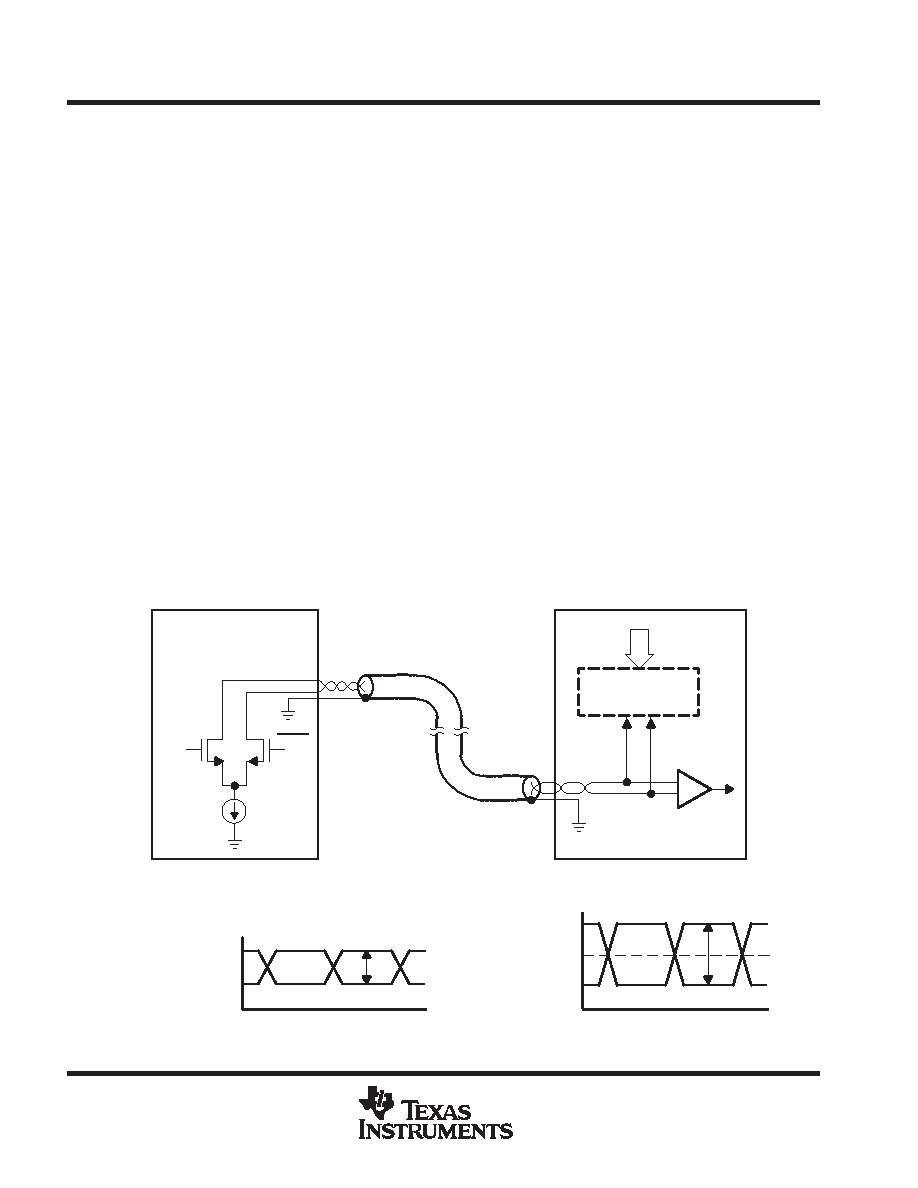

The input clock to the TFP501 is conditioned by a PLL (phase-locked-loop) to remove high frequency jitter from

the clock. The PLL provides four 10x clock outputs of different phases to locate and sync the T.M.D.S. data

streams (4x oversampling). During the active display interval, the pixel data is encoded to be transition

minimized; whereas, during the blanking interval, the control data is encoded to be transition maximized. A

DVI-compliant transmitter is required to transmit during the blanking interval for a minimum period of time,

128-t(pixel), to ensure sufficient time for data synchronization when the receiver sees a transition maximized

code. Performing synchronization during the blanking interval, when the data is transition maximized, assures

reliable data bit boundary detection. Phase synchronization to the data streams is unique for each of the three

input channels and is maintained as long as the link remains active.

TFP501 T.M.D.S. input levels and input impedance matching

The T.M.D.S. inputs to the TFP501 receiver have a fixed single-ended input termination impedance to AVDD.

The TFP501 is internally optimized using a laser trim process to precisely fix the single-ended termination

impedance at 50

. This fixed impedance eliminates the need for external termination resistors while providing

optimum impedance matching to standard DVI cables having a characteristic impedance of 100

.

Figure 14 shows a conceptual schematic of a TFP510 transmitter and TFP501 receiver connection. The

TFP510 transmitter drives the twisted-pair cable via a current source, usually achieved with an open-drain type

output driver. The internal single-ended termination resistors, which are matched to the characteristic

impedance of the DVI cable, provide a pullup to AVDD. Naturally, when the transmitter is disconnected and the

TFP501 DVI inputs are left unconnected, the TFP501 receiver inputs are pulled up to AVDD. The single-ended

differential signal and full differential signal is shown in Figure 15. The TFP501 is designed to respond to

differential signal swings ranging from 150 mV to 1.56 V with common mode voltages ranging from

(AVDD300 mV) to (AVDD37 mV).

_

+

Internal

Termination at 50

AVCC

DVI-Compliant Cable

DATA

TI TFP501 Receiver

TI TFP510 Transmitter

Current

Source

Figure 14. T.M.D.S. Differential Input and Transmitter Connection

1/2 VID

AVCC

AVCC - 1/2 VID

+ 1/2 VID

- 1/2 VID

VID

a ) Single-Ended Input Signal

b) Differential Input Signal

Figure 15. T.M.D.S. Inputs

相关PDF资料 |

PDF描述 |

|---|---|

| TFP503PZPG4 | SPECIALTY CONSUMER CIRCUIT, PQFP100 |

| TFP503PZP | SPECIALTY CONSUMER CIRCUIT, PQFP100 |

| TFP510PAPG4 | SPECIALTY CONSUMER CIRCUIT, PQFP64 |

| TFP510PAP | SPECIALTY CONSUMER CIRCUIT, PQFP64 |

| TFP513PAPG4 | SPECIALTY CONSUMER CIRCUIT, PQFP64 |

相关代理商/技术参数 |

参数描述 |

|---|---|

| TFP501PZPG4 | 制造商:Texas Instruments 功能描述:PNL BUS HDCP DGTL RCVR 100HTQFP - Rail/Tube |

| TFP503 | 制造商:TI 制造商全称:Texas Instruments 功能描述:PANELBUS HDCP DIGITAL RECEIVER |

| TFP503PZP | 制造商:Texas Instruments 功能描述:PANELBUS DVI RECEIVER 165MHZ PLUS HDCP |

| TFP503PZPG4 | 制造商:Texas Instruments 功能描述:DGTL RCVR 1RX 100HTQFP - Rail/Tube |

| TFP50N06 | 制造商:TAK_CHEONG 制造商全称:Tak Cheong Electronics (Holdings) Co.,Ltd 功能描述:N-Channel Power MOSFET 50A, 60V, 0.023Ω |

发布紧急采购,3分钟左右您将得到回复。