- 您现在的位置:买卖IC网 > PDF目录98252 > TLV320ADC3101IRGET320 (TEXAS INSTRUMENTS INC) SPECIALTY CONSUMER CIRCUIT, PQCC24 PDF资料下载

参数资料

| 型号: | TLV320ADC3101IRGET320 |

| 厂商: | TEXAS INSTRUMENTS INC |

| 元件分类: | 消费家电 |

| 英文描述: | SPECIALTY CONSUMER CIRCUIT, PQCC24 |

| 封装: | 4 X 4 MM, GREEN, PLASTIC, VQFN-24 |

| 文件页数: | 50/83页 |

| 文件大小: | 1338K |

| 代理商: | TLV320ADC3101IRGET320 |

第1页第2页第3页第4页第5页第6页第7页第8页第9页第10页第11页第12页第13页第14页第15页第16页第17页第18页第19页第20页第21页第22页第23页第24页第25页第26页第27页第28页第29页第30页第31页第32页第33页第34页第35页第36页第37页第38页第39页第40页第41页第42页第43页第44页第45页第46页第47页第48页第49页当前第50页第51页第52页第53页第54页第55页第56页第57页第58页第59页第60页第61页第62页第63页第64页第65页第66页第67页第68页第69页第70页第71页第72页第73页第74页第75页第76页第77页第78页第79页第80页第81页第82页第83页

SLAS553A – NOVEMBER 2008 – REVISED SEPTEMBER 2009...................................................................................................................................... www.ti.com

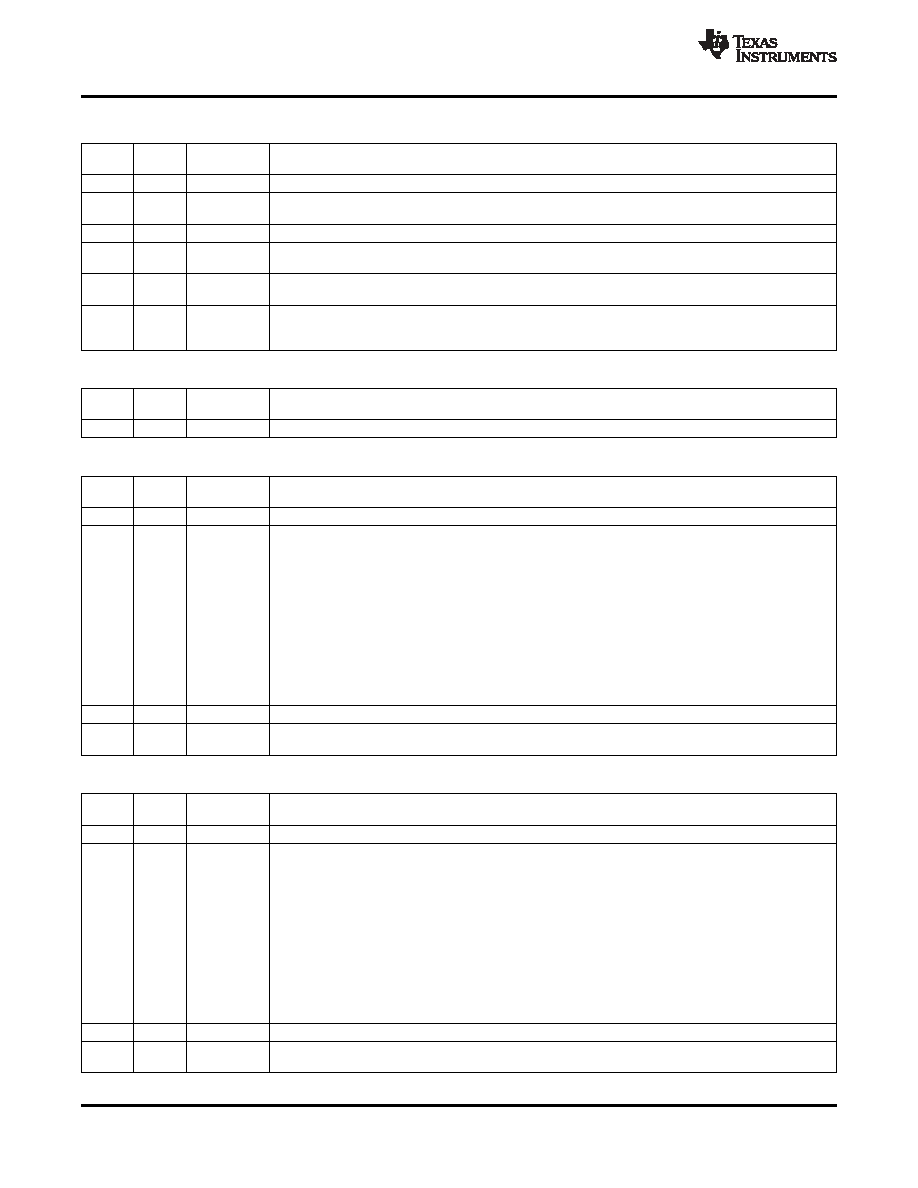

Page 0 / Register 49: INT2 Interrupt Control

BIT

READ/

RESET

DESCRIPTION

WRITE

VALUE

D7–D5

R

000

Reserved. Do not write any value other than reset value.

D4

R/W

0

0: ADC AGC noise interrupt is not used in the generation of INT2 interrupt.

1: ADC AGC noise interrupt is used in the generation of INT2 interrupt.

D3

R

0

Reserved. Do not write any value other than reset value.

D2

R/W

0

0: Engine-generated interrupts and overflow flags are not used in the generation of INT2 interrupt.

1: Engine-generated interrupts and overflow flags are used in the generation of INT2 interrupt.

D1

R/W

0

0: ADC data-available interrupt is not used in the generation of INT2 interrupt.

1: ADC data-available interrupt is used in the generation of INT2 interrupt.

D0

R/W

0

0: INT2 is only one pulse (active high) of duration typical 2 ms.

1: INT2 is multiple pulses (active high) of duration typical 2 ms and period 4 ms, until flag register 42 or

45 is read by the user.

Page 0 / Register 50: Reserved

BIT

READ/

RESET

DESCRIPTION

WRITE

VALUE

D7–D0

R

XXXX XXXX

Reserved. Do not write to this register.

Page 0 / Register 51: DMCLK/GPIO2 Control

BIT

READ/

RESET

DESCRIPTION

WRITE

VALUE

D7–D6

R

00

Reserved. Do not write any value other than reset value.

D5–D2

R/W

0000

0000: DMCLK disabled (input and output buffers powered down)

0001: DMCLK is in input mode (can be used as secondary BCLK input, secondary WCLK input,

Dig_Mic_In, or in ClockGen block)

0010: DMCLK is used as general-purpose input (GPI)

0011: DMCLK output = general-purpose output

0100: DMCLK output = CLKOUT output (source determined by cdiv_clkin_reg; page 0 / register 25)

0101: DMCLK output = INT1 output

0110: DMCLK output = INT2 output

0111: Reserved. Do not use.

1000: DMCLK output = secondary BCLK output for codec interface

1001: DMCLK output = secondary WCLK output for codec interface

1010: DMCLK output = ADC_MOD_CLK output for the digital microphone

1011–1111: Reserved. Do not use.

D1

R

0

DMCLK input buffer value

D0

R/W

0

0: DMCLK value = 0 when D5–D2 are programmed to "0011" (general-purpose output)

1: DMCLK value = 1 when D5–D2 are programmed to "0011" (general-purpose output)

Page 0 / Register 52: DMDIN/GPIO1 Control

BIT

READ/

RESET

DESCRIPTION

WRITE

VALUE

D7–D6

R

00

Reserved. Do not write any value other than reset value.

D5–D2

R/W

0000

0000: DMDIN disabled (input and output buffers powered down)

0001: DMDIN is in input mode (can be used as secondary BCLK input, secondary WCLK input,

Dig_Mic_In, or in ClockGen block)

0010: DMDIN is used as general-purpose input (GPI)

0011: DMDIN output = general-purpose output

0100: DMDIN output = CLKOUT output (source determined by cdiv_clkin_reg; page 0 / register 25)

0101: DMDIN output = INT1 output

0110: DMDIN output = INT2 output

0111: Reserved. Do not use.

1000: DMDIN output = secondary BCLK output for codec interface

1001: DMDIN output = secondary WCLK output for codec interface

1010: DMDIN output = ADC_MOD_CLK output for the digital microphone

1011–1111: Reserved. Do not use.

D1

R

0

DMDIN Input Buffer Value

D0

R/W

0

0: DMDIN value = 0 when D5–D2 are programmed to "0011" (general-purpose output)

1: DMDIN value = 1 when D5–D2 are programmed to "0011" (general-purpose output)

54

Copyright 2008–2009, Texas Instruments Incorporated

Product Folder Link(s) :TLV320ADC3101

相关PDF资料 |

PDF描述 |

|---|---|

| TLV320ADC3101IRGER | SPECIALTY CONSUMER CIRCUIT, PQCC24 |

| TLV320ADC3101IRGET | SPECIALTY CONSUMER CIRCUIT, PQCC24 |

| TLV320AIC10C | SPECIALTY CONSUMER CIRCUIT, PQFP48 |

| TLV320AIC10I | SPECIALTY CONSUMER CIRCUIT, PQFP48 |

| TLV320AIC10CPFB | SPECIALTY CONSUMER CIRCUIT, PQFP48 |

相关代理商/技术参数 |

参数描述 |

|---|---|

| TLV320AIC10 | 制造商:TI 制造商全称:Texas Instruments 功能描述:General-Purpose 3V to 5.5V 16-bit 22-KSPS DSP CODEC |

| TLV320AIC10C | 制造商:TI 制造商全称:Texas Instruments 功能描述:General-Purpose 3V to 5.5V 16-bit 22-KSPS DSP CODEC |

| TLV320AIC10CGQER | 功能描述:接口—CODEC 16-Bit 22-KSPS DSP Codec RoHS:否 制造商:Texas Instruments 类型: 分辨率: 转换速率:48 kSPs 接口类型:I2C ADC 数量:2 DAC 数量:4 工作电源电压:1.8 V, 2.1 V, 2.3 V to 5.5 V 最大工作温度:+ 85 C 安装风格:SMD/SMT 封装 / 箱体:DSBGA-81 封装:Reel |

| TLV320AIC10CPFB | 功能描述:接口—CODEC 16-Bit 22-KSPS DSP Codec RoHS:否 制造商:Texas Instruments 类型: 分辨率: 转换速率:48 kSPs 接口类型:I2C ADC 数量:2 DAC 数量:4 工作电源电压:1.8 V, 2.1 V, 2.3 V to 5.5 V 最大工作温度:+ 85 C 安装风格:SMD/SMT 封装 / 箱体:DSBGA-81 封装:Reel |

| TLV320AIC10CPFBG4 | 功能描述:接口—CODEC 16-Bit Reg Trnscvr With 3-State Outputs RoHS:否 制造商:Texas Instruments 类型: 分辨率: 转换速率:48 kSPs 接口类型:I2C ADC 数量:2 DAC 数量:4 工作电源电压:1.8 V, 2.1 V, 2.3 V to 5.5 V 最大工作温度:+ 85 C 安装风格:SMD/SMT 封装 / 箱体:DSBGA-81 封装:Reel |

发布紧急采购,3分钟左右您将得到回复。