- 您现在的位置:买卖IC网 > PDF目录300038 > TMS470R1B768PGEQR (TEXAS INSTRUMENTS INC) 32-BIT, FLASH, 60 MHz, RISC MICROCONTROLLER, PQFP144 PDF资料下载

参数资料

| 型号: | TMS470R1B768PGEQR |

| 厂商: | TEXAS INSTRUMENTS INC |

| 元件分类: | 微控制器/微处理器 |

| 英文描述: | 32-BIT, FLASH, 60 MHz, RISC MICROCONTROLLER, PQFP144 |

| 封装: | PLASTIC, LQFP-144 |

| 文件页数: | 6/49页 |

| 文件大小: | 552K |

| 代理商: | TMS470R1B768PGEQR |

第1页第2页第3页第4页第5页当前第6页第7页第8页第9页第10页第11页第12页第13页第14页第15页第16页第17页第18页第19页第20页第21页第22页第23页第24页第25页第26页第27页第28页第29页第30页第31页第32页第33页第34页第35页第36页第37页第38页第39页第40页第41页第42页第43页第44页第45页第46页第47页第48页第49页

SPNS108B – AUGUST 2005 – REVISED MAY 2008 ......................................................................................................................................................... www.ti.com

Flash Pipeline Mode

When in pipeline mode, the flash operates with a system clock frequency of up to 60 MHz (versus a system

clock in normal mode of up to 30 MHz). Flash in pipeline mode is capable of accessing 64-bit words and

provides two 32-bit pipelined words to the CPU. Also in pipeline mode, the flash can be read with no wait states

when memory addresses are contiguous (after the initial 1-or 2-wait-state reads).

NOTE:

After a system reset, pipeline mode is disabled (ENPIPE bit [FMREGOPT.0] is a 0). In

other words, the B768 device powers up and comes out of reset in non-pipeline

mode. Furthermore, setting the flash configuration mode bit (GBLCTRL.4) will override

pipeline mode.

Flash Program and Erase

The B768 device flash contains three 256K-byte memory arrays (or banks) for a total of 768K bytes of flash and

consists of 18 sectors. These 18 sectors are sized as follows:

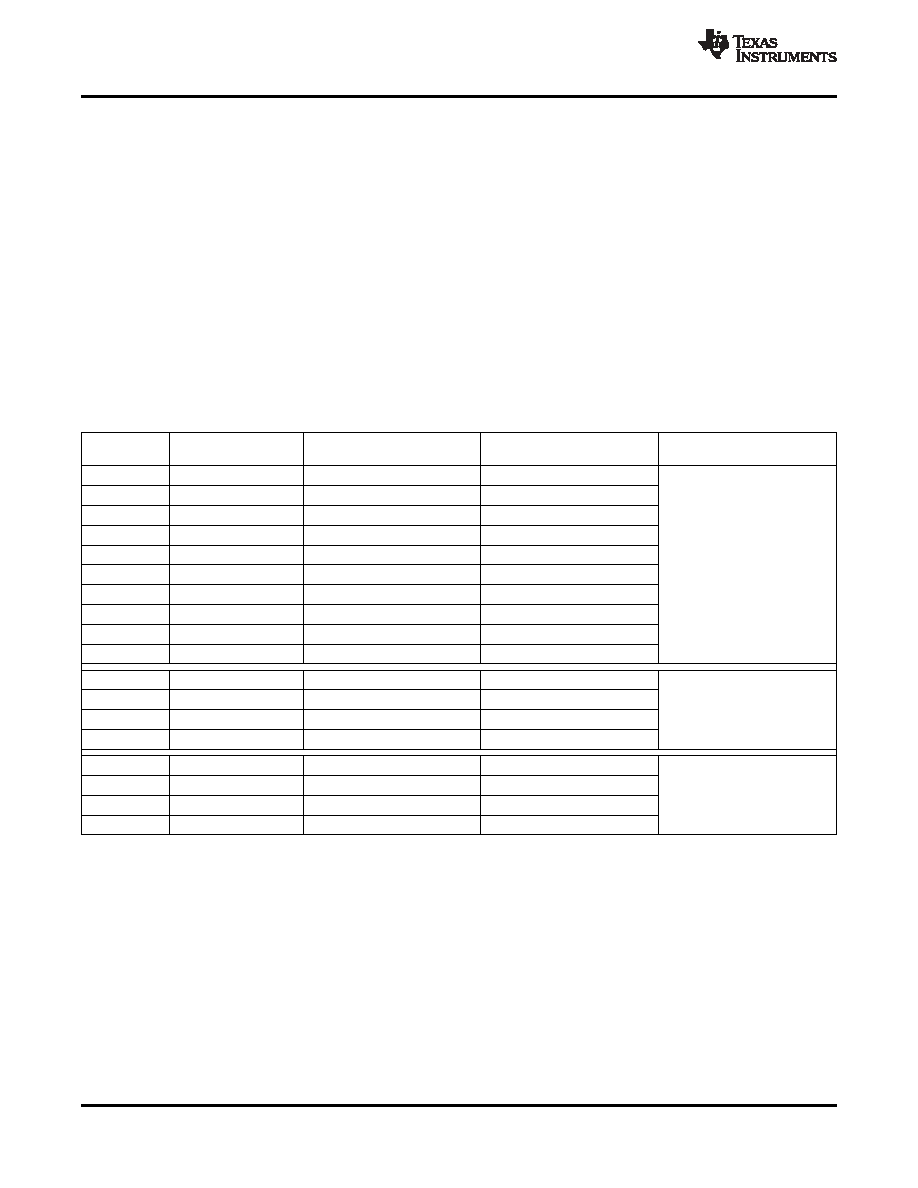

Table 4. B768 Flash Memory Banks and Sectors

MEMORY ARRAYS

SECTOR NO.

SEGMENT

LOW ADDRESS

HIGH ADDRESS

(OR BANKS)

0

16K Bytes

0x0000_0000

0x0000_3FFF

1

16K Bytes

0x0000_4000

0x0000_7FFF

2

32K Bytes

0x0000_8000

0x0000_FFFF

3

32K Bytes

0x0001_0000

0x0001_7FFF

4

32K Bytes

0x0001_8000

0x0001_FFFF

BANK0

(256K Bytes)

5

32K Bytes

0x0002_0000

0x0002_7FFF

6

32K Bytes

0x0002_8000

0x0002_FFFF

7

32K Bytes

0x0003_0000

0x0003_7FFF

8

16K Bytes

0x0003_8000

0x0003_BFFF

9

16K Bytes

0x0003_C000

0x0003_FFFF

0

64K Bytes

0x0004_0000

0x0004_FFFF

1

64K Bytes

0x0005_0000

0x0005_FFFF

BANK1

(256K Bytes)

2

64K Bytes

0x0006_0000

0x0006_FFFF

3

64K Bytes

0x0007_0000

0x0007_FFFF

0

64K Bytes

0x0008_0000

0x0008_FFFF

1

64K Bytes

0x0009_0000

0x0009_FFFF

BANK2

(256K Bytes)

2

64K Bytes

0x000A_0000

0x000A_FFFF

3

64K Bytes

0x000B_0000

0x000B_FFFF

The minimum size for an erase operation is one sector. The maximum size for a program operation is one 16-bit

word. For more detailed information on flash program and erase operations, see the TMS470R1x Flash

Reference Guide (literature number SPNU194).

NOTE:

The flash external pump voltage (VCCP ) is required for all operations (program, erase,

and read).

HET RAM

The B768 device contains HET RAM. The HET RAM has a 128-instruction capability. The HET RAM is

configurable by the SYS module to be addressed within the range of 0x0000_0000 to 0xFFE0_0000. The HET

RAM is addressed through memory select 4.

14

Copyright 2005–2008, Texas Instruments Incorporated

Product Folder Link(s): TMS470R1B768

相关PDF资料 |

PDF描述 |

|---|---|

| TMS4C1050-4DJL | 256K X 4 OTHER FIFO, PDSO20 |

| TMS4C1050-3NL | 256K X 4 OTHER FIFO, PDIP16 |

| TMS570LS10216ASZWTQR | 32-BIT, FLASH, 160 MHz, RISC MICROCONTROLLER, PBGA337 |

| TMX320DM642GNZ500 | 64-BIT, 75.19 MHz, OTHER DSP, PBGA548 |

| TN4002PM | 10 MHz - 500 MHz RF/MICROWAVE WIDE BAND LOW POWER AMPLIFIER |

相关代理商/技术参数 |

参数描述 |

|---|---|

| TMS470R1B768PGET | 功能描述:ARM微控制器 - MCU 60mhz / 768k Flash RoHS:否 制造商:STMicroelectronics 核心:ARM Cortex M4F 处理器系列:STM32F373xx 数据总线宽度:32 bit 最大时钟频率:72 MHz 程序存储器大小:256 KB 数据 RAM 大小:32 KB 片上 ADC:Yes 工作电源电压:1.65 V to 3.6 V, 2 V to 3.6 V, 2.2 V to 3.6 V 工作温度范围:- 40 C to + 85 C 封装 / 箱体:LQFP-48 安装风格:SMD/SMT |

| TMS470R1F316PZQ | 制造商:Texas Instruments 功能描述: |

| TMS470R1F354PNQ | 制造商:Texas Instruments 功能描述: |

| TMS470R1F366APZQ | 制造商:Texas Instruments 功能描述: |

| TMS470R1F369APGEQ | 制造商:Texas Instruments 功能描述: |

发布紧急采购,3分钟左右您将得到回复。