- 您现在的位置:买卖IC网 > PDF目录365968 > TSB14C01HV (Texas Instruments, Inc.) 5-V IEEE 1394-1995 BACKPLANE TRANSCEIVER/ARBITER PDF资料下载

参数资料

| 型号: | TSB14C01HV |

| 厂商: | Texas Instruments, Inc. |

| 英文描述: | 5-V IEEE 1394-1995 BACKPLANE TRANSCEIVER/ARBITER |

| 中文描述: | 5V的电机及电子学工程师联合会1394-1995背板收发器/仲裁者 |

| 文件页数: | 24/35页 |

| 文件大小: | 224K |

| 代理商: | TSB14C01HV |

第1页第2页第3页第4页第5页第6页第7页第8页第9页第10页第11页第12页第13页第14页第15页第16页第17页第18页第19页第20页第21页第22页第23页当前第24页第25页第26页第27页第28页第29页第30页第31页第32页第33页第34页第35页

6

–

4

LReq0

LReq1

LReq2

LReqN

LReq3

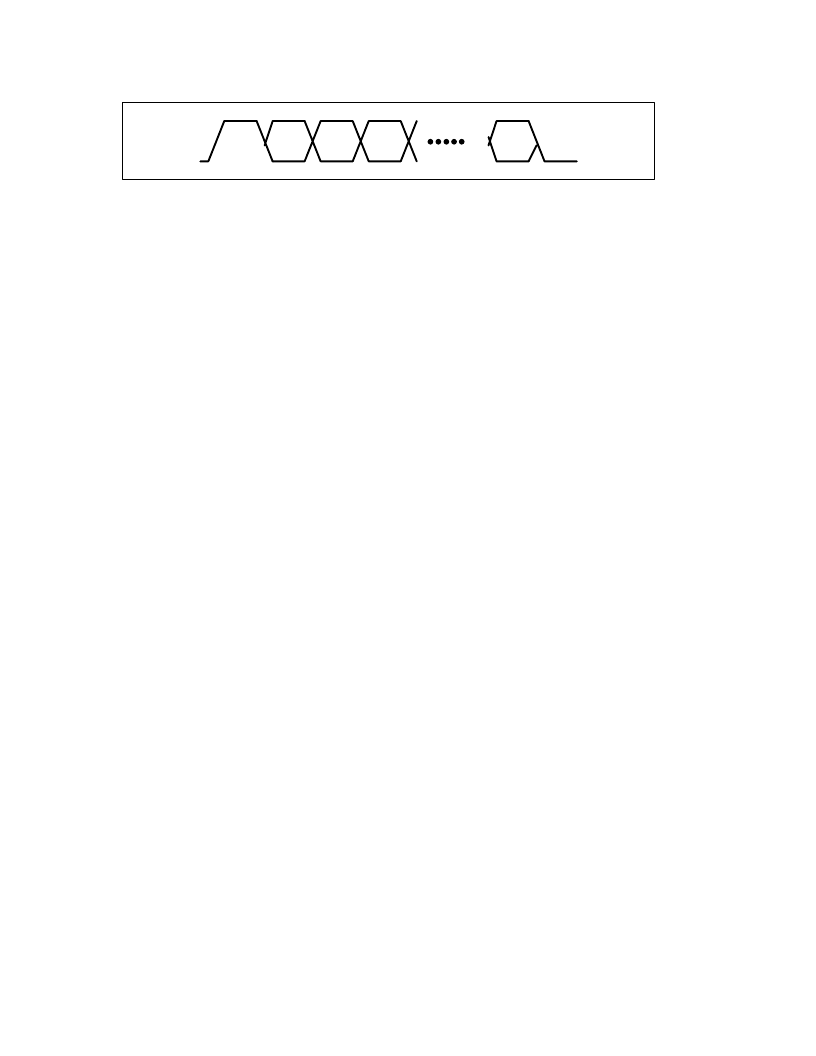

Figure 6

–

2. LREQ Timing

6.1.1

Bus Request

For fair or priority access, the link requests control of the bus at least one clock cycle after the PHY

–

link interface

becomes idle. When the link senses that the CTL terminals are in a receive state (CTL0 and CTL1 = 10), then it knows

that its request has been lost. This is true anytime during or after a bus request transfer by the link. Additionally, the

PHY ignores any fair requests if it asserts the receive state while the link is requesting the bus. When the link finds

the CTL terminals in a receive state, the link reissues the bus request transfer one clock cycle after the next interface

idle.

To send an acknowledge, the link must issue an ImmReq request during the reception of the packet addressed to

it. This is required because the delay from end-of-packet to acknowledge requests adds directly to the minimum delay

every PHY must wait after every packet to allow an acknowledge to occur. After the packet ends, the PHY immediately

takes control of the bus and grants the bus to the link. If the header cyclic redundancy check (CRC) of the packet turns

out to be bad, the link releases the bus immediately. The link cannot use this grant to send another type of packet.

To ensure this, the link must wait 160 ns after the end of the received packet to allow the PHY to grant it the bus for

the acknowledgement, and then the link releases the bus and proceeds with another request.

Although improbable, it is conceivable that two separate nodes can believe that an incoming packet is intended for

them. The nodes then issue an ImmReq request before checking the CRC of the packet. Since both PHYs seize

control of the bus at the same time, a temporary, localized collision of the bus occurs. As soon as the two nodes check

the CRC, the mistaken node drops its request and the false line is removed. The only side effect is the loss of the

intended acknowledgement packet (this is handled by the higher-layer protocol).

Once the link issues an immediate, fair, or urgent request for access to the bus it cannot issue another request until

the PHY indicates a lost (incoming packet) or won (transmit) signal. The PHY ignores new requests while a previous

request is pending.

6.1.2

Read/Write Requests

For read requests (see Table 6

–

6), the PHY returns the contents of the addressed register at the next opportunity

through a status transfer. For write requests, the PHY takes the value in the data field (see Table 6

–

7) of the transfer

and loads it into the addressed register as soon as the transfer is complete. When the status transfer is interrupted

by an incoming packet, the PHY continues to attempt the transfer of the requested register until it is successful.

6.1.3

Status

When the PHY has status information to transfer to the link, it initiates a status transfer. The PHY waits until the

interface is idle to perform the transfer. The PHY initiates the transfer by asserting status (01) on the CTL terminals,

along with the first two bits of status information on D0 and D1. The PHY maintains CTL status for the duration of the

status transfer. The PHY can temporarily halt a status transfer by asserting something other than status on the CTL

terminals. This is done in the event that a packet arrives before the status transfer completes. There must be at least

one idle cycle between consecutive status transfers.

The PHY normally sends only the first 4 bits of status to the link. These bits are status flags that are needed by link

state machines. The PHY sends an entire status packet to the link after a request transfer that contains a read request.

The definition of the bits in the status transfer are shown in Table 6

–

9 (also see Table 3

–

1 and Table 6

–

6). Status

transfer timing is shown in Figure 6

–

3.

相关PDF资料 |

PDF描述 |

|---|---|

| TSB21LV03MHV | IC APEX 20KE FPGA 200K 484-FBGA |

| TSB21LV03CHV | IEEE 1394-1995 TRIPLE-CABLE TRANSCEIVER/ARBITER |

| TSB2203X6MMX30M | IC APEX 20KE FPGA 200K 240-PQFP |

| TSB2204.5X12MMX20M | IC APEX 20KE FPGA 200K 240-PQFP |

| TSB2204.5X19MMX20M | IC APEX 20KE FPGA 200K 240-PQFP |

相关代理商/技术参数 |

参数描述 |

|---|---|

| TSB14C01MHV | 制造商:未知厂家 制造商全称:未知厂家 功能描述:Transceiver |

| TSB14C01PM | 制造商:Rochester Electronics LLC 功能描述:- Bulk |

| TSB15 | 制造商:未知厂家 制造商全称:未知厂家 功能描述:EURO TERMINAL BLOCKS |

| TSB150002DS | 制造商:TE Connectivity 功能描述: |

| TSB150004DS | 制造商:TE Connectivity 功能描述:Conn Europa Terminal Blocks 8 POS 13.5mm Screw ST Cable Mount 40A/Contact |

发布紧急采购,3分钟左右您将得到回复。