- 您现在的位置:买卖IC网 > PDF目录3972 > UPD44646183AF5-E22-FQ1 (Renesas Electronics America)SRAM DDRII 72MBIT 165-PBGA PDF资料下载

参数资料

| 型号: | UPD44646183AF5-E22-FQ1 |

| 厂商: | Renesas Electronics America |

| 文件页数: | 13/42页 |

| 文件大小: | 0K |

| 描述: | SRAM DDRII 72MBIT 165-PBGA |

| 标准包装: | 1 |

| 格式 - 存储器: | RAM |

| 存储器类型: | SRAM - 同步,DDR II+ |

| 存储容量: | 72M(4M x 18) |

| 速度: | 450MHz |

| 接口: | 并联 |

| 电源电压: | 1.7 V ~ 1.9 V |

| 工作温度: | 0°C ~ 70°C |

| 封装/外壳: | 165-LBGA |

| 供应商设备封装: | 165-PBGA(13x15) |

| 包装: | 散装 |

第1页第2页第3页第4页第5页第6页第7页第8页第9页第10页第11页第12页当前第13页第14页第15页第16页第17页第18页第19页第20页第21页第22页第23页第24页第25页第26页第27页第28页第29页第30页第31页第32页第33页第34页第35页第36页第37页第38页第39页第40页第41页第42页

�� �

�

�

�μ� PD44646092A-A,� 44646182A-A,� 44646362A-A,� 44646093A-A,� 44646183A-A,� 44646363A-A�

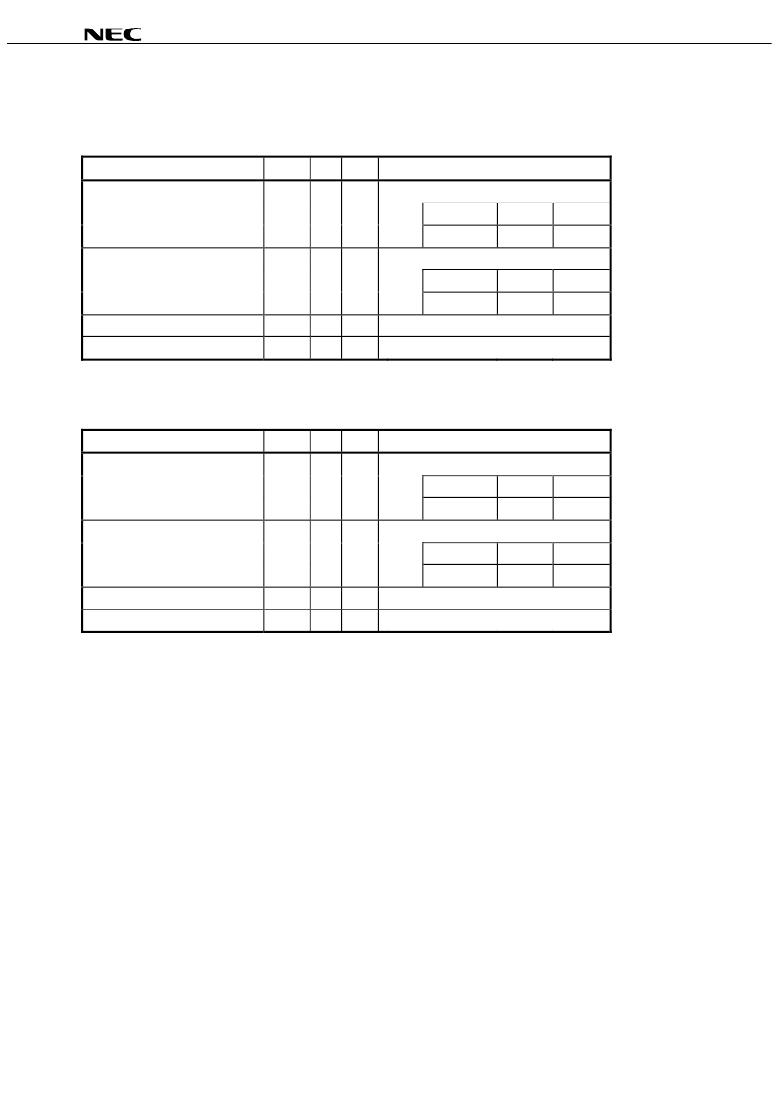

�Truth� Table�

�2.0� Clock� Cycles� Read� Latency�

�[� μ� PD44646092A-A],� [� μ� PD44646182A-A],� [� μ� PD44646362A-A]�

�Operation�

�WRITE� cycle�

�Load� address,� input� write� data� on�

�consecutive� K� and� K#� rising� edge�

�READ� cycle�

�Load� address,� read� data� on�

�consecutive� K� and� K#� rising� edge�

�NOP� (No� operation)�

�Clock� stop�

�CLK�

�L� →� H�

�L� →� H�

�L� →� H�

�Stopped�

�LD#�

�L�

�L�

�H�

�X�

�R,W#�

�L�

�H�

�X�

�X�

�DQ�

�Data� in�

�Input� data�

�Input� clock�

�Data� out�

�Output� data�

�Output� clock�

�DQ� =� High-Z�

�Previous� state�

�D� A� (A+0)�

�K(t+1)� ↑�

�Q� A� (A+0)�

�K(t+2)� ↑�

�D� A� (A+1)�

�K#(t+1)� ↑�

�Q� A� (A+1)�

�K#(t+2)� ↑�

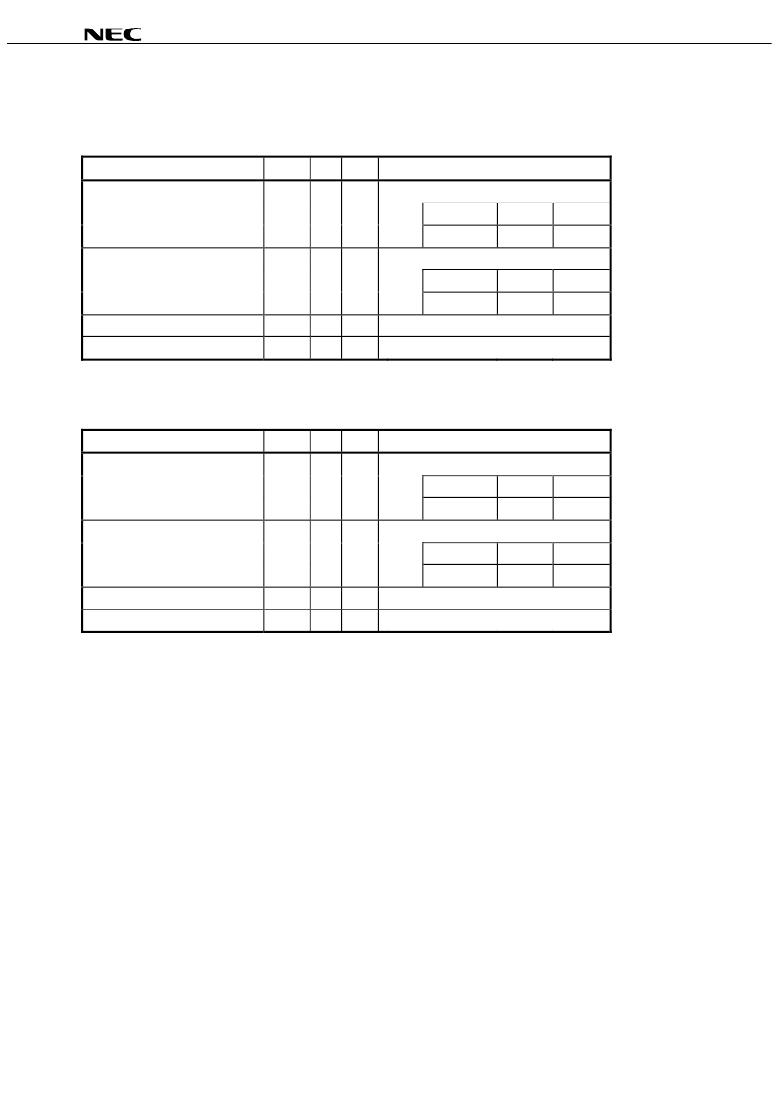

�2.5� Clock� Cycles� Read� Latency�

�[� μ� PD44646093A-A],� [� μ� PD44646183A-A],� [� μ� PD44646363A-A]�

�Operation�

�WRITE� cycle�

�Load� address,� input� write� data� on�

�consecutive� K� and� K#� rising� edge�

�READ� cycle�

�Load� address,� read� data� on�

�consecutive� K� and� K#� rising� edge�

�NOP� (No� operation)�

�Clock� stop�

�CLK�

�L� →� H�

�L� →� H�

�L� →� H�

�Stopped�

�LD#�

�L�

�L�

�H�

�X�

�R,W#�

�L�

�H�

�X�

�X�

�DQ�

�Data� in�

�Input� data�

�Input� clock�

�Data� out�

�Output� data�

�Output� clock�

�DQ� =� High-Z�

�Previous� state�

�D� A� (A+0)�

�K(t+1)� ↑�

�Q� A� (A+0)�

�K#(t+2)� ↑�

�D� A� (A+1)�

�K#(t+1)� ↑�

�Q� A� (A+1)�

�K(t+3)� ↑�

�Remarks�

�Remarks� listed� below� are� for� both� products� with� 2.0� and� 2.5� Clock� Cycles� Read� Latency.�

�1.� H� :� HIGH,� L� :� LOW,� ×� :� don’t� care,� ↑� :� rising� edge.�

�2.� Data� inputs� are� registered� at� K� and� K#� rising� edges.� Data� outputs� are� delivered� at� K� and� K#� rising� edges.�

�3.� All� control� inputs� in� the� truth� table� must� meet� setup/hold� times� around� the� rising� edge� (LOW� to� HIGH)� of�

�K.� All� control� inputs� are� registered� during� the� rising� edge� of� K.�

�4.� This� device� contains� circuitry� that� ensure� the� outputs� to� be� in� high� impedance� during� power-up.�

�5.� Refer� to� state� diagram� and� timing� diagrams� for� clarification.�

�6.� A+0� refers� to� the� address� input� during� a� WRITE� or� READ� cycle.�

�A+1� refers� to� the� next� internal� burst� address� in� accordance� with� the� burst� sequence.�

�7.� It� is� recommended� that� K� =� K#� when� clock� is� stopped.� This� is� not� essential� but� permits� most� rapid� restart�

�by� overcoming� transmission� line� charging� symmetrically.�

�Data� Sheet� M19960EJ2V0DS�

�11�

�相关PDF资料 |

PDF描述 |

|---|---|

| IDT70T3589S133BC | IC SRAM 2MBIT 133MHZ 256BGA |

| RMC60DTEH | CONN EDGECARD 120PS .100 EYELET |

| IDT70T3399S133BC | IC SRAM 2MBIT 133MHZ 256BGA |

| FMM43DREF | CONN EDGECARD 86POS .156 EYELET |

| IDT70V657S10DRG | IC SRAM 1.125MBIT 10NS 208PQFP |

相关代理商/技术参数 |

参数描述 |

|---|---|

| UPD44646183AF5-E22-FQ1-A | 功能描述:SRAM DDRII 72MBIT 165-PBGA RoHS:是 类别:集成电路 (IC) >> 存储器 系列:- 标准包装:3,000 系列:- 格式 - 存储器:EEPROMs - 串行 存储器类型:EEPROM 存储容量:8K (1K x 8) 速度:400kHz 接口:I²C,2 线串口 电源电压:1.7 V ~ 5.5 V 工作温度:-40°C ~ 85°C 封装/外壳:8-SOIC(0.154",3.90mm 宽) 供应商设备封装:8-SOIC 包装:带卷 (TR) |

| UPD44646183AF5-E25-FQ1 | 功能描述:SRAM DDRII 72MBIT 165-PBGA RoHS:是 类别:集成电路 (IC) >> 存储器 系列:- 标准包装:3,000 系列:- 格式 - 存储器:EEPROMs - 串行 存储器类型:EEPROM 存储容量:8K (1K x 8) 速度:400kHz 接口:I²C,2 线串口 电源电压:1.7 V ~ 5.5 V 工作温度:-40°C ~ 85°C 封装/外壳:8-SOIC(0.154",3.90mm 宽) 供应商设备封装:8-SOIC 包装:带卷 (TR) |

| UPD44646183AF5-E25-FQ1-A | 功能描述:SRAM DDRII 72MBIT 165-PBGA RoHS:是 类别:集成电路 (IC) >> 存储器 系列:- 标准包装:3,000 系列:- 格式 - 存储器:EEPROMs - 串行 存储器类型:EEPROM 存储容量:8K (1K x 8) 速度:400kHz 接口:I²C,2 线串口 电源电压:1.7 V ~ 5.5 V 工作温度:-40°C ~ 85°C 封装/外壳:8-SOIC(0.154",3.90mm 宽) 供应商设备封装:8-SOIC 包装:带卷 (TR) |

| UPD44646363AF5-E22-FQ1 | 功能描述:SRAM DDRII 72MBIT 165-PBGA RoHS:是 类别:集成电路 (IC) >> 存储器 系列:- 标准包装:3,000 系列:- 格式 - 存储器:EEPROMs - 串行 存储器类型:EEPROM 存储容量:8K (1K x 8) 速度:400kHz 接口:I²C,2 线串口 电源电压:1.7 V ~ 5.5 V 工作温度:-40°C ~ 85°C 封装/外壳:8-SOIC(0.154",3.90mm 宽) 供应商设备封装:8-SOIC 包装:带卷 (TR) |

| UPD44646363AF5-E22-FQ1-A | 功能描述:SRAM DDRII 72MBIT 165-PBGA RoHS:是 类别:集成电路 (IC) >> 存储器 系列:- 标准包装:3,000 系列:- 格式 - 存储器:EEPROMs - 串行 存储器类型:EEPROM 存储容量:8K (1K x 8) 速度:400kHz 接口:I²C,2 线串口 电源电压:1.7 V ~ 5.5 V 工作温度:-40°C ~ 85°C 封装/外壳:8-SOIC(0.154",3.90mm 宽) 供应商设备封装:8-SOIC 包装:带卷 (TR) |

发布紧急采购,3分钟左右您将得到回复。