- 您现在的位置:买卖IC网 > PDF目录361590 > UPSD3213B-24U1T (意法半导体) Flash Programmable System Devices with 8032 Microcontroller Core and 64Kbit SRAM PDF资料下载

参数资料

| 型号: | UPSD3213B-24U1T |

| 厂商: | 意法半导体 |

| 英文描述: | Flash Programmable System Devices with 8032 Microcontroller Core and 64Kbit SRAM |

| 中文描述: | 闪存可编程系统设备与8032微控制器核心和64Kbit SRAM的 |

| 文件页数: | 43/176页 |

| 文件大小: | 1081K |

| 代理商: | UPSD3213B-24U1T |

第1页第2页第3页第4页第5页第6页第7页第8页第9页第10页第11页第12页第13页第14页第15页第16页第17页第18页第19页第20页第21页第22页第23页第24页第25页第26页第27页第28页第29页第30页第31页第32页第33页第34页第35页第36页第37页第38页第39页第40页第41页第42页当前第43页第44页第45页第46页第47页第48页第49页第50页第51页第52页第53页第54页第55页第56页第57页第58页第59页第60页第61页第62页第63页第64页第65页第66页第67页第68页第69页第70页第71页第72页第73页第74页第75页第76页第77页第78页第79页第80页第81页第82页第83页第84页第85页第86页第87页第88页第89页第90页第91页第92页第93页第94页第95页第96页第97页第98页第99页第100页第101页第102页第103页第104页第105页第106页第107页第108页第109页第110页第111页第112页第113页第114页第115页第116页第117页第118页第119页第120页第121页第122页第123页第124页第125页第126页第127页第128页第129页第130页第131页第132页第133页第134页第135页第136页第137页第138页第139页第140页第141页第142页第143页第144页第145页第146页第147页第148页第149页第150页第151页第152页第153页第154页第155页第156页第157页第158页第159页第160页第161页第162页第163页第164页第165页第166页第167页第168页第169页第170页第171页第172页第173页第174页第175页第176页

43/176

μ

PSD323X

How Interruptsare Handled

The interrupt flags are sampled at S5P2 of every

machine cycle. The samples are polled during fol-

lowing machine cycle. If one of the flags was in a

set condition at S5P2 of the preceding cycle, the

polling cycle will find it and the interrupt system will

generate anLCALL to the appropriate service rou-

tine, provided this H/W generated LCALL is not

blocked by any of the following conditions:

I

An interrupt of equal priority or higher priority

level is already in progress.

I

The current machine cycle is not the final cycle

in the execution of the instruction in progress.

I

The instruction in progress is RETI or any

access to the interrupt priority or interrupt

enable registers.

The polling cycle is repeated with each machine

cycle, and the values polled are the values that

were present at S5P2 of the previous machine cy-

cle.

Note:

If an interrupt flag is active but being re-

sponded to for one of the above mentioned condi-

tions, if the flag is still inactive when the blocking

condition is removed, the denied interrupt will not

be serviced. In other words, the fact that the inter-

rupt flag was once active but not servicedis notre-

membered. Every polling cycle is new.

The processor acknowledges an interrupt request

by executing a hardware generated LCALL to the

appropriate service routine. The hardware gener-

ated LCALL pushes the contents of the Program

Counter on to the stack (but it does not save the

PSW) and reloads the PCwith anaddress that de-

pends on the source of the interrupt being vec-

tored to as shown in Table 24.

Execution proceeds from that location until the

RETI instructionis encountered.The RETIinstruc-

tion informsthe processor that the interrupt routine

is no longer in progress, then pops the top two

bytes from the stack and reloads the Program

Counter. Execution of the interrupted program

continues from where it left off.

Note:

A simple RET instruction would also return

execution to the interrupted program, but it would

have left the interrupt control system thinking an

interrupt was still in progress, making future inter-

rupts impossible.

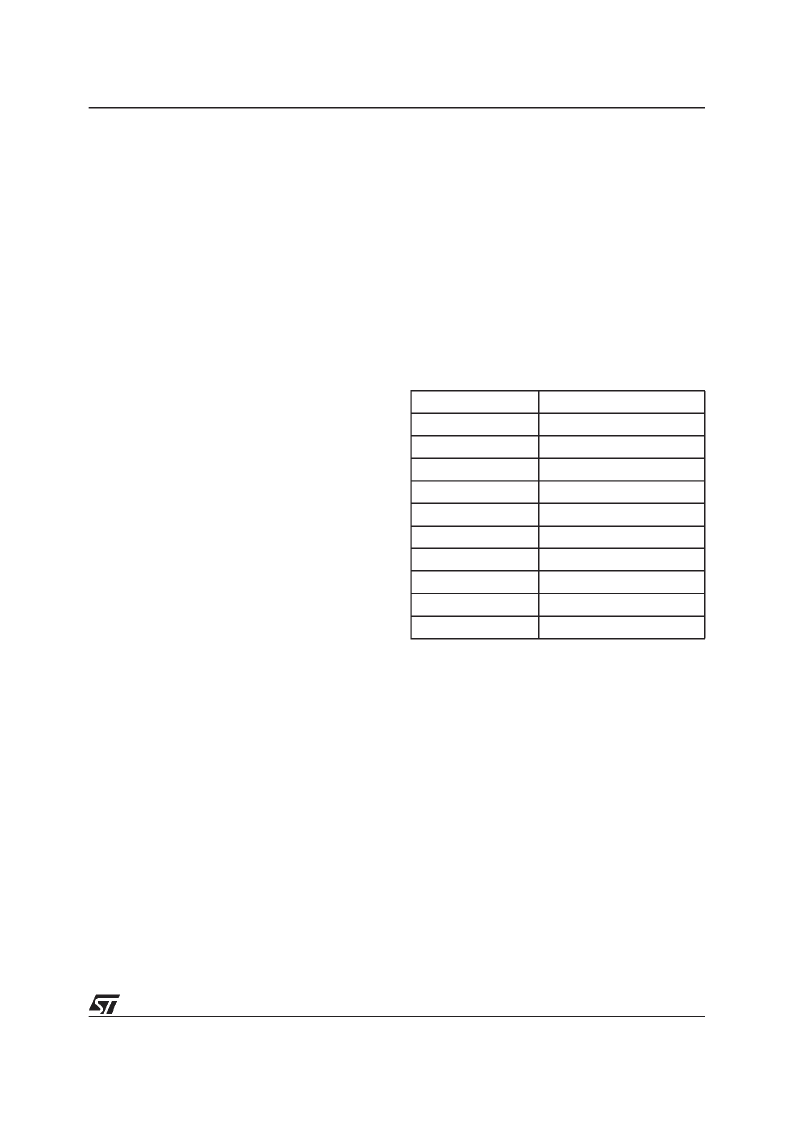

Table 24. Vector Addresses

Source

Vector Address

Int0

0003h

2nd USART

004Bh

Timer0

000Bh

I C

0043h

Int1

0013h

DDC

003Bh

Timer1

001Bh

USB

0033h

1st USART

0023h

Timer2+EXF2

002Bh

相关PDF资料 |

PDF描述 |

|---|---|

| UPSD3213B-40T1T | Flash Programmable System Devices with 8032 Microcontroller Core and 64Kbit SRAM |

| UPSD3213B-40T6T | Flash Programmable System Devices with 8032 Microcontroller Core and 64Kbit SRAM |

| UPSD3213B-40U1T | Flash Programmable System Devices with 8032 Microcontroller Core and 64Kbit SRAM |

| UPSD3213BV-40U6T | Flash Programmable System Devices with 8032 Microcontroller Core and 64Kbit SRAM |

| UPSD3214A-40U1T | Flash Programmable System Devices with 8032 Microcontroller Core and 64Kbit SRAM |

相关代理商/技术参数 |

参数描述 |

|---|---|

| UPSD3213B-24U6 | 制造商:STMICROELECTRONICS 制造商全称:STMicroelectronics 功能描述:Flash Programmable System Device with 8032 Microcontroller Core |

| UPSD3213B-24U6T | 制造商:STMICROELECTRONICS 制造商全称:STMicroelectronics 功能描述:Flash Programmable System Devices with 8032 Microcontroller Core and 64Kbit SRAM |

| UPSD3213B-40T1 | 制造商:STMICROELECTRONICS 制造商全称:STMicroelectronics 功能描述:Flash Programmable System Device with 8032 Microcontroller Core |

| UPSD3213B-40T1T | 制造商:STMICROELECTRONICS 制造商全称:STMicroelectronics 功能描述:Flash Programmable System Devices with 8032 Microcontroller Core and 64Kbit SRAM |

| UPSD3213B-40T6 | 制造商:STMICROELECTRONICS 制造商全称:STMicroelectronics 功能描述:Flash Programmable System Device with 8032 Microcontroller Core |

发布紧急采购,3分钟左右您将得到回复。