- 您现在的位置:买卖IC网 > PDF目录140426 > W25Q16CVZPAG (WINBOND ELECTRONICS CORP) 16M X 1 SPI BUS SERIAL EEPROM, PDSO8 PDF资料下载

参数资料

| 型号: | W25Q16CVZPAG |

| 厂商: | WINBOND ELECTRONICS CORP |

| 元件分类: | PROM |

| 英文描述: | 16M X 1 SPI BUS SERIAL EEPROM, PDSO8 |

| 封装: | 6 X 5 MM, GREEN, WSON-8 |

| 文件页数: | 18/79页 |

| 文件大小: | 1131K |

| 代理商: | W25Q16CVZPAG |

第1页第2页第3页第4页第5页第6页第7页第8页第9页第10页第11页第12页第13页第14页第15页第16页第17页当前第18页第19页第20页第21页第22页第23页第24页第25页第26页第27页第28页第29页第30页第31页第32页第33页第34页第35页第36页第37页第38页第39页第40页第41页第42页第43页第44页第45页第46页第47页第48页第49页第50页第51页第52页第53页第54页第55页第56页第57页第58页第59页第60页第61页第62页第63页第64页第65页第66页第67页第68页第69页第70页第71页第72页第73页第74页第75页第76页第77页第78页第79页

W25Q16CV

Publication Release Date: April 01, 2011

- 25 -

Revision C

(IO

1)

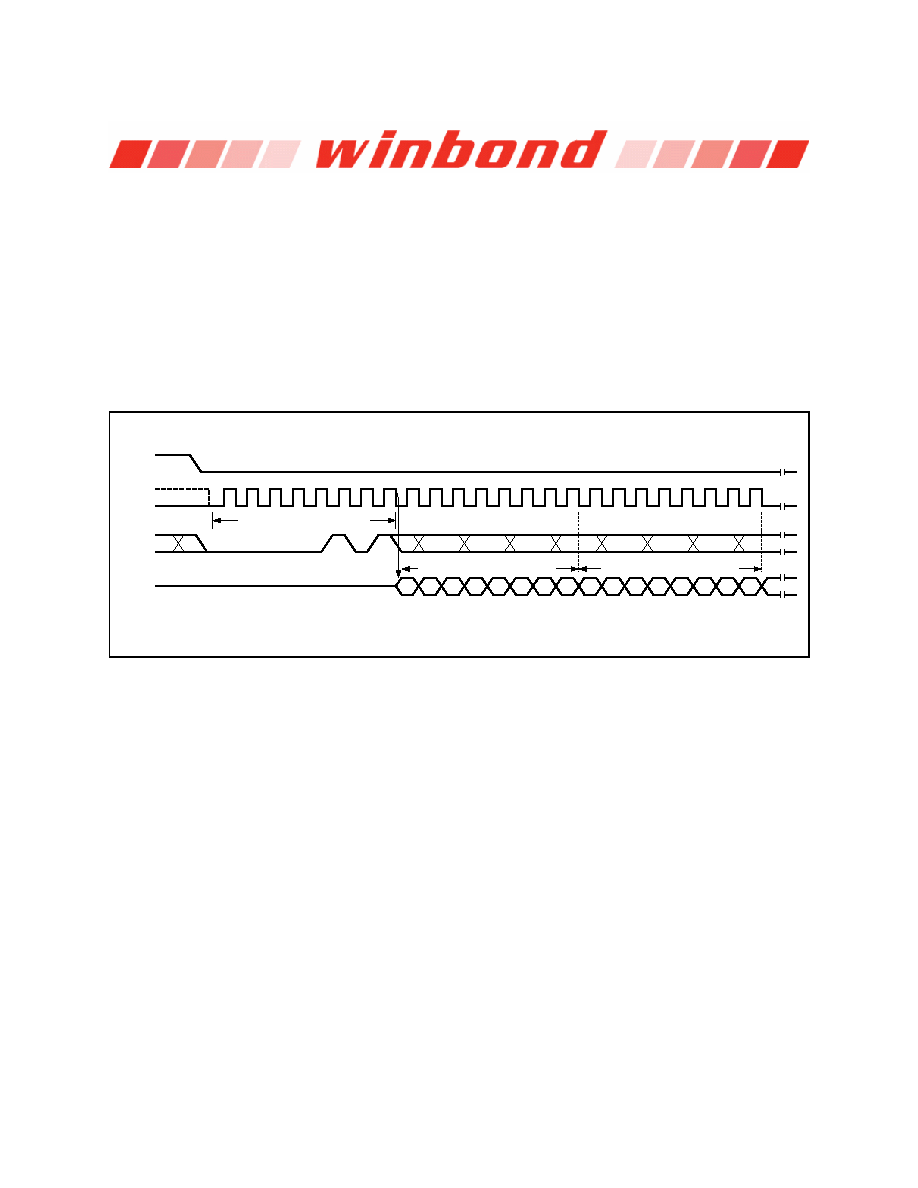

7.2.8 Read Status Register-1 (05h) and Read Status Register-2 (35h)

The Read Status Register instructions allow the 8-bit Status Registers to be read. The instruction is

entered by driving /CS low and shifting the instruction code “05h” for Status Register-1 or “35h” for Status

Register-2 into the DI pin on the rising edge of CLK. The status register bits are then shifted out on the DO

pin at the falling edge of CLK with most significant bit (MSB) first as shown in Figure 7. The Status

Register bits are shown in Figure 3a and 3b and include the BUSY, WEL, BP2-BP0, TB, SEC, SRP0,

SRP1, QE, LB[3:1], CMP and SUS bits (see Status Register section earlier in this datasheet).

The Read Status Register instruction may be used at any time, even while a Program, Erase or Write

Status Register cycle is in progress. This allows the BUSY status bit to be checked to determine when the

cycle is complete and if the device can accept another instruction. The Status Register can be read

continuously, as shown in Figure 7. The instruction is completed by driving /CS high.

/CS

CLK

DI

(IO

0)

DO

Mode 0

Mode 3

0

1

2

3

4

5

6

7

Instruction (05h or 35h)

High Impedance

8

9

10

11

12

13

14

15

16

17

18

19

20

21

22

23

7

6

5

4

3

2

1

0

7

6

5

4

3

2

1

0

7

Status Register 1 or 2 out

**

= MSB

*

Figure 7. Read Status Register Instruction Sequence Diagram

7.2.9 Write Status Register (01h)

The Write Status Register instruction allows the Status Register to be written. Only non-volatile Status

Register bits SRP0, SEC, TB, BP2, BP1, BP0 (bits 7 thru 2 of Status Register-1) and CMP, LB3, LB2,

LB1, QE, SRP1 (bits 14 thru 8 of Status Register-2) can be written to. All other Status Register bit

locations are read-only and will not be affected by the Write Status Register instruction. LB[3:1] are non-

volatile OTP bits, once it is set to 1, it can not be cleared to 0. The Status Register bits are shown in

Figure 3 and described in 7.1.

To write non-volatile Status Register bits, a standard Write Enable (06h) instruction must previously have

been executed for the device to accept the Write Status Register Instruction (Status Register bit WEL

must equal 1). Once write enabled, the instruction is entered by driving /CS low, sending the instruction

code “01h”, and then writing the status register data byte as illustrated in Figure 8.

To write volatile Status Register bits, a Write Enable for Volatile Status Register (50h) instruction must

have been executed prior to the Write Status Register instruction (Status Register bit WEL remains 0).

However, SRP1 and LB3, LB2, LB1 can not be changed from “1” to “0” because of the OTP protection for

these bits. Upon power off, the volatile Status Register bit values will be lost, and the non-volatile Status

Register bit values will be restored when power on again.

相关PDF资料 |

PDF描述 |

|---|---|

| WF128K32-150G2LC5 | 128K X 32 FLASH 5V PROM MODULE, 150 ns, CQFP68 |

| WS128K32L-55G2UCA | 128K X 32 MULTI DEVICE SRAM MODULE, 55 ns, CQFP68 |

| WE128K32N-200HSQ | 512K X 8 EEPROM 5V MODULE, 200 ns, CHIP66 |

| WF128K32NA-150HC | 512K X 8 FLASH 12V PROM MODULE, 150 ns, CHIP66 |

| WS512K32-35HI | 2M X 8 MULTI DEVICE SRAM MODULE, 35 ns, CHIP66 |

相关代理商/技术参数 |

参数描述 |

|---|---|

| W25Q16CVZPAP | 制造商:WINBOND 制造商全称:Winbond 功能描述:3V 16M-BIT SERIAL FLASH MEMORY WITH DUAL AND QUAD SPI |

| W25Q16CVZPIG | 功能描述:IC SPI FLASH 16MBIT 8WSON RoHS:是 类别:集成电路 (IC) >> 存储器 系列:SpiFlash® 标准包装:2,500 系列:- 格式 - 存储器:EEPROMs - 串行 存储器类型:EEPROM 存储容量:1K (128 x 8) 速度:100kHz 接口:UNI/O?(单线) 电源电压:1.8 V ~ 5.5 V 工作温度:-40°C ~ 85°C 封装/外壳:8-TSSOP,8-MSOP(0.118",3.00mm 宽) 供应商设备封装:8-MSOP 包装:带卷 (TR) |

| W25Q16CVZPIP | 制造商:WINBOND 制造商全称:Winbond 功能描述:3V 16M-BIT SERIAL FLASH MEMORY WITH DUAL AND QUAD SPI |

| W25Q16DVDAIG | 制造商:WINBOND 制造商全称:Winbond 功能描述:3V 16M-BIT SERIAL FLASH MEMORY WITH DUAL AND QUAD SPI |

| W25Q16DVDAIP | 制造商:WINBOND 制造商全称:Winbond 功能描述:3V 16M-BIT SERIAL FLASH MEMORY WITH DUAL AND QUAD SPI |

发布紧急采购,3分钟左右您将得到回复。