- 您现在的位置:买卖IC网 > PDF目录68459 > W6692ACF (WINBOND ELECTRONICS CORP) DATACOM, ISDN CONTROLLER, PQFP100 PDF资料下载

参数资料

| 型号: | W6692ACF |

| 厂商: | WINBOND ELECTRONICS CORP |

| 元件分类: | 数字传输电路 |

| 英文描述: | DATACOM, ISDN CONTROLLER, PQFP100 |

| 封装: | QFP-100 |

| 文件页数: | 17/98页 |

| 文件大小: | 584K |

| 代理商: | W6692ACF |

第1页第2页第3页第4页第5页第6页第7页第8页第9页第10页第11页第12页第13页第14页第15页第16页当前第17页第18页第19页第20页第21页第22页第23页第24页第25页第26页第27页第28页第29页第30页第31页第32页第33页第34页第35页第36页第37页第38页第39页第40页第41页第42页第43页第44页第45页第46页第47页第48页第49页第50页第51页第52页第53页第54页第55页第56页第57页第58页第59页第60页第61页第62页第63页第64页第65页第66页第67页第68页第69页第70页第71页第72页第73页第74页第75页第76页第77页第78页第79页第80页第81页第82页第83页第84页第85页第86页第87页第88页第89页第90页第91页第92页第93页第94页第95页第96页第97页第98页

Data Sheet

W6692A PCI ISDN S/T-Controller

Publication Release Date:

Mar,2000

Revision 1.0

-24 -

A 96 kHz continuous pulse with alternating polarities is sent.

Send Single Pulses

A 2 KHz , isolated pulse with alternating polarities is sent.

Layer 1 Reset

A layer 1 reset command forces the transmission of INFO 0 and disables the S line awake detector. Thus activation from NT

is not possible.

There is no indication in reset state. The reset state can be left only with ECK command.

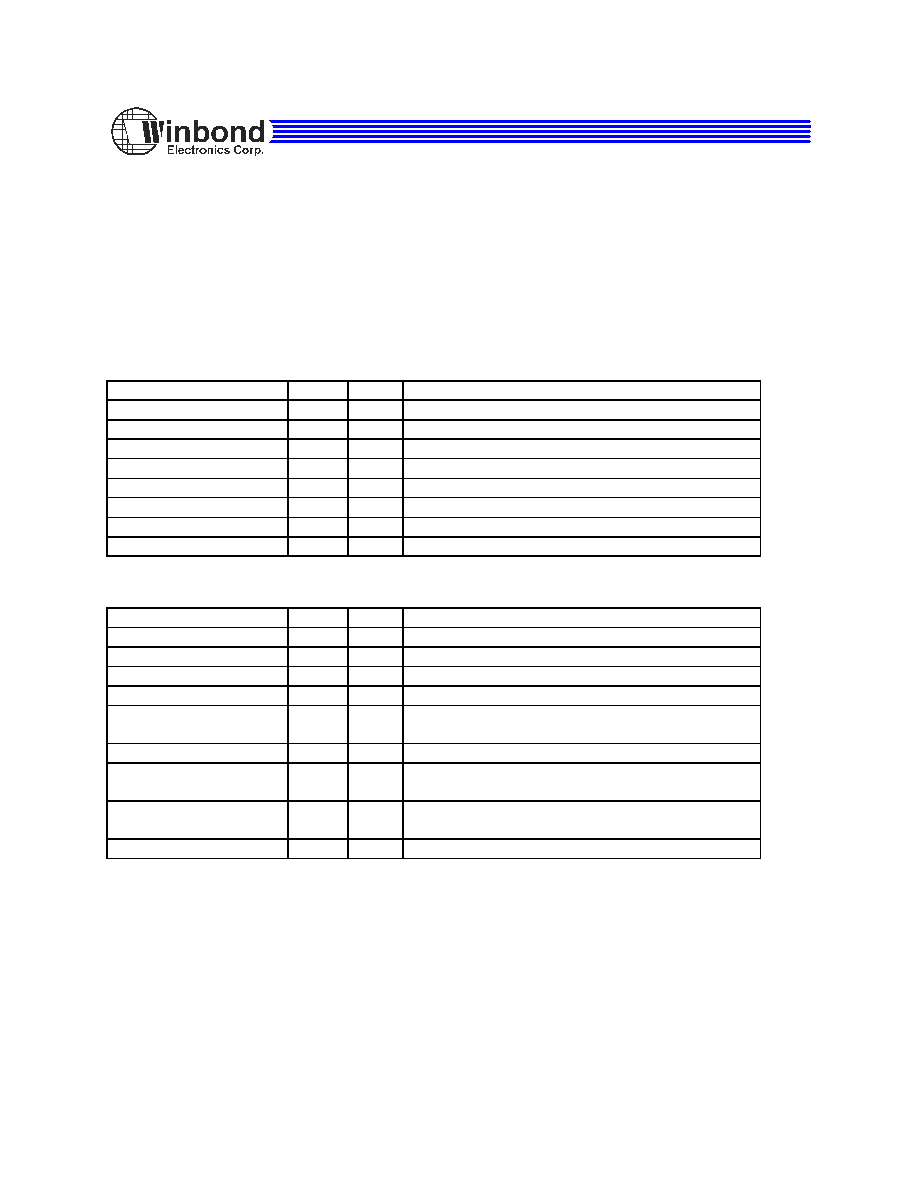

TABLE 7.2 LAYER 1 COMMAND CODES

Command

Symbol

Code

Description

Enable clock

ECK

0000

Enable internal clocks

Layer 1 reset

RST

0001

Layer 1 reset

Send continuous pulses

SCP

0100

Send continuous pulses at 96 kHz

Send single pulses

SSP

0010

Send isolated pulses at 2 kHz

Activate request at priority 8

AR8

1000

Activate layer 1 and set D channel priority level to 8

Activate request at priority 10

AR10

1001

Activate layer 1 and set D channel priority to 10

Enable analog loopback

EAL

1010

Enable analog loopback

Deactivate layer 1

DRC

1111

Deactivate layer 1 and disable internal clocks

TABLE 7.3 LAYER 1 INDICATION CODES

Indication

Symbol

Code

Descriptions

Clock Enabled

CE

0111

Internal clocks are enabled

Deactivate request downstream

DRD

0000

Deactivation request by S interface, i.e INFO 0 received

Level detected

LD

0100

Signal received, receiver not synchronous

Activate request downstream

ARD

1000

INFO 2 received

Test indication

TI

1010

Analog loopback activated or continuous zeros or single zeros

transmitted

Awake test indication

ATI

1011

Level detected during test function

Activate indication with priority

class 1

AI8

1100

INFO 4 received, D channel priority is 8 or 9

Activate indication with priority

class 2

AI10

1101

INFO 4 received, D channel priority is 10 or 11

Clock disabled

CD

1111

Layer 1 deactivated, internal clocks are disabled

7.2.3.2 State Transition Diagrams

The followings are the state transition diagrams, which implement the activation/deactivation state matrix in I.430 (TABLE

5/I.430). The "command" and "s receive" entries in each state octagon keep the state, the "indication" and "s transmit" entries in

each state octagon are the state outputs. For example, at "F3 Deactivated with clock" state, the layer 1 will stay at this state if the

command is "ECK" and the INFO 0 is received on S interface. At this state, it provides "CE" indication to the microprocessor

and transmits INFO 0 on S interface. The "AR8/10" command causes transition to F4 and non-INFO 0 signal causes transition to

相关PDF资料 |

PDF描述 |

|---|---|

| W6694ACD | DATACOM, ISDN CONTROLLER, PQFP48 |

| W671320P | TELECOM-SLIC, PQCC28 |

| W671361P | TELECOM-SLIC, PQCC28 |

| W671361Y | TELECOM-SLIC, QCC32 |

| W671310P | TELECOM-SLIC, PQCC28 |

相关代理商/技术参数 |

参数描述 |

|---|---|

| W6694 | 制造商:WINBOND 制造商全称:Winbond 功能描述:USB Bus ISDN S/T-Controller |

| W6694A | 制造商:未知厂家 制造商全称:未知厂家 功能描述:TE Mode S/T Controller with USB 1.1 Interface |

| W6694CD | 制造商:WINBOND 制造商全称:Winbond 功能描述:USB Bus ISDN S/T-Controller |

| W66ARX-18 | 制造商:Magnecraft 功能描述: |

| W66MAF185X | 制造商:Panasonic Industrial Company 功能描述:CRT |

发布紧急采购,3分钟左右您将得到回复。