- 您现在的位置:买卖IC网 > PDF目录68459 > W6692ACF (WINBOND ELECTRONICS CORP) DATACOM, ISDN CONTROLLER, PQFP100 PDF资料下载

参数资料

| 型号: | W6692ACF |

| 厂商: | WINBOND ELECTRONICS CORP |

| 元件分类: | 数字传输电路 |

| 英文描述: | DATACOM, ISDN CONTROLLER, PQFP100 |

| 封装: | QFP-100 |

| 文件页数: | 6/98页 |

| 文件大小: | 584K |

| 代理商: | W6692ACF |

第1页第2页第3页第4页第5页当前第6页第7页第8页第9页第10页第11页第12页第13页第14页第15页第16页第17页第18页第19页第20页第21页第22页第23页第24页第25页第26页第27页第28页第29页第30页第31页第32页第33页第34页第35页第36页第37页第38页第39页第40页第41页第42页第43页第44页第45页第46页第47页第48页第49页第50页第51页第52页第53页第54页第55页第56页第57页第58页第59页第60页第61页第62页第63页第64页第65页第66页第67页第68页第69页第70页第71页第72页第73页第74页第75页第76页第77页第78页第79页第80页第81页第82页第83页第84页第85页第86页第87页第88页第89页第90页第91页第92页第93页第94页第95页第96页第97页第98页

Data Sheet

W6692A PCI ISDN S/T-Controller

Publication Release Date:

Mar,2000

Revision 1.0

-14 -

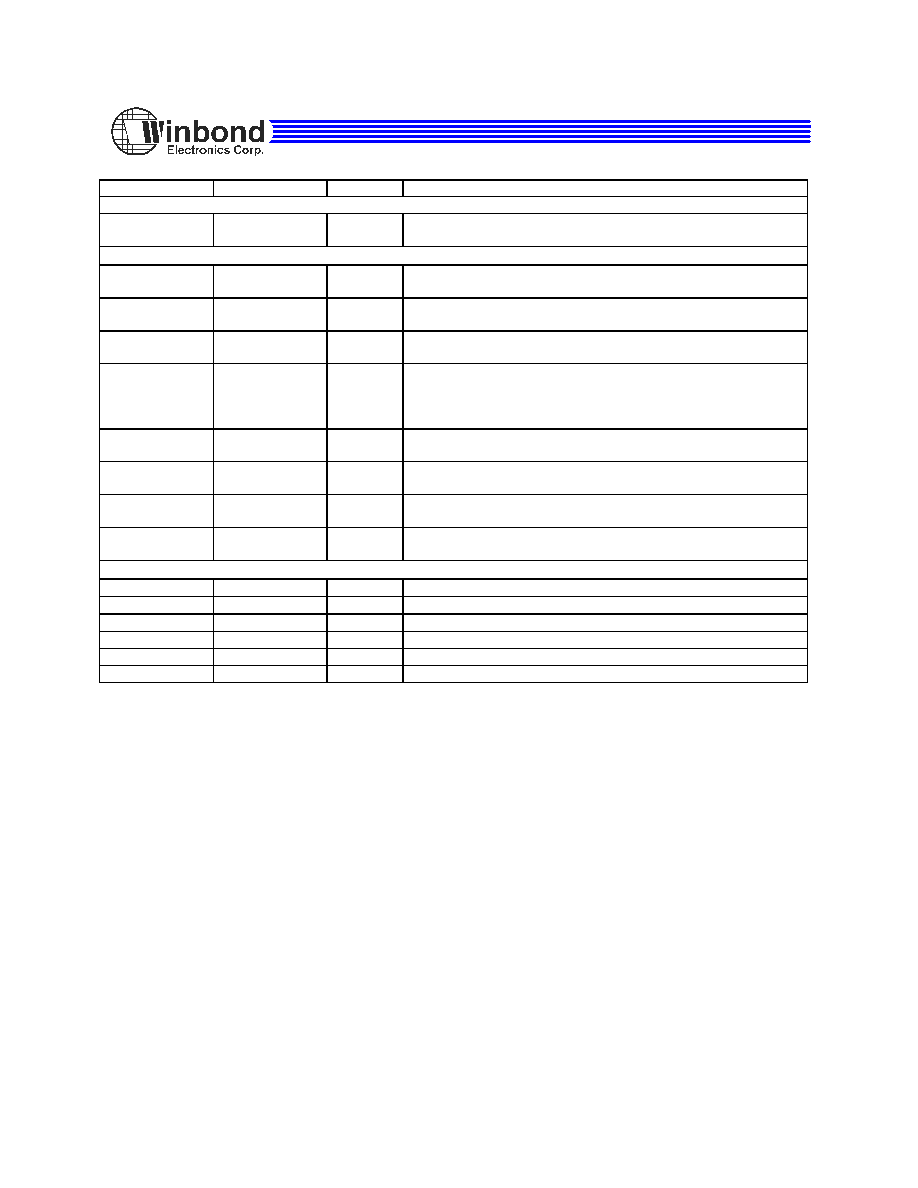

TESTP

61

I

Used to enable normal operation (1) or enter test mode (0).

PCI Power Management

PME

60

O

Power Management Event Signal. Level triggered, active HIGH. Drive

a transistor to PME# in PCI slot.

Peripheral Control

TOUT2

20

O

Timer 2 output. A square wave with 50 % duty cycle, 1~63 ms period

can be generated.

XINTIN0

52

I

A level change (either direction) will generate a maskable interrupt on

the PCI bus interrupt request pin INTA#.

XINTIN1

53

I

A level change (either direction) will generate a maskable interrupt on

the PCI bus interrupt request pin INTA#.

IO10-IO0

79,78,77,29,28,

27,26,4,3,2,1

I/O

When confiured as simple IO mode (PCTL:XMODE = 0), these pins

can read/write data from/to peripheral components. The pin directions

are selected via register. After hardware reset, the output drivers are

disabled.

XAD7-XAD0

29,28,27,26,

4,3,2,1

I/O

When configured as microprocessor mode (PCTL:XMODE = 1),

address and data are multiplexed on these pins.

XALE

77

O

When configured as microprocessor mode (PCTL:XMODE = 1), this is

the Address Latch Enable output.

XRDB

78

O

When configured as microprocessor mode (PCTL:XMODE = 1), this is

the read pulse.

XWRB

79

O

When configured as microprocessor mode (PCTL:XMODE = 1), this is

the write pulse.

Power and Ground

VDDD

17,58,67,83

I

Digital Power Supply (5V

±5%).

VDDA

51

I

Analog Power Supply (5V

±5%).

VDDB

6,32,43,89

I

PCI Bus Power Supply (5V

±5%).

VSSD

16,59,68,82

I

Digital Ground.

VSSA

48

I

Analog Ground.

VSSB

5,31,42,88

I

PCI Bus Ground.

相关PDF资料 |

PDF描述 |

|---|---|

| W6694ACD | DATACOM, ISDN CONTROLLER, PQFP48 |

| W671320P | TELECOM-SLIC, PQCC28 |

| W671361P | TELECOM-SLIC, PQCC28 |

| W671361Y | TELECOM-SLIC, QCC32 |

| W671310P | TELECOM-SLIC, PQCC28 |

相关代理商/技术参数 |

参数描述 |

|---|---|

| W6694 | 制造商:WINBOND 制造商全称:Winbond 功能描述:USB Bus ISDN S/T-Controller |

| W6694A | 制造商:未知厂家 制造商全称:未知厂家 功能描述:TE Mode S/T Controller with USB 1.1 Interface |

| W6694CD | 制造商:WINBOND 制造商全称:Winbond 功能描述:USB Bus ISDN S/T-Controller |

| W66ARX-18 | 制造商:Magnecraft 功能描述: |

| W66MAF185X | 制造商:Panasonic Industrial Company 功能描述:CRT |

发布紧急采购,3分钟左右您将得到回复。