- 您现在的位置:买卖IC网 > PDF目录68583 > WJLXT971ALC.A4-857344 (CORTINA SYSTEMS INC) DATACOM, ETHERNET TRANSCEIVER, PQFP64 PDF资料下载

参数资料

| 型号: | WJLXT971ALC.A4-857344 |

| 厂商: | CORTINA SYSTEMS INC |

| 元件分类: | 网络接口 |

| 英文描述: | DATACOM, ETHERNET TRANSCEIVER, PQFP64 |

| 封装: | 10 X 10 MM, 1.40 MM HEIGHT, ROHS COMPLIANT, LQFP-64 |

| 文件页数: | 22/80页 |

| 文件大小: | 931K |

| 代理商: | WJLXT971ALC.A4-857344 |

第1页第2页第3页第4页第5页第6页第7页第8页第9页第10页第11页第12页第13页第14页第15页第16页第17页第18页第19页第20页第21页当前第22页第23页第24页第25页第26页第27页第28页第29页第30页第31页第32页第33页第34页第35页第36页第37页第38页第39页第40页第41页第42页第43页第44页第45页第46页第47页第48页第49页第50页第51页第52页第53页第54页第55页第56页第57页第58页第59页第60页第61页第62页第63页第64页第65页第66页第67页第68页第69页第70页第71页第72页第73页第74页第75页第76页第77页第78页第79页第80页

Page 29

Cortina Systems LXT972A Single-Port 10/100 Mbps PHY Transceiver

LXT972A PHY

Datasheet

249186, Revision 5.2

13 September 2007

5.5 Establishing Link

5.5.1

Auto-Negotiation

If not configured for forced operation, the LXT972A PHY attempts to auto-negotiate with

its link partner by sending Fast Link Pulse (FLP) bursts. Each burst consists of up to 33

link pulses spaced 62.5

μs apart. Odd link pulses (clock pulses) are always present. Even

link pulses (data pulses) may be absent or present to indicate a ‘0’ or a ‘1’. Each FLP burst

exchanges 16 bits of data, which are referred to as a “link code word”. All devices that

support auto-negotiation must implement the “Base Page” defined by the IEEE 802.3

standard (Registers 4 and 5).

The LXT972A PHY also supports the optional “Next Page” function as listed in Table 46,

5.5.1.1

Base Page Exchange

By exchanging Base Pages, the LXT972A PHY and its link partner communicate their

capabilities to each other. Both sides must receive at least three consecutive identical

base pages for negotiation to continue. Each side identifies the highest common

capabilities that both sides support, and each side configures itself accordingly.

5.5.1.2

Manual Next Page Exchange

“Next Page Exchange” information is additional information that exceeds the information

required by Base Page exchange and that is sent by “Next Pages”. The LXT972A PHY

fully supports the IEEE 802.3 standard method of negotiation through the Next Page

exchange.

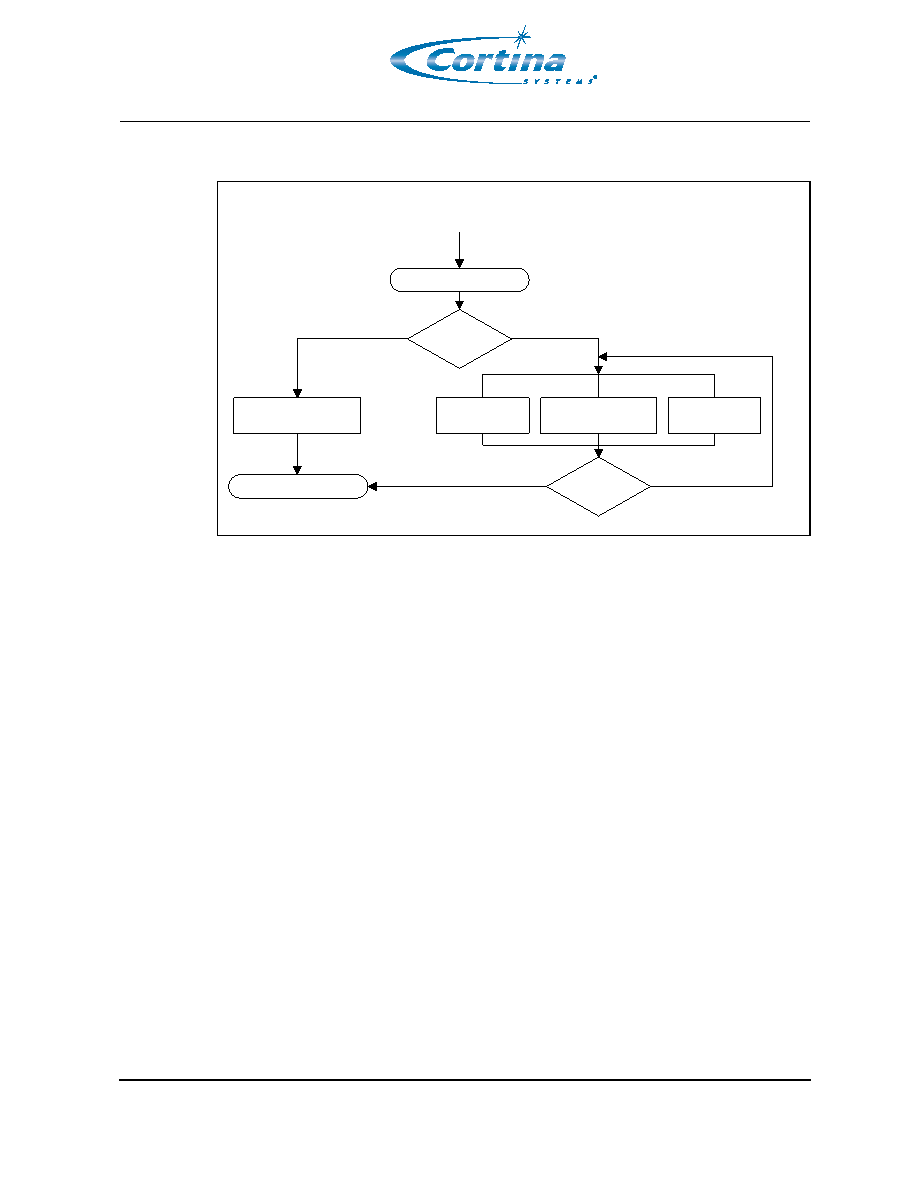

Figure 6

Link Establishment Overview

Check Value

0.12

Start

Done

Enable

Auto-Neg/Parallel Detection

Go To Forced

Settings

Attempt Auto-

Negotiation

Listen for 10T

Link Pulses

Listen for 100TX

Idle Symbols

Link Up?

NO

YES

Power-Up, Reset,

or Link Failure

Disable

Auto-Negotiation

0.12 = 0

0.12 = 1

B3496-01

相关PDF资料 |

PDF描述 |

|---|---|

| WJLXT971ALE.A4-857343 | DATACOM, ETHERNET TRANSCEIVER, PQFP64 |

| WJLXT971ALE.A4-857346 | DATACOM, ETHERNET TRANSCEIVER, PQFP64 |

| WJLXT972ALC.A4-857341 | DATACOM, ETHERNET TRANSCEIVER, PQFP64 |

| WJLXT972ALC.A4-857345 | DATACOM, ETHERNET TRANSCEIVER, PQFP64 |

| WJLXT971ALC.A4SE000 | DATACOM, ETHERNET TRANSCEIVER, PQFP64 |

相关代理商/技术参数 |

参数描述 |

|---|---|

| WJLXT971ALE.A4 | 功能描述:IC XCVR 3V 2-SPEED ETHER 64LQFP RoHS:是 类别:集成电路 (IC) >> 接口 - 驱动器,接收器,收发器 系列:- 标准包装:1,000 系列:- 类型:收发器 驱动器/接收器数:2/2 规程:RS232 电源电压:3 V ~ 5.5 V 安装类型:表面贴装 封装/外壳:16-SOIC(0.295",7.50mm 宽) 供应商设备封装:16-SOIC 包装:带卷 (TR) |

| WJLXT971ALE.A4-857343 | 功能描述:TXRX ETH 10/100 SGL PORT 64-LQFP RoHS:是 类别:集成电路 (IC) >> 接口 - 驱动器,接收器,收发器 系列:- 产品培训模块:Lead (SnPb) Finish for COTS Obsolescence Mitigation Program 标准包装:2,500 系列:- 类型:发射器 驱动器/接收器数:4/0 规程:RS422,RS485 电源电压:4.75 V ~ 5.25 V 安装类型:表面贴装 封装/外壳:16-SOIC(0.154",3.90mm 宽) 供应商设备封装:16-SOIC 包装:带卷 (TR) |

| WJLXT971ALE.A4-857346 | 制造商:Cortina Systems Inc 功能描述:PHY 1-CH 10Mbps/100Mbps 64-Pin LQFP T/R |

| WJLXT971CA4 | 制造商:Intel 功能描述: |

| WJLXT972ALC.A4 | 功能描述:IC TRANS 3.3V ETHERNET 64-LQFP RoHS:是 类别:集成电路 (IC) >> 接口 - 驱动器,接收器,收发器 系列:- 产品培训模块:Lead (SnPb) Finish for COTS Obsolescence Mitigation Program 标准包装:25 系列:- 类型:收发器 驱动器/接收器数:2/2 规程:RS232 电源电压:4.5 V ~ 5.5 V 安装类型:通孔 封装/外壳:16-DIP(0.300",7.62mm) 供应商设备封装:16-PDIP 包装:管件 |

发布紧急采购,3分钟左右您将得到回复。