- 您现在的位置:买卖IC网 > PDF目录68583 > WJLXT971ALC.A4-857344 (CORTINA SYSTEMS INC) DATACOM, ETHERNET TRANSCEIVER, PQFP64 PDF资料下载

参数资料

| 型号: | WJLXT971ALC.A4-857344 |

| 厂商: | CORTINA SYSTEMS INC |

| 元件分类: | 网络接口 |

| 英文描述: | DATACOM, ETHERNET TRANSCEIVER, PQFP64 |

| 封装: | 10 X 10 MM, 1.40 MM HEIGHT, ROHS COMPLIANT, LQFP-64 |

| 文件页数: | 72/80页 |

| 文件大小: | 931K |

| 代理商: | WJLXT971ALC.A4-857344 |

第1页第2页第3页第4页第5页第6页第7页第8页第9页第10页第11页第12页第13页第14页第15页第16页第17页第18页第19页第20页第21页第22页第23页第24页第25页第26页第27页第28页第29页第30页第31页第32页第33页第34页第35页第36页第37页第38页第39页第40页第41页第42页第43页第44页第45页第46页第47页第48页第49页第50页第51页第52页第53页第54页第55页第56页第57页第58页第59页第60页第61页第62页第63页第64页第65页第66页第67页第68页第69页第70页第71页当前第72页第73页第74页第75页第76页第77页第78页第79页第80页

Page 74

Cortina Systems LXT972A Single-Port 10/100 Mbps PHY Transceiver

LXT972A PHY

Datasheet

249186, Revision 5.2

13 September 2007

9.0 Register Definitions -

Product-Specific Registers

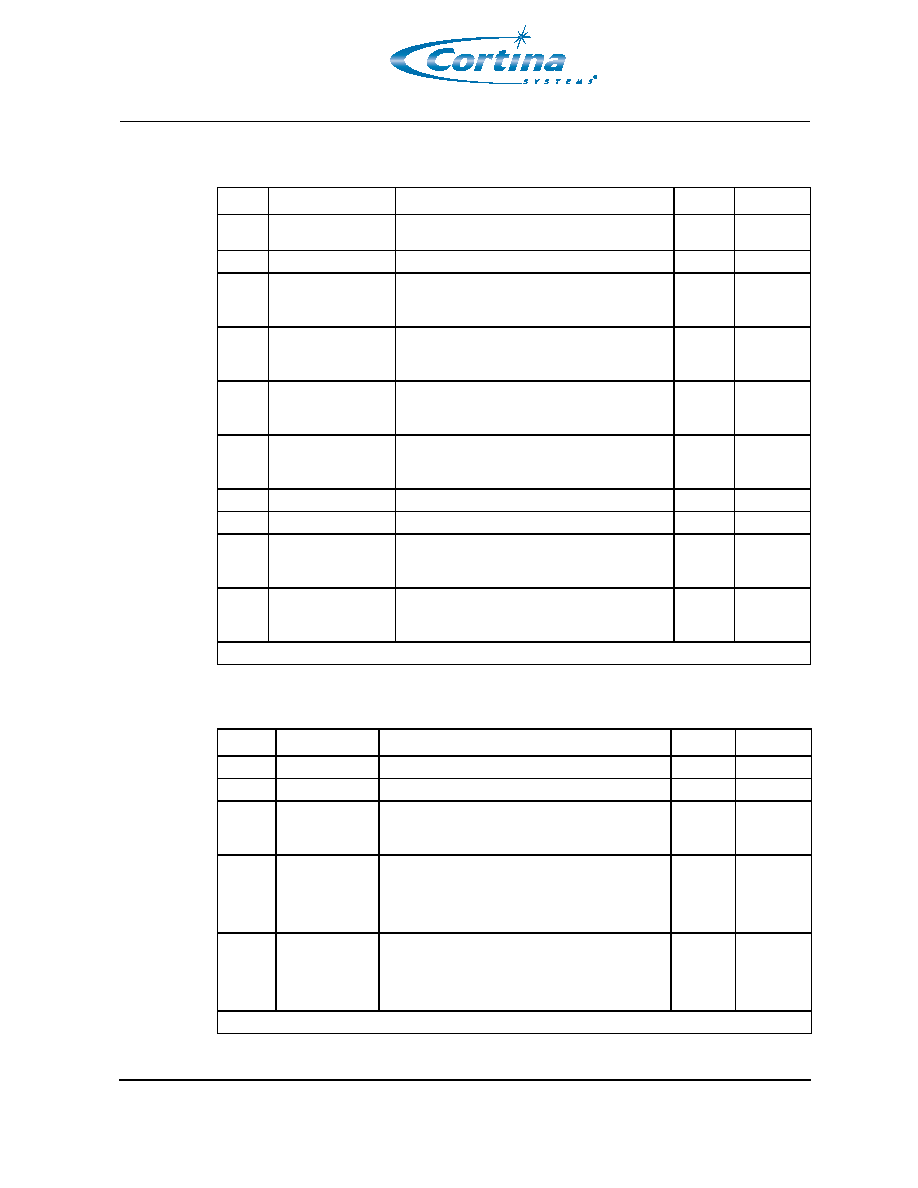

Table 51

Interrupt Enable Register - Address 18, Hex 12

Bit

Name

Description

Type 1

Default

18.

15:9

Reserved

Write as ‘0’. Ignore on Read.

R/W

N/A

18.8

Reserved

Write as ‘0’. Ignore on Read.

R/W

0

18.7

ANMSK

Mask for Auto Negotiate Complete

0 = Do not allow event to cause interrupt.

1 = Enable event to cause interrupt.

R/W

0

18.6

SPEEDMSK

Mask for Speed Interrupt

0 = Do not allow event to cause interrupt.

1 = Enable event to cause interrupt.

R/W

0

18.5

DUPLEXMSK

Mask for Duplex Interrupt

0 = Do not allow event to cause interrupt.

1 = Enable event to cause interrupt.

R/W

0

18.4

LINKMSK

Mask for Link Status Interrupt

0 = Do not allow event to cause interrupt.

1 = Enable event to cause interrupt.

R/W

0

18.3

Reserved

Write as ‘0’. Ignore on Read.

R/W

0

18.2

Reserved

Write as ‘0’. Ignore on Read.

R/W

0

18.1

INTEN

Interrupt Enable.

0 = Disable interrupts.

1 = Enable interrupts.

R/W

0

18.0

TINT

Test Force Interrupt

0 = Normal operation.

1 = Force interrupt on MDINT_L

R/W

0

1. R/W = Read /Write

Table 52

Status Change Register - Address 19, Hex 13 (Sheet 1 of 2)

Bit

Name

Description

Type 1

Default

19.15:9

Reserved

Ignore on Read.

RO

N/A

19.8

Reserved

Ignore on Read.

RO

0

19.7

ANDONE

Auto-negotiation Status

0 = Auto-negotiation has not completed.

1 = Auto-negotiation has completed.

RO/

SC

N/A

19.6

SPEEDCHG

Speed Change Status

0 = A Speed Change has not occurred since last

reading this register.

1 = A Speed Change has occurred since last reading

this register.

RO/

SC

0

19.5

DUPLEXCHG

Duplex Change Status

0 = A Duplex Change has not occurred since last

reading this register.

1 = A Duplex Change has occurred since last

reading this register.

RO/

SC

0

1. R/W = Read/Write, RO = Read Only, SC = Self Clearing.

相关PDF资料 |

PDF描述 |

|---|---|

| WJLXT971ALE.A4-857343 | DATACOM, ETHERNET TRANSCEIVER, PQFP64 |

| WJLXT971ALE.A4-857346 | DATACOM, ETHERNET TRANSCEIVER, PQFP64 |

| WJLXT972ALC.A4-857341 | DATACOM, ETHERNET TRANSCEIVER, PQFP64 |

| WJLXT972ALC.A4-857345 | DATACOM, ETHERNET TRANSCEIVER, PQFP64 |

| WJLXT971ALC.A4SE000 | DATACOM, ETHERNET TRANSCEIVER, PQFP64 |

相关代理商/技术参数 |

参数描述 |

|---|---|

| WJLXT971ALE.A4 | 功能描述:IC XCVR 3V 2-SPEED ETHER 64LQFP RoHS:是 类别:集成电路 (IC) >> 接口 - 驱动器,接收器,收发器 系列:- 标准包装:1,000 系列:- 类型:收发器 驱动器/接收器数:2/2 规程:RS232 电源电压:3 V ~ 5.5 V 安装类型:表面贴装 封装/外壳:16-SOIC(0.295",7.50mm 宽) 供应商设备封装:16-SOIC 包装:带卷 (TR) |

| WJLXT971ALE.A4-857343 | 功能描述:TXRX ETH 10/100 SGL PORT 64-LQFP RoHS:是 类别:集成电路 (IC) >> 接口 - 驱动器,接收器,收发器 系列:- 产品培训模块:Lead (SnPb) Finish for COTS Obsolescence Mitigation Program 标准包装:2,500 系列:- 类型:发射器 驱动器/接收器数:4/0 规程:RS422,RS485 电源电压:4.75 V ~ 5.25 V 安装类型:表面贴装 封装/外壳:16-SOIC(0.154",3.90mm 宽) 供应商设备封装:16-SOIC 包装:带卷 (TR) |

| WJLXT971ALE.A4-857346 | 制造商:Cortina Systems Inc 功能描述:PHY 1-CH 10Mbps/100Mbps 64-Pin LQFP T/R |

| WJLXT971CA4 | 制造商:Intel 功能描述: |

| WJLXT972ALC.A4 | 功能描述:IC TRANS 3.3V ETHERNET 64-LQFP RoHS:是 类别:集成电路 (IC) >> 接口 - 驱动器,接收器,收发器 系列:- 产品培训模块:Lead (SnPb) Finish for COTS Obsolescence Mitigation Program 标准包装:25 系列:- 类型:收发器 驱动器/接收器数:2/2 规程:RS232 电源电压:4.5 V ~ 5.5 V 安装类型:通孔 封装/外壳:16-DIP(0.300",7.62mm) 供应商设备封装:16-PDIP 包装:管件 |

发布紧急采购,3分钟左右您将得到回复。