参数资料

| 型号: | X40021V14I-CT1 |

| 厂商: | Intersil |

| 文件页数: | 5/24页 |

| 文件大小: | 0K |

| 描述: | IC VOLTAGE MONITOR DUAL 14-TSSOP |

| 标准包装: | 2,500 |

| 类型: | 多压监控器 |

| 监视电压数目: | 2 |

| 输出: | 开路漏极或开路集电极 |

| 复位: | 低有效 |

| 复位超时: | 可调节/可选择 |

| 电压 - 阀值: | 1.6V,2.9V |

| 工作温度: | -40°C ~ 85°C |

| 安装类型: | 表面贴装 |

| 封装/外壳: | 14-TSSOP(0.173",4.40mm 宽) |

| 供应商设备封装: | 14-TSSOP |

| 包装: | 带卷 (TR) |

�� �

�

�

�X40020,� 40021�

�PRINCIPLES� OF� OPERATION�

�Power-on� Reset�

�Applying� power� to� the� X40020/21� activates� a� Power-�

�on� Reset� Circuit� that� pulls� the� RESET/RESET� pins�

�active.� This� signal� provides� several� benefits.�

�–� It� prevents� the� system� microprocessor� from� starting�

�to� operate� with� insufficient� voltage.�

�–� It� prevents� the� processor� from� operating� prior� to� sta-�

�bilization� of� the� oscillator.�

�–� It� allows� time� for� an� FPGA� to� download� its� configura-�

�tion� prior� to� initialization� of� the� circuit.�

�–� It� prevents� communication� to� the� EEPROM,� greatly�

�Low� Voltage� V2� Monitoring�

�The� X40020/21� also� monitors� a� second� voltage� level� and�

�asserts� V2FAIL� if� the� voltage� falls� below� a� preset� mini-�

�mum� V� TRIP2� .� The� V2FAIL� signal� is� either� ORed� with�

�RESET� to� prevent� the� microprocessor� from� operating� in�

�a� power� fail� or� brownout� condition� or� used� to� interrupt� the�

�microprocessor� with� notification� of� an� impending� power�

�failure.� The� V2FAIL� signal� remains� active� until� the� V� CC�

�drops� below� 1V� (V� CC� falling).� It� also� remains� active� until�

�V2MON� returns� and� exceeds� V� TRIP2� .�

�V2MON� voltage� monitor� is� powered� by� V� OUT.� If� V� CC�

�and� V� BATT� go� away,� V2MON� cannot� be� monitored.�

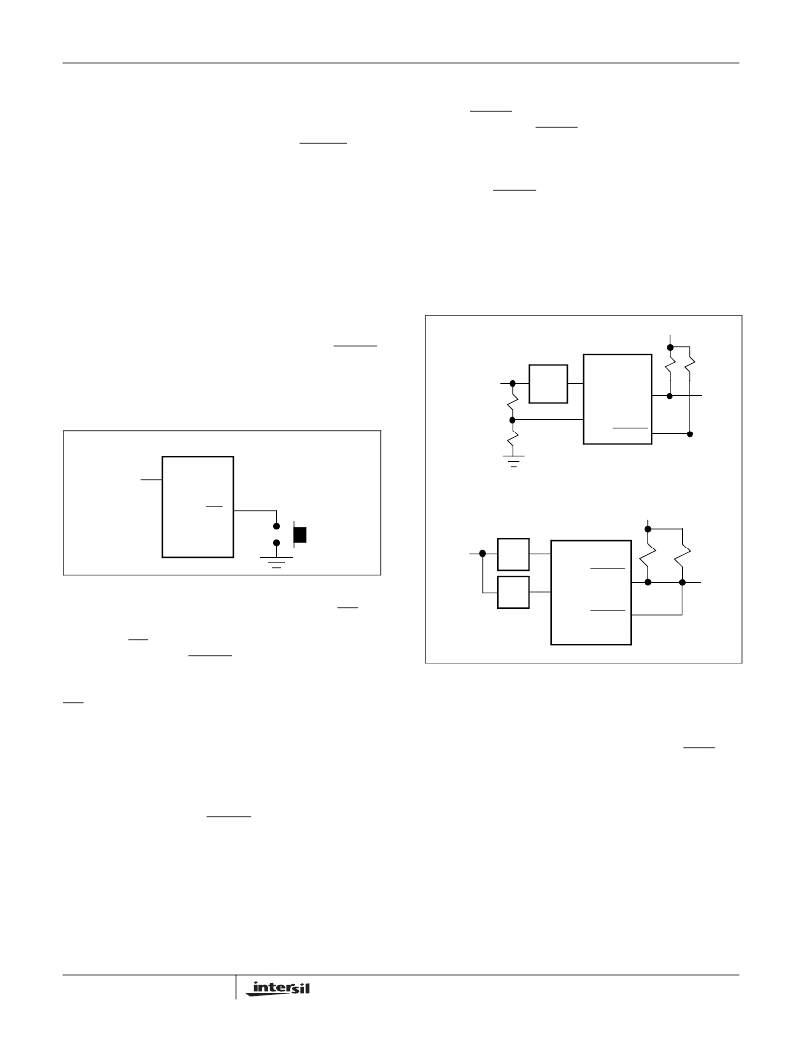

�Figure� 2.� Two� Uses� of� Multiple� Voltage� Monitoring�

�reducing� the� likelihood� of� data� corruption� on� power-up.�

�When� V� CC� exceeds� the� device� V� TRIP1� threshold� value�

�for� t� PURST� (selectable)� the� circuit� releases� the� RESET�

�(X40021)� and� RESET� (X40020)� pin� allowing� the� system�

�to� begin� operation.�

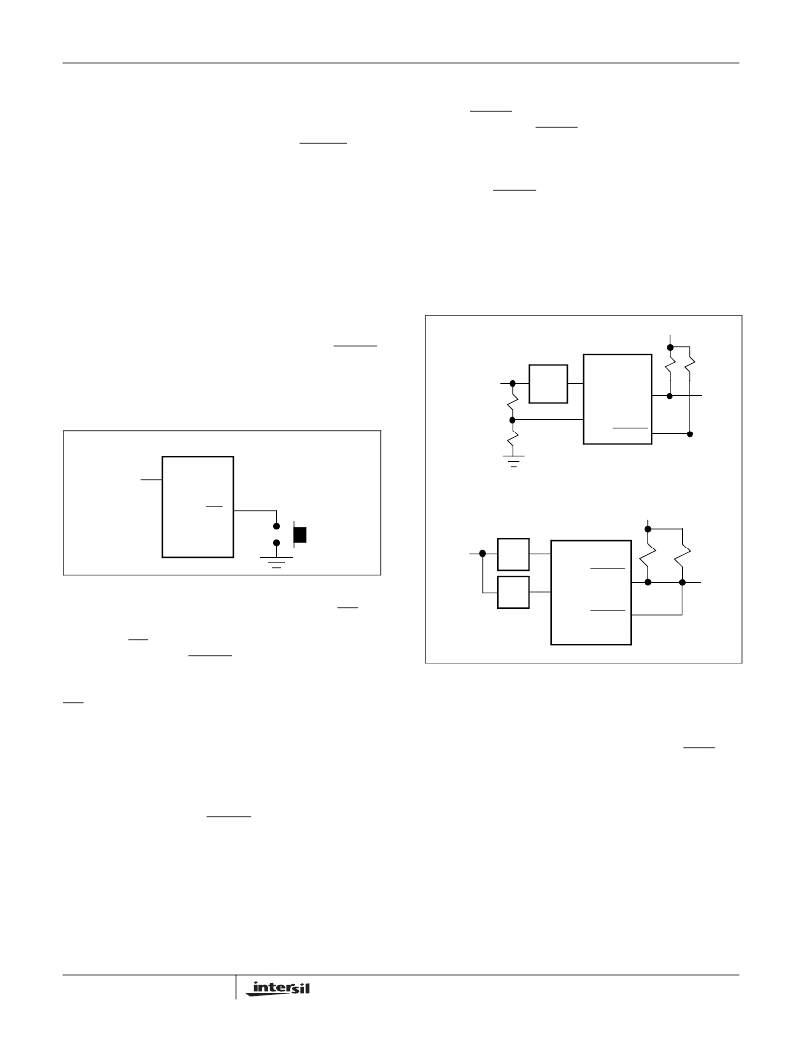

�Figure� 1.� Connecting� a� Manual� Reset� Push-Button�

�Unreg.�

�Supply�

�R�

�5V�

�Reg�

�X40020�

�V� CC�

�RESET�

�V2MON�

�V� OUT�

�System�

�Reset�

�X40020�

�R�

�V2FAIL�

�System�

�Reset�

�RESET�

�MR�

�Resistors� selected� so� 3V� appears� on� V2MON� when� unregulated�

�supply� reaches� 6V.�

�V� OUT�

�Manual�

�Reset�

�Unreg.�

�Supply�

�5V�

�Reg�

�X40021�

�V� CC�

�Manual� Reset�

�By� connecting� a� push-button� directly� from� MR� to�

�3V�

�Reg�

�RESET�

�V2MON�

�V2FAIL�

�System�

�Reset�

�ground,� the� designer� adds� manual� system� reset� capa-�

�bility.� The� MR� pin� is� LOW� while� the� push-button� is�

�closed� and� RESET/RESET� pin� remains� LOW� for�

�t� PURST� or� till� the� push-button� is� released� and� for� t� PURST�

�thereafter.� A� weak� pull� up� resistor� is� connected� to� the�

�MR� pin.�

�Low� Voltage� V1� Monitoring�

�During� operation,� the� X40020/21� monitors� the� V� CC�

�level� and� asserts� RESET� if� supply� voltage� falls� below�

�a� preset� minimum� V� TRIP1� .� The� RESET� signal� prevents�

�the� microprocessor� from� operating� in� a� power� fail� or�

�brownout� condition.� The� V1FAIL� signal� remains� active�

�until� the� voltage� drops� below� 1V.� It� also� remains� active�

�until� V� CC� returns� and� exceeds� V� TRIP1� for� t� PURST� .�

�5�

�Notice:� No� external� components� required� to� monitor� two� voltages.�

�WATCHDOG� TIMER�

�The� Watchdog� Timer� circuit� monitors� the� microprocessor�

�activity� by� monitoring� the� SDA� and� SCL� pins.� A� standard�

�read� or� write� sequence� to� any� slave� address� byte�

�restarts� the� watchdog� timer� and� prevents� the� WDO� sig-�

�nal� to� go� active.� A� minimum� sequence� to� reset� the�

�watchdog� timer� requires� four� microprocessor� instructions�

�namely,� a� Start,� Clock� Low,� Clock� High� and� Stop.� The�

�state� of� two� nonvolatile� control� bits� in� the� Status� Register�

�determine� the� watchdog� timer� period.� The� microproces-�

�sor� can� change� these� watchdog� bits� by� writing� to� the�

�X40020/21� control� register� (also� refer� to� page� 21).�

�FN8112.1�

�May� 17,� 2006�

�相关PDF资料 |

PDF描述 |

|---|---|

| X40035V14I-CT1 | IC VOLTAGE MONITOR TRPL 14-TSSOP |

| X4005S8I-4.5A | IC SUPERVISOR CPU I2C 8-SOIC |

| X40239S16I-BT1 | IC VOLTAGE MON TRPL EE 16-SOIC |

| X40415V8I-CT1 | IC VOLTAGE MON DUAL W/SUP 8TSSOP |

| X40421V14I-CT1 | IC VOLT MON DUAL SUP/SW 14-TSSOP |

相关代理商/技术参数 |

参数描述 |

|---|---|

| X400-22FA | 制造商:MOFLASH SIGNALLING 功能描述:BEACON XENON HIGH OUTPUT |

| X4003 | 制造商:INTERSIL 制造商全称:Intersil Corporation 功能描述:CPU Supervisor |

| X4003_06 | 制造商:INTERSIL 制造商全称:Intersil Corporation 功能描述:CPU Supervisor |

| X40030 | 制造商:INTERSIL 制造商全称:Intersil Corporation 功能描述:Triple Voltage Monitor with Intergrated CPU Supervisor |

| X40030_06 | 制造商:INTERSIL 制造商全称:Intersil Corporation 功能描述:Triple Voltage Monitor with Integrated CPU Supervisor |

发布紧急采购,3分钟左右您将得到回复。