参数资料

| 型号: | X9252YV24IZ-2.7 |

| 厂商: | Intersil |

| 文件页数: | 18/20页 |

| 文件大小: | 0K |

| 描述: | IC POT DGTL QUAD 24-TSSOP |

| 标准包装: | 62 |

| 系列: | XDCP™ |

| 接片: | 256 |

| 电阻(欧姆): | 2.8k |

| 电路数: | 4 |

| 温度系数: | 标准值 ±300 ppm/°C |

| 存储器类型: | 非易失 |

| 接口: | I²C(芯片选择,设备位址,增/减) |

| 电源电压: | 2.7 V ~ 5.5 V |

| 工作温度: | -40°C ~ 85°C |

| 安装类型: | 表面贴装 |

| 封装/外壳: | 24-TSSOP(0.173",4.40mm 宽) |

| 供应商设备封装: | 24-TSSOP |

| 包装: | 管件 |

| 产品目录页面: | 1237 (CN2011-ZH PDF) |

7

FN8167.2

November 14, 2005

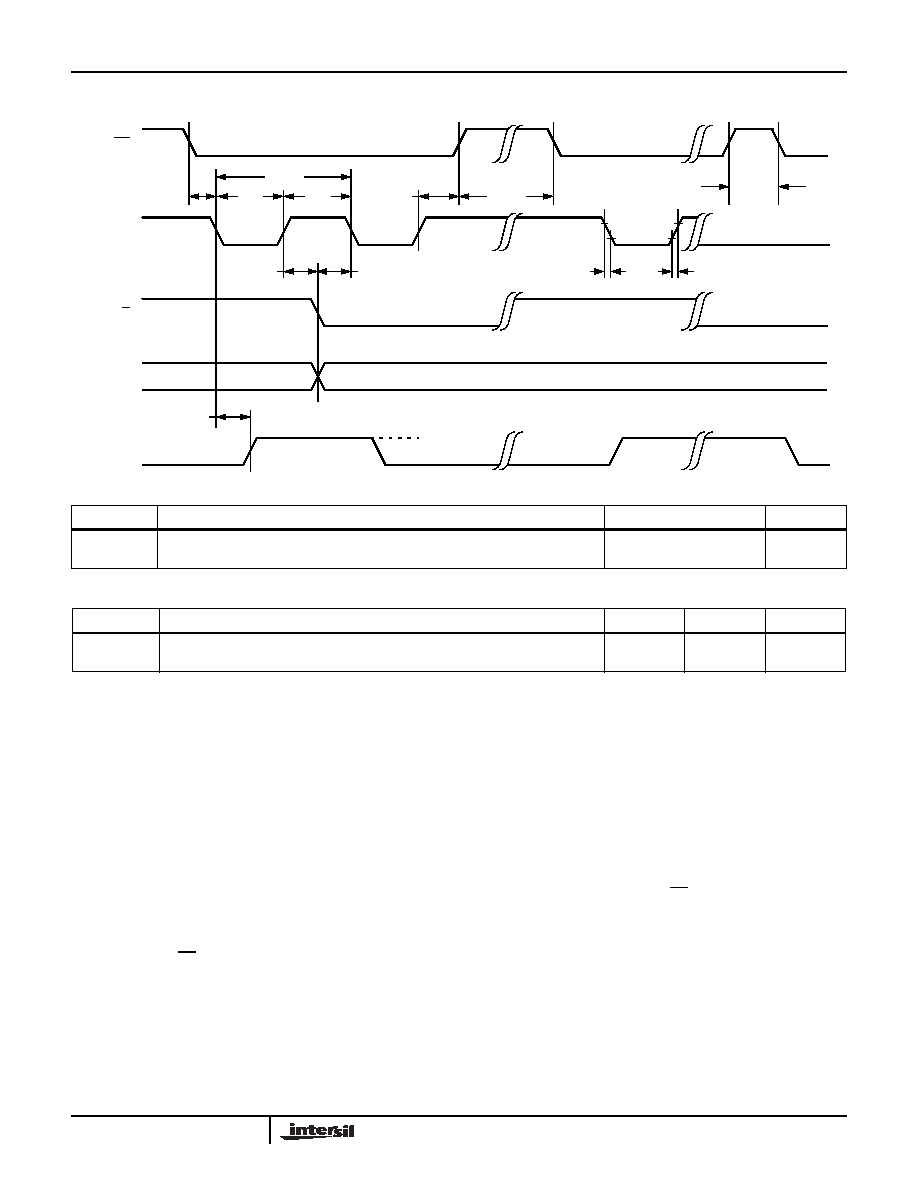

Increment/Decrement Timing

NOTES:

1. Absolute linearity is utilized to determine actual wiper voltage versus expected voltage = [V(RW(n)(actual))-V(RW(n)(expected))]/MI

V(RW(n)(expected)) = n(V(RH)-V(RL))/255 + V(RL), with n from 0 to 255.

2. Relative linearity is a measure of the error in step size between taps = [V(RW(n+1))-(V(RW(n)) + MI)]/MI, with n from 0 to 254

3. 1 Ml = Minimum Increment = [V(RH)-V(RL)]/255.

4. Typical values are for TA = 25°C and nominal supply voltage.

5. This parameter is not 100% tested.

6. Ratiometric temperature coefficient = (V(RW)T1(n)-V(RW)T2(n))/[V(RW)T1(n)(T1-T2)] x 106, with T1 & T2 being 2 temperatures, and n from 0 to

255.

7. Measured with wiper at tap position 255, RL grounded, using test circuit.

8. tWC is the minimum cycle time to be allowed for any nonvolatile write by the user, unless Acknowledge Polling is used. It is the time from a valid

STOP condition at the end of a write sequence of a 2-wire interface write operation, or from the rising edge of CS of a valid “Store” operation of

the Up/Down interface, to the end of the self-timed internal nonvolatile write cycle.

9. The recommended power up sequence is to apply VCC/VSS first, then the potentiometer voltages. During power up, the data sheet parameters

for the DCP do not fully apply until tD after VCC reaches its final value. In order to prevent unwanted tap position changes, or an inadvertant

store, bring the CS pin high before or concurrently with the VCC pin on power up.

CS

SCL

U/D

RW

tCI

tIL

tIH

tCYC

tID

tDI

tIW

MI

(3)

tIC

tCPHS

tF

tR

10%

90%

tCPHNS

DS0, DS1

High-Voltage Write Cycle Timing

SYMBOL

PARAMETER

TYP

MAX

UNITS

tWC

(Notes 5, 8)

Non-volatile write cycle time

5

10

ms

XDCP Timing

SYMBOL

PARAMETER

MIN

MAX

UNITS

tWRL (Note 5) SCL rising edge to wiper code changed, wiper response time after instruction

issued (all load instructions)

520

s

X9252

相关PDF资料 |

PDF描述 |

|---|---|

| VE-B30-MV | CONVERTER MOD DC/DC 5V 150W |

| VE-J5K-MZ | CONVERTER MOD DC/DC 40V 25W |

| VI-J2Y-MZ | CONVERTER MOD DC/DC 3.3V 16.5W |

| MS3124E12-8PW | CONN RCPT 8POS JAM NUT W/PINS |

| VE-J5H-MZ | CONVERTER MOD DC/DC 52V 25W |

相关代理商/技术参数 |

参数描述 |

|---|---|

| X9258 | 制造商:INTERSIL 制造商全称:Intersil Corporation 功能描述:Low Noise/Low Power/2-Wire Bus/256 Taps |

| X9258)06 | 制造商:INTERSIL 制造商全称:Intersil Corporation 功能描述:Quad Digital Controlled Potentiometers |

| X9258_11 | 制造商:INTERSIL 制造商全称:Intersil Corporation 功能描述:Quad Digital Controlled Potentiometers(XDCP?) |

| X9258_13 | 制造商:INTERSIL 制造商全称:Intersil Corporation 功能描述:Low Noise/Low Power/2-Wire Bus/256 Taps |

| X9258TB24 | 制造商:XICOR 制造商全称:Xicor Inc. 功能描述:Quad Digital Controlled Potentiometers (XDCP) |

发布紧急采购,3分钟左右您将得到回复。