参数资料

| 型号: | XA3S1200E-4FGG400I |

| 厂商: | Xilinx Inc |

| 文件页数: | 15/37页 |

| 文件大小: | 0K |

| 描述: | IC FPGA SPARTAN-3E 1200K 400-FBG |

| 标准包装: | 60 |

| 系列: | Spartan®-3E XA |

| LAB/CLB数: | 8672 |

| 逻辑元件/单元数: | 19512 |

| RAM 位总计: | 516096 |

| 输入/输出数: | 304 |

| 门数: | 1200000 |

| 电源电压: | 1.14 V ~ 1.26 V |

| 安装类型: | 表面贴装 |

| 工作温度: | -40°C ~ 100°C |

| 封装/外壳: | 400-BGA |

| 供应商设备封装: | 400-FBGA(21x21) |

第1页第2页第3页第4页第5页第6页第7页第8页第9页第10页第11页第12页第13页第14页当前第15页第16页第17页第18页第19页第20页第21页第22页第23页第24页第25页第26页第27页第28页第29页第30页第31页第32页第33页第34页第35页第36页第37页

DS635 (v2.0) September 9, 2009

Product Specification

22

R

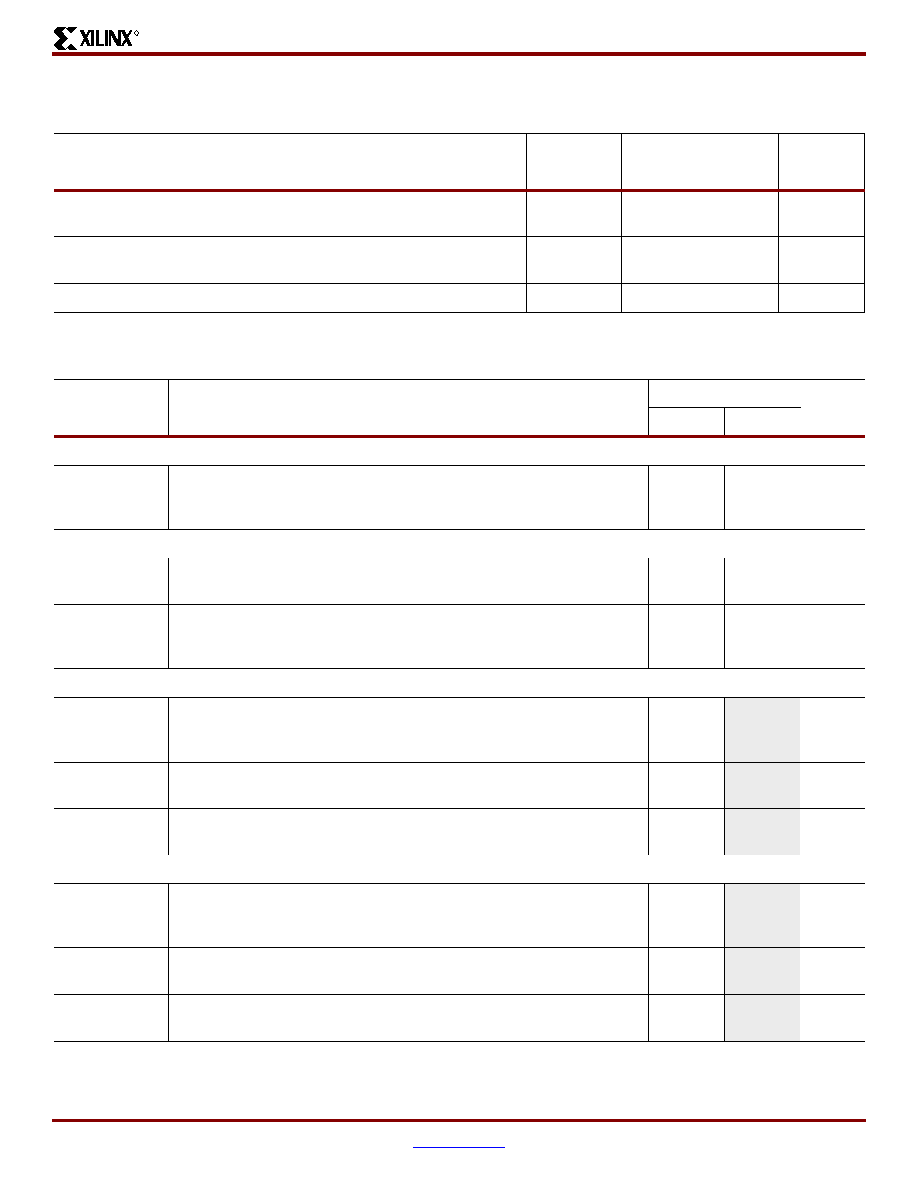

Clock Buffer/Multiplexer Switching Characteristics

18 x 18 Embedded Multiplier Timing

Table 23: Clock Distribution Switching Characteristics

Description

Symbol

Maximum

Units

-4 Speed Grade

Global clock buffer (BUFG, BUFGMUX, BUFGCE) I input to O-output

delay

TGIO

1.46

ns

Global clock multiplexer (BUFGMUX) select S-input setup to I0 and I1

inputs. Same as BUFGCE enable CE-input

TGSI

0.63

ns

Frequency of signals distributed on global buffers (all sides)

FBUFG

311

MHz

Table 24: 18 x 18 Embedded Multiplier Timing

Symbol

Description

-4 Speed Grade

Units

Min

Max

Combinatorial Delay

TMULT

Combinatorial multiplier propagation delay from the A and B inputs to

the P outputs, assuming 18-bit inputs and a 36-bit product (AREG,

BREG, and PREG registers unused)

-4.88(1)

ns

Clock-to-Output Times

TMSCKP_P

Clock-to-output delay from the active transition of the CLK input to valid

data appearing on the P outputs when using the PREG register(2)

-1.10

ns

TMSCKP_A

TMSCKP_B

Clock-to-output delay from the active transition of the CLK input to valid

data appearing on the P outputs when using either the AREG or BREG

register(3)

-4.97

ns

Setup Times

TMSDCK_P

Data setup time at the A or B input before the active transition at the

CLK when using only the PREG output register (AREG, BREG

registers unused)(2)

3.98

-ns

TMSDCK_A

Data setup time at the A input before the active transition at the CLK

when using the AREG input register(3)

0.23

-ns

TMSDCK_B

Data setup time at the B input before the active transition at the CLK

when using the BREG input register(3)

0.39

-ns

Hold Times

TMSCKD_P

Data hold time at the A or B input before the active transition at the CLK

when using only the PREG output register (AREG, BREG registers

unused)(2)

-0.97

TMSCKD_A

Data hold time at the A input before the active transition at the CLK

when using the AREG input register(3)

0.04

TMSCKD_B

Data hold time at the B input before the active transition at the CLK

when using the BREG input register(3)

0.05

相关PDF资料 |

PDF描述 |

|---|---|

| 93C86BT-E/ST | IC EEPROM 16KBIT 1024X16 8-TSSOP |

| 93C86BT-E/MS | IC EEPROM 16KBIT 1024X16 8-MSOP |

| 93C86B-E/ST | IC EEPROM 16KBIT 1024X16 8-TSSOP |

| 93C86B-E/MS | IC EEPROM 16KBIT 1024X16 8-MSOP |

| XC3SD3400A-4CS484C | SPARTAN-3ADSP FPGA 3400K 484CSA |

相关代理商/技术参数 |

参数描述 |

|---|---|

| XA3S1200E-4FGG400Q | 功能描述:IC FPGA SPARTAN-3E 1200K 400-FBG RoHS:是 类别:集成电路 (IC) >> 嵌入式 - FPGA(现场可编程门阵列) 系列:Spartan®-3E XA 标准包装:40 系列:Spartan® 6 LX LAB/CLB数:3411 逻辑元件/单元数:43661 RAM 位总计:2138112 输入/输出数:358 门数:- 电源电压:1.14 V ~ 1.26 V 安装类型:表面贴装 工作温度:-40°C ~ 100°C 封装/外壳:676-BGA 供应商设备封装:676-FBGA(27x27) |

| XA3S1200E-4FTG256I | 功能描述:IC FPGA SPARTAN3E 1200K 256FTBGA RoHS:是 类别:集成电路 (IC) >> 嵌入式 - FPGA(现场可编程门阵列) 系列:Spartan®-3E XA 标准包装:40 系列:Spartan® 6 LX LAB/CLB数:3411 逻辑元件/单元数:43661 RAM 位总计:2138112 输入/输出数:358 门数:- 电源电压:1.14 V ~ 1.26 V 安装类型:表面贴装 工作温度:-40°C ~ 100°C 封装/外壳:676-BGA 供应商设备封装:676-FBGA(27x27) |

| XA3S1200E-4FTG256Q | 功能描述:IC FPGA SPARTAN3E 1200K 256FTBGA RoHS:是 类别:集成电路 (IC) >> 嵌入式 - FPGA(现场可编程门阵列) 系列:Spartan®-3E XA 标准包装:40 系列:Spartan® 6 LX LAB/CLB数:3411 逻辑元件/单元数:43661 RAM 位总计:2138112 输入/输出数:358 门数:- 电源电压:1.14 V ~ 1.26 V 安装类型:表面贴装 工作温度:-40°C ~ 100°C 封装/外壳:676-BGA 供应商设备封装:676-FBGA(27x27) |

| XA3S1400A | 制造商:XILINX 制造商全称:XILINX 功能描述:XA Spartan-3A Automotive FPGA Family Data Sheet |

| XA3S1400A-4FGG484I | 功能描述:IC FPGA SPARTAN3A 1400K 484-FBGA RoHS:是 类别:集成电路 (IC) >> 嵌入式 - FPGA(现场可编程门阵列) 系列:Spartan®-3A XA 产品变化通告:Step Intro and Pkg Change 11/March/2008 标准包装:1 系列:Virtex®-5 SXT LAB/CLB数:4080 逻辑元件/单元数:52224 RAM 位总计:4866048 输入/输出数:480 门数:- 电源电压:0.95 V ~ 1.05 V 安装类型:表面贴装 工作温度:-40°C ~ 100°C 封装/外壳:1136-BBGA,FCBGA 供应商设备封装:1136-FCBGA 配用:568-5088-ND - BOARD DEMO DAC1408D750122-1796-ND - EVALUATION PLATFORM VIRTEX-5 |

发布紧急采购,3分钟左右您将得到回复。