- 您现在的位置:买卖IC网 > PDF目录225572 > XC4VFX100-11FFG1517I (XILINX INC) FPGA, 10544 CLBS, 1181 MHz, PBGA1517 PDF资料下载

参数资料

| 型号: | XC4VFX100-11FFG1517I |

| 厂商: | XILINX INC |

| 元件分类: | FPGA |

| 英文描述: | FPGA, 10544 CLBS, 1181 MHz, PBGA1517 |

| 封装: | LEAD FREE, FBGA-1517 |

| 文件页数: | 21/58页 |

| 文件大小: | 1863K |

| 代理商: | XC4VFX100-11FFG1517I |

第1页第2页第3页第4页第5页第6页第7页第8页第9页第10页第11页第12页第13页第14页第15页第16页第17页第18页第19页第20页当前第21页第22页第23页第24页第25页第26页第27页第28页第29页第30页第31页第32页第33页第34页第35页第36页第37页第38页第39页第40页第41页第42页第43页第44页第45页第46页第47页第48页第49页第50页第51页第52页第53页第54页第55页第56页第57页第58页

Virtex-4 FPGA Data Sheet: DC and Switching Characteristics

DS302 (v3.7) September 9, 2009

Product Specification

28

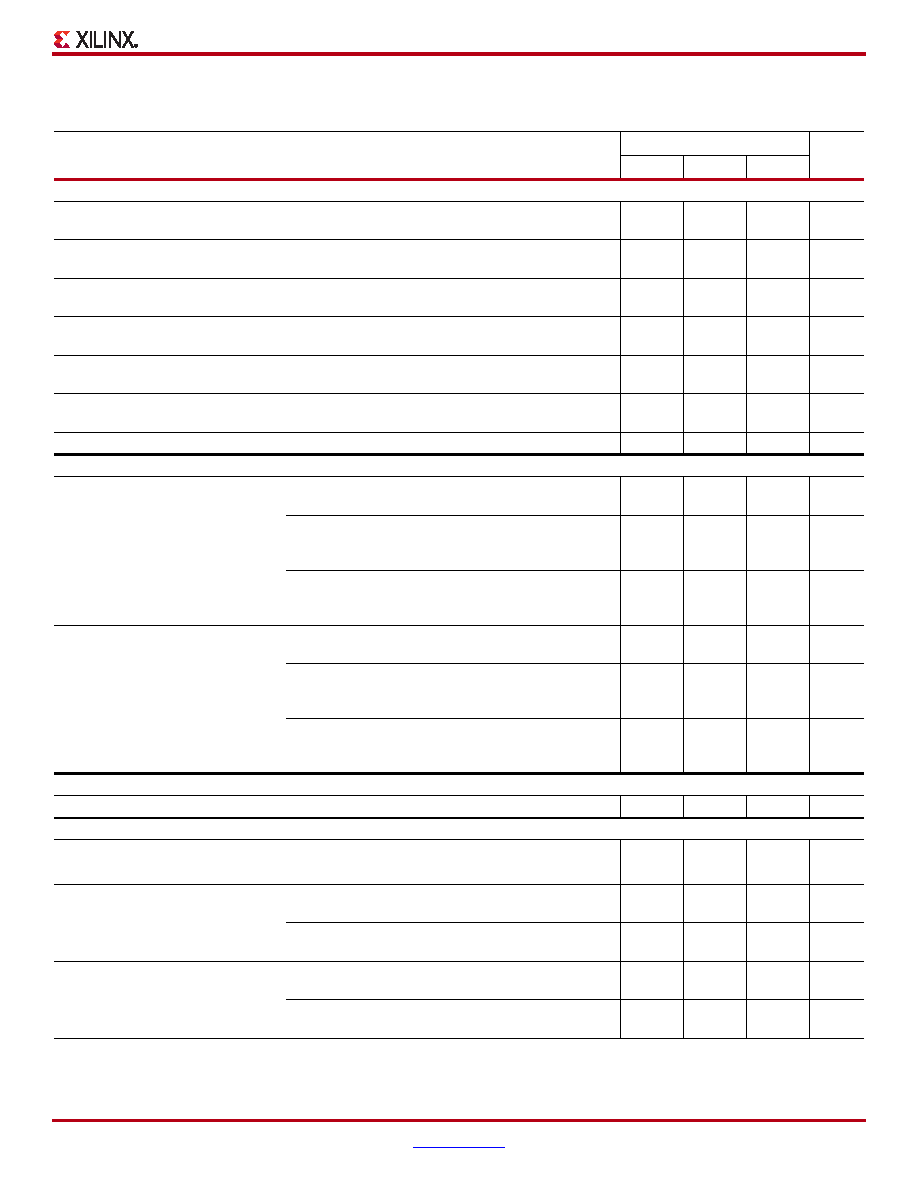

Input Serializer/Deserializer Switching Characteristics

Table 34: ISERDES Switching Characteristics

Symbol

Description

Speed Grade

Units

-12

-11

-10

Setup/Hold for Control Lines

TISCCK_BITSLIP / TISCKC_BITSLIP

BITSLIP pin Setup/Hold with respect to CLKDIV

0.28

–0.20

0.34

–0.16

0.40

–0.13

ns

TISCCK_CE / TISCKC_CE(2)

CE pin Setup/Hold with respect to CLK (for CE1)

0.48

–0.37

0.57

–0.30

0.69

–0.25

ns

TISCCK_CE2 / TISCKC_CE2(2)

CE pin Setup/Hold with respect to CLKDIV (for CE2)

0.11

–0.04

0.14

–0.03

0.16

–0.02

ns

TISCCK_DLYCE / TISCKC_DLYCE

DLYCE pin Setup/Hold with respect to CLKDIV

0.16

0.11

0.19

0.13

0.23

0.16

ns

TISCCK_DLYINC / TISCKC_DLYINC

DLYINC pin Setup/Hold with respect to CLKDIV

0.01

0.36

0.01

0.43

0.01

0.51

ns

TISCCK_DLYRST / TISCKC_DLYRST

DLYRST pin Setup/Hold with respect to CLKDIV

–0.03

0.37

–0.02

0.45

–0.02

0.54

ns

TISCCK_SR

SR pin Setup with respect to CLKDIV

0.64

0.77

0.92

ns

Setup/Hold for Data Lines

TISDCK_D / TISCKD_D

D pin Setup/Hold with respect to CLK

(IOBDELAY = IBUF or NONE)

0.24

–0.11

0.28

–0.11

0.34

–0.11

ns

D pin Setup/Hold with respect to CLK

(IOBDELAY = IFD or BOTH,

IOBDELAY_TYPE = DEFAULT)

6.64

–6.51

7.63

–6.51

8.84

–6.51

ns

D pin Setup/Hold with respect to CLK(1)

(IOBDELAY = IFD or BOTH,

IOBDELAY_TYPE = FIXED, IOBDELAY_VALUE = 0)

0.81

–0.68

0.87

–0.68

1.08

–0.68

ns

TISDCK_DDR / TISCKD_DDR

D pin Setup/Hold with respect to CLK at DDR mode

(IOBDELAY = IBUF or NONE)

0.24

–0.11

0.28

–0.11

0.34

–0.11

ns

D pin Setup/Hold with respect to CLK at DDR mode

(IOBDELAY = IFD or BOTH,

IOBDELAY_TYPE = DEFAULT)

6.64

–6.51

7.63

–6.51

8.84

–6.51

ns

D pin Setup/Hold with respect to CLK at DDR mode(1)

(IOBDELAY = IFD or BOTH,

IOBDELAY_TYPE = FIXED, IOBDELAY_VALUE = 0)

0.81

–0.68

0.87

–0.68

1.08

–0.68

ns

Sequential Delays

TISCKO_Q

CLKDIV to out at Q pin

0.59

0.71

0.85

ns

Propagation Delays

TISDO_DO_IOBDELAY_IFD

D input to DO output pin (IOBDELAY = IFD)

0.17

0.20

0.24

ns

TISDO_DO_IOBDELAY_NONE

D input to DO output pin (IOBDELAY = NONE)

0.17

0.20

0.24

ns

TISDO_DO_IOBDELAY_BOTH

D input to DO output pin (IOBDELAY = BOTH,

IOBDELAY_TYPE = DEFAULT)

6.00

6.91

7.96

ns

D input to DO output pin(1) (IOBDELAY = BOTH,

IOBDELAY_TYPE = FIXED, IOBDELAY_VALUE = 0)

0.74

0.79

0.99

ns

TISDO_DO_IOBDELAY_IBUF

D input to DO output pin (IOBDELAY = IBUF,

IOBDELAY_TYPE = DEFAULT)

6.00

6.91

7.96

ns

D input to DO output pin(1) (IOBDELAY = IBUF,

IOBDELAY_TYPE = FIXED, IOBDELAY_VALUE = 0)

0.74

0.79

0.99

ns

Notes:

1.

Recorded at 0 tap value. Refer to Timing Report for other values.

2.

TISCCK_CE2 and TISCKC_CE2 are reported as TISCCK_CE / TISCKC_CE in TRCE report.

相关PDF资料 |

PDF描述 |

|---|---|

| XC4VFX100-12FFG1152C | FPGA, 10544 CLBS, 1181 MHz, PBGA1152 |

| XC4VFX100-12FFG1517C | FPGA, 10544 CLBS, 1181 MHz, PBGA1517 |

| XC5206-3PCG84I | FPGA, 196 CLBS, 6000 GATES, 83 MHz, PQCC84 |

| XC5206-3PQG100I | FPGA, 196 CLBS, 6000 GATES, 83 MHz, PQFP100 |

| XC5206-3PQG160I | FPGA, 196 CLBS, 6000 GATES, 83 MHz, PQFP160 |

相关代理商/技术参数 |

参数描述 |

|---|---|

| XC4VFX100-12FF1152C | 制造商:Xilinx 功能描述: |

| XC4VFX100-12FF1517C | 制造商:Xilinx 功能描述: |

| XC4VFX100-12FFG1152C | 功能描述:IC FPGA VIRTEX-4FX 100K 1152FBGA RoHS:是 类别:集成电路 (IC) >> 嵌入式 - FPGA(现场可编程门阵列) 系列:Virtex®-4 FX 产品变化通告:XC4000(E,L) Discontinuation 01/April/2002 标准包装:24 系列:XC4000E/X LAB/CLB数:100 逻辑元件/单元数:238 RAM 位总计:3200 输入/输出数:80 门数:3000 电源电压:4.5 V ~ 5.5 V 安装类型:表面贴装 工作温度:-40°C ~ 100°C 封装/外壳:120-BCBGA 供应商设备封装:120-CPGA(34.55x34.55) |

| XC4VFX100-12FFG1152CES | 制造商:Xilinx 功能描述: |

| XC4VFX100-12FFG1517C | 功能描述:IC FPGA VIRTEX-4FX 100K 1517FBGA RoHS:是 类别:集成电路 (IC) >> 嵌入式 - FPGA(现场可编程门阵列) 系列:Virtex®-4 FX 产品变化通告:XC4000(E,L) Discontinuation 01/April/2002 标准包装:24 系列:XC4000E/X LAB/CLB数:100 逻辑元件/单元数:238 RAM 位总计:3200 输入/输出数:80 门数:3000 电源电压:4.5 V ~ 5.5 V 安装类型:表面贴装 工作温度:-40°C ~ 100°C 封装/外壳:120-BCBGA 供应商设备封装:120-CPGA(34.55x34.55) |

发布紧急采购,3分钟左右您将得到回复。