- 您现在的位置:买卖IC网 > PDF目录205935 > XC5204-6TQ144C (XILINX INC) Field Programmable Gate Arrays PDF资料下载

参数资料

| 型号: | XC5204-6TQ144C |

| 厂商: | XILINX INC |

| 元件分类: | FPGA |

| 英文描述: | Field Programmable Gate Arrays |

| 中文描述: | FPGA, 120 CLBS, 4000 GATES, 83 MHz, PQFP144 |

| 封装: | PLASTIC, TQFP-144 |

| 文件页数: | 24/73页 |

| 文件大小: | 598K |

| 代理商: | XC5204-6TQ144C |

第1页第2页第3页第4页第5页第6页第7页第8页第9页第10页第11页第12页第13页第14页第15页第16页第17页第18页第19页第20页第21页第22页第23页当前第24页第25页第26页第27页第28页第29页第30页第31页第32页第33页第34页第35页第36页第37页第38页第39页第40页第41页第42页第43页第44页第45页第46页第47页第48页第49页第50页第51页第52页第53页第54页第55页第56页第57页第58页第59页第60页第61页第62页第63页第64页第65页第66页第67页第68页第69页第70页第71页第72页第73页

R

XC5200 Series Field Programmable Gate Arrays

7-112

November 5, 1998 (Version 5.2)

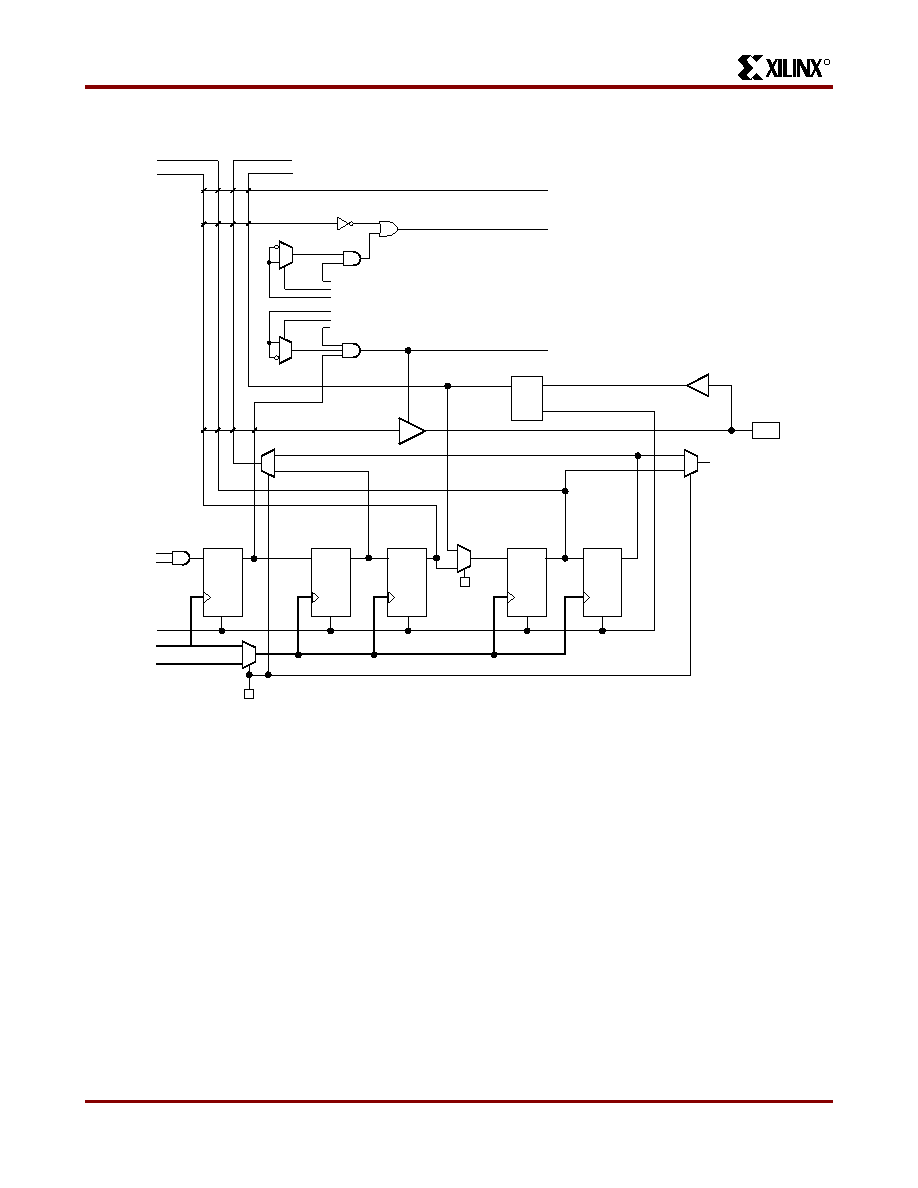

DONE High to active user I/O is controlled by an option to

the bitstream generation software.

Release of Global Reset After DONE Goes High

By default, Global Reset (GR) is released two CCLK cycles

after the DONE pin goes High. If CCLK is not clocked twice

after DONE goes High, all flip-flops are held in their initial

reset state. The delay from DONE High to GR inactive is

controlled by an option to the bitstream generation soft-

ware.

Configuration Complete After DONE Goes High

Three full CCLK cycles are required after the DONE pin

goes High, as shown in Figure 25 on page 109. If CCLK is

not clocked three times after DONE goes High, readback

cannot be initiated and most boundary scan instructions

cannot be used.

Configuration Through the Boundary Scan

Pins

XC5200-Series devices can be configured through the

boundary scan pins.

For detailed information, refer to the Xilinx application note

XAPP017, “

Boundary Scan in XC4000 and XC5200

Devices.”

Readback

The user can read back the content of configuration mem-

ory and the level of certain internal nodes without interfer-

ing with the normal operation of the device.

Readback not only reports the downloaded configuration

bits, but can also include the present state of the device,

represented by the content of all flip-flops and latches in

CLBs.

DONE

*

**

QS

R

1

0

1

0

1

0

1

0

1

GR ENABLE

GR INVERT

STARTUP.GR

STARTUP.GTS

GTS INVERT

GTS ENABLE

CONTROLLED BY STARTUP SYMBOL

IN THE USER SCHEMATIC (SEE

LIBRARIES GUIDE)

GLOBAL RESET OF

ALL CLB FLIP-FLOPS/LATCHES

IOBs OPERATIONAL PER CONFIGURATION

GLOBAL 3-STATE OF ALL IOBs

Q2

Q3

Q1/Q4

DONE

IN

STARTUP

Q0

Q1

Q2

Q3

Q4

M

" FINISHED "

ENABLES BOUNDARY

SCAN, READBACK AND

CONTROLS THE OSCILLATOR

K

SQ

K

DQ

K

DQ

K

DQ

K

DQ

FULL

LENGTH COUNT

CLEAR MEMORY

CCLK

STARTUP.CLK

USER NET

CONFIGURATION BIT OPTIONS SELECTED BY USER

X9002

Figure 26: Start-up Logic

相关PDF资料 |

PDF描述 |

|---|---|

| XC5206-3BG225C | Field Programmable Gate Arrays |

| XC5206-3BG352C | Field Programmable Gate Arrays |

| XC5206-3HQ208C | Field Programmable Gate Arrays |

| XC5206-3HQ240C | Field Programmable Gate Arrays |

| XC5206-3PG156C | Field Programmable Gate Arrays |

相关代理商/技术参数 |

参数描述 |

|---|---|

| XC5204-6TQ144I | 制造商:Xilinx 功能描述: |

| XC5204-6TQ176C | 制造商:XILINX 制造商全称:XILINX 功能描述:Field Programmable Gate Arrays |

| XC5204-6VQ100C | 功能描述:IC FPGA 120 CLB'S 100-VQFP RoHS:否 类别:集成电路 (IC) >> 嵌入式 - FPGA(现场可编程门阵列) 系列:XC5200 产品变化通告:XC4000(E,L) Discontinuation 01/April/2002 标准包装:24 系列:XC4000E/X LAB/CLB数:100 逻辑元件/单元数:238 RAM 位总计:3200 输入/输出数:80 门数:3000 电源电压:4.5 V ~ 5.5 V 安装类型:表面贴装 工作温度:-40°C ~ 100°C 封装/外壳:120-BCBGA 供应商设备封装:120-CPGA(34.55x34.55) |

| XC5204-6VQ100I | 制造商:Xilinx 功能描述: |

| XC5204-6VQ64C | 制造商:XILINX 制造商全称:XILINX 功能描述:Field Programmable Gate Arrays |

发布紧急采购,3分钟左右您将得到回复。